第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編):FPGA Insights

産業機器業界では、産業用イーサネットの普及や機能安全規格への対応など、大きな市場の変化がある。こうしたトレンドに対応しつつ、企業の収益性をさらに高めていく手法の1つとして、TCO(Total Cost of Ownership:設計資産保有の総コスト)を考慮した製品開発が注目を集めている。今回より、産業機器におけるTCOの重要性や、TCOの削減に向けたFPGAの応用事例などを前編と後編の2回に分けて解説する。

電子/電気機器の開発において、コストを削減しながら、変化し続ける顧客のニーズや各種の規格に対応する設計を迅速に行い、新製品をできるだけ早く市場に投入していくという課題は、民生電子機器だけに当てはまることではない。一般的に、一度開発したら10年あるいはそれ以上の製品寿命があるといわれてきた産業機器でも、通信/ネットワーク技術や半導体技術の進歩、国や地域ごとに定められた規格への対応が必要となり、製品のアップグレードや機能追加などへの迅速な対応が強く求められている。

産業機器業界では、以下に挙げる大きな市場の変化がある。こうした業界の動きに対応しつつ、企業の収益性をさらに高めていく手法の1つとして、TCO(Total Cost of Ownership:設計資産保有の総コスト)を考慮した製品開発が注目を集めている。TCOは、製品のライフ・サイクルにかかる全コストの総量である。TCOの削減は、収益性の高い産業機器製品を生み出し、製品の競争力を維持するために、あらゆる企業がこの概念を理解し、今後取り組まなければならない共通課題の1つとなってきた。

産業機器における 3つのトレンド

産業機器市場で大きなトレンドが3つある。その1つは、産業用イーサネットの普及である。前回の「FPGAで実現する産業用ワイヤレスセンサーネットワーク」でも述べたが、産業機器ユーザーは現在、産業用ネットワークの一部を「Fieldbus」 ベースからイーサネット ・ベースへと移行している。しかし、ここで課題となるのが産業用ネットワークには、いくつものプロトコル規格が存在していることである。

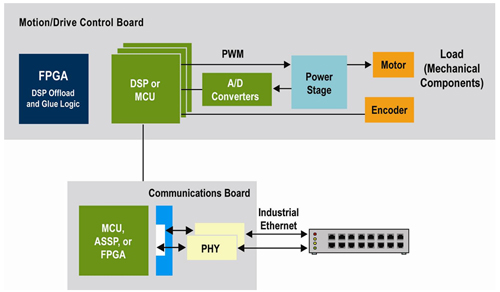

産業用イーサネットに対応する機器を開発する際に、MCU(マイコン) や ASSP などハードウエアが固定された半導体チップを使った場合、複数のプロトコルに対応しようとすると、コストの上昇を招くことがある(図1)。これに対して、FPGAなどのプログラマブル・デバイスは、複数ある産業用イーサネット・プロトコル規格に対応する場合でも、主な機能をワンチップにできることやハードウエアによる並列処理が可能なことから、外付け部品や回路基板の数を少なくすることができる。このため、開発サイクルの短縮とコストの削減が可能となる。

2つ目は、主要工場における消費エネルギーの削減と、それによるコスト低減への取り組みだ。全世界の総発電量の約 50% を電気モーターが消費しているといわれている。しかもエネルギー消費を抑えるように制御されているモーターは、全モーター数のわずか 5% にとどまっている。こうした状況下で、主な工場ではエネルギー効率と位置決め精度をより高めたモーター・ドライブ・システムを導入する機運が高まっている。

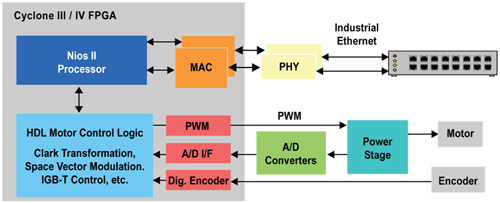

エネルギー効率を高める手段の1つとして、FPGAを使ったモーター・コントロール・システムが注目を集めている。FPGA を用いることで、FOC (Field Oriented Control)アルゴリズムなどの演算を内部のハードウエアで高速処理できる。また、FPGAはエンベデッド・プロセッサ、産業用イーサネット・インタフェース、デジタル・エンコーダなどの機能ブロック、およびカスタム・ロジックをワンチップに集積することができることも設計者にはすでに認識されている。とりわけ欧米ではFPGAへの機能集約に積極的だ。FPGA は、こうした特徴を生かすことで、性能の向上と先進的な機能をもたらすほか、部品と基板再設計を減らしてコスト削減を実現することができる。

3つ目は、国際電気標準会議の規格「IEC 61508」(電気・電子・プログラマブル電子安全関連系の機能安全)などへの対応がある。「IEC 61508 」や関連する安全規格は、欧州に加え米国や日本など他の地域でも適用されている。また、欧州ではIEC 61508を欧州機械指令「 2006/42/EG 」と書き換えた。この機器安全規格に適合するまで、欧州の供給者には 2 年間の猶予があるものの、多くの機器メーカーはこれらの安全要件に適合する準備が遅れているようだ。機能安全規格に準拠した機器を設計しようとすると、開発がより複雑となり、安全設計と認証のために必要な開発期間が延びて、市場への製品投入が遅れる可能性がある。

TCOを考慮した柔軟なシステム設計

TCO は一般に、製品やシステムの直接コストと間接コストを決定するための財務的な評価項目であると定義されている。 TCO は、長期的な収益状況を明らかにし、関連するシステム・コストを含む、あらゆるプロジェクトとプロセスにわたる企業の総資産コストに対処することで、長期的な収益評価基準を提供してくれる。

新製品の開発に要する時間は年々増大している。例えば、組み込み用のソフトウエアは大規模化し、複数のグループに分けて開発が行われるようになった。そして、各グループが開発したモジュールを最終的に一本化している。しかし、ソフトウエアを合体した時に整合性が取れないこともある。その結果、製品の開発スケジュールに大幅な遅延が生じてしまう可能性がある。このため、経営者やマネジメント層からは「コストアップ要因になりかねない複雑な開発作業をできるだけ単純化したい」という要求が増えている。

TCOを考慮した柔軟なシステム設計を取り入れていかないと、製品出荷の後のメンテナンスや改良、シリーズ展開を図る時に、同じ開発プロセスを繰り返し行うことになりかねない。

ソフトウエア変更で新機能に対応

システム開発を行う場合、従来はプロセッサやDSP、メモリなど、いくつかの必要な個別部品を回路基板上に並べて実装していた。そのシステム(電子回路)をできるだけコンパクトなサイズにまとめるため、回路基板のレイアウトを出来る限り小さくするなどの工夫を行っていた。

最近は開発に対するエンジニアの考え方が少し変わってきたようだ。実装したハードウエア(部品や基板)を変えずに、ソフトウエアを変更することで、新しい機能にも対応していくという動きにある。

日本ではこの10年〜20年間は必要な機能をASICやASSPで開発し、設計資産をハードウエアで残してきた。今後は、ハードウエアだけでなく、ソフトウエア資産(ファンクション)も取り入れた、ハードウエアとソフトウエアの融合がTCO削減には重要となる。

微細化が進んだことで、ASICの設計/開発費は高騰し、プロトタイプのASICを作成するまでに1年〜2年の開発期間を要することがある。設計を少し変更しようと思っても、開発の期間とコストを考えると、その作業は大変である。これに対して、FPGAはソフトウエアの機能をアップグレードすることで、従来のハードウエア(プリント基板や電子部品)をそのまま活用することができる。まさに、回路設計者はその目的に応じて発想の転換が必要だ。

FPGAによるTCO削減の一例として、アルテラ社のFPGAを取り上げる。産業用途向けのソリューション・ポートフォリオには、FPGA、デザイン・ソフトウエア、IP(intellectual property)コアが含まれている。必要な機能をワンチップにインテグレーションが可能なFPGA を使用すると、以下のようにTCO を削減することができる(図2)。

- 外部にICチップを追加することなく、ハードウエアの性能を高速化しソフトウエアを効果的に活用

- 柔軟な FPGA プラットフォーム だけで、追加ボードをデザインすることなく、変化し続ける機能やプロトコルに対応

- すべてのシステム機能を 1個の FPGA に統合することで、信頼性を高め、製造および保守コストを削減

- 同じ FPGA デザインを使用して複数の製品を展開し、市場投入までの期間を短縮

- FPGA の長いライフ・サイクルを利用して製造中止のリスクを抑え、交換コストを削減

前編では産業機器市場におけるトレンドやTCO削減の重要性などについて述べてきた。後編では、業界のトレンドに対するFPGAの応用事例などを解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●産業用アプリケーションにおける、設計資産保有の総コストの削減

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.