第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜:FPGA Insights

FPGAの設計開発フローの中で、「これさえ知っていればFPGAの設計ができる」という4つの基本ステップをこれまで、4回にわたって取り上げ、一歩ずつ解説してきた。今回からは、FPGAなどのICチップが実装されたプリント基板を用い、より実践的な「ボードを使った回路設計」についてわかりやすく解説する。その具体的な事例として「DDR2 SDRAMインタフェース」を設計してみる。最新のFPGA設計ツールとIPコアを活用することで、FPGAの設計が比較的容易であることを実感していただきたい。

FPGA を用いた DDR2 SDRAMインタフェース

今日、組み込みシステムに搭載されるマイクロコントローラの処理性能が格段に向上している。このため、CPUとメモリ間のデータ転送を高速に行うためのメモリ・インタフェースが、パソコン以外の用途でも爆発的に普及している。その1つがDDR2 SDRAMインタフェースであり、今やシステム性能を向上する上で、欠かせない存在となっている。半面、こうした高速メモリ・インタフェースを使いこなすために、配慮しなければならない課題もある。例えば、高速パラレル通信では、「信号品質」の問題や「タイミング制約」の設定などに注意する必要がある。

DDR2 SDRAMインタフェースの機能は、一般的に「ASIC」や「ASSP」、「FPGA」 を使って実現されることが多い。これらのICチップを選択する場合には、それぞれ一長一短があることを理解しておかなくてはならない。ASIC の場合は、大量生産される機器には向いているものの、ASIC の設計にミスがあった場合、想像しただけでも恐ろしくなるような開発工数とコストが発生する可能性がある。

ASSP の場合は、比較的安価に短納期で入手できるが、特定用途であるために汎用性に欠けることがある。例えば、供給する半導体メーカーの品種展開にもよるが、「ほかのメモリ・インタフェースとのブリッジ機能が内蔵されていない」など、ユーザーの仕様に『ぴったり合う製品がない』ことも少なくない。

これに対して FPGAは、コントローラからピンの配置まで、必要とする機能や性能を設計者側で決めることができるのが大きな特徴である。このため、仮にFPGA 内部のデザインに設計ミスがあった場合でも、設計者がオンボード上で再プログラミングし、必要に応じて内部の回路を書き換えることが可能である。このため、開発工数やコストの点で、ASIC とは比較にならないくらいリスクを軽減させることができる。

また、FPGAは汎用性が高い。一例だが、FPGAであればシリアルI/Oを10ポート備えることもでき、顧客のニーズにも柔軟な対応が可能である。その上、 DDR2 SDRAMインタフェース 以外の機能を FPGA に集積させることができるため、プリント基板上に実装する部品の点数を削減することにもつながる。

そこで、本稿ではDDR2 SDRAMインタフェース回路をFPGAに実装するための方法について、「トポロジー検証の段階からデバック手法まで」を2回に分けて、わかりやすく紹介する。

ボード回路の設計

ボード回路の設計を行うフローでは、回路図を入力する前に、まず DDR2 SDRAMインタフェース信号のトポロジー(接続形態)を検討する必要がある。そこで本項では、1つのFPGAに2つの DDR2 SDRAMチップを接続する場合のトポロジーについて、実例を交えて紹介する。接続するDDR2 SDRAMチップ数が増えれば、それだけ分岐する数も増えることになる。

今回紹介する事例では、DDR2 SDRAMインタフェース信号を「Address/Command Group」、「DATA Group」、「Clock Group」 と3つのグループに分け、グループごとに以下のようなトポロジーにすることを決めた。また、全ての DDR2 SDRAMインタフェースの信号配線は等長とし、各終端抵抗、ダンピング抵抗はできる限りピンの直近に設置するものとした。

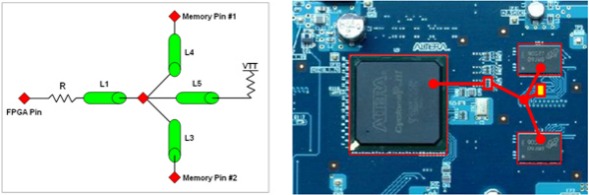

まずAddress/Command Group について説明する。Address/Command Group は、FPGA からの出力信号でI/O 規格が 「SSTL18-Class I 」となる。FPGA の送信端側にダンピング抵抗を設置し、DDR2 SDRAMチップの受信端側には Fly-By 終端抵抗を設置する。ここでは、FPGA の送信端側のダンピング抵抗を、 FPGAの内部抵抗 (On-Chip- Termination)に置き換えることも可能である。また、1つの FPAG に対して、DDR2 SDRAM チップを複数接続する場合 Address/Command Groupは基板上でスタービアを用い信号を分岐する。図1は、外部にダンピング抵抗を置き DDR2 SDRAM を2つ搭載した場合のAddress/Command Groupにおけるトポロジーのイメージ図である。

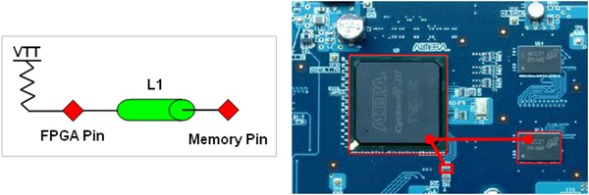

次に、DATA Group について説明する。DATA Group は双方向の信号になり、I/O 規格も 「SSTL18-Class II 」となる。双方向信号となるので FPGA、SDRAM 両側にそれぞれ Fly-By 終端抵抗が必要である。ただし、DDR2 SDRAMチップ 側の Fly-By 終端抵抗は、DDR2 SDRAMチップ の内部抵抗と置き換えることができる。図2は、DDR2 SDRAM チップの内部抵抗を使用した場合のDATA Group におけるトポロジーのイメージ図となる。

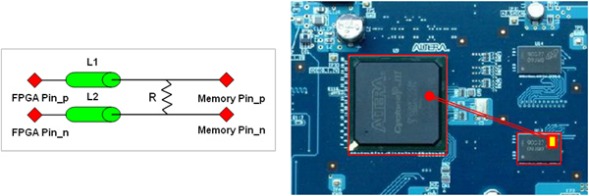

もう1つはClock Group である。Clock Group は差動信号であり、DDR2 SDRAMチップの直近に、100 Ωの差動終端抵抗が必要となる(図3)。

トポロジーが決定したら、それを元に回路の入力を行い、その次にパターン設計を行っていくこととなる。このときに『信号品質』という問題に直面する。DDR2 SDRAMインタフェースなど高速信号を取り扱うボード設計の場合、基板設計の各フェーズにおいて高速信号を考慮した設計手法を取り入れる必要がある。

一般的に高速信号では、アナログ的な動作が数々発生し、デジタル信号を中心とした過去の経験則だけでは十分に対処しきれない状況が出てくることもある。このため、高速信号を取り扱う回路設計では、事前にシミュレータを用いてトポロジーなどの検証を行うことが重要なポイントになってくる。それが結果的に設計の後戻り工数を削減することにもつながる。

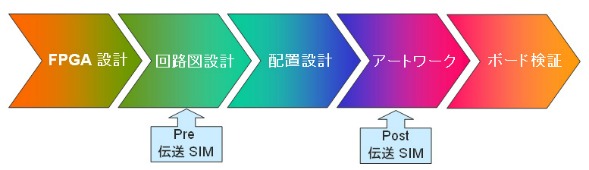

基本的に伝送シミュレーションは、図4の通り、「 Pre 」と「 Post 」で2回実施する。Preシミュレーションでは、「トポロジーの検証」、「部品配置の検証」および、「抵抗の性能見積もり」などを行うことができる。 Post シミュレーションは配置/配線の設計を行った後に、その設計が適切であるかどうかを検証するために行われる。シミュレーションの特徴は、どこの位置にでも検証用のプローブが当てられるだけではなく、抵抗値・配線長などの値をその場で自由に変更して、その場で検証することができることだ。その検証結果から得られる最適値を基に、実際の基板設計を行うことができる。

ここでは、メンター・グラフィックス社の伝送線路解析ツール「HyperLynx 」を使用し、「IBIS(I/O Buffer Information Specification)」モデル による伝送シミュレーションを行った。「Cyclone III 」用のIBISモデルは、アルテラ社のホームページからダウンロードすることができる。アルテラ社の開発ソフトウエア「Quartus II 」を利用すると、事前に設定した制約(ピン名、ピンオプションほか )が反映された、IBIS モデルを生成することが可能である。このため、ホームページからIBISモデルをダウンロードする場合に比べて、Tool 上で新たに制約条件を設定する必要がなく、開発作業を効率よく行うことができる。

なお、IBISモデルはプリント基板上の回路の動作をシステムレベルでシミュレーションするために使われることが多い。これに対して、チップ内の全トランジスタを対象として、より精度の高い動作シミュレーションを行いたい場合はSPICEモデルを適用するなど、シミュレーションの目的に応じて、そのモデルは使い分けられている。

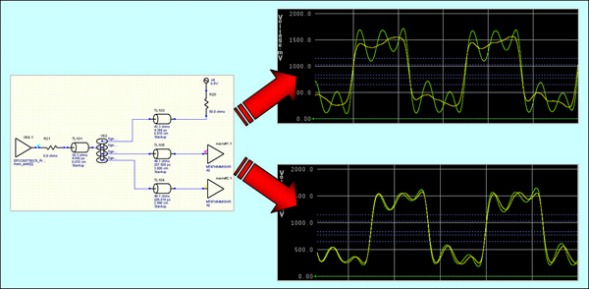

図5は、1つの FPGA で、2 つの DDR2 SDRAMチップ をサポートした時のAddress/Command Groupのシミュレーション結果である。右側の信号波形が上下で異なるのがわかる。このデータは、スタービアの分岐点から DDR2 SDRAM チップまでのそれぞれの配線長の差分が 1mm (右上) の場合と、0.5 mm(右下) の場合の結果である。この結果からわかるように、通常ではわずか0.5 mm の配線長誤差を見落としがちだが、メモリ・インタフェースの周波数が200MHzあるいはそれ以上の高速になれば、配線長のわずかなばらつきがシステムの動作に多大な影響を及ぼすことになる。実機を作成する前に伝送線路のシミュレーションを実行することで、不具合があっても早期に問題解決することが可能となる。シミュレーションでは抵抗、コンデンサ、配線長などの値をコンピュータ上で簡単に変更して、繰り返し検証することができる。このため、基板を作成し終わった後にデバックするケースと比べると、不具合などの改善に要する工数を格段に削減することができる。

図5:1つのFPGAで、2つのDDR2 SDRAMチップをサポートした時のAddress/Command Groupのシミュレーション結果(スタービアの分岐点から DDR2 SDRAM チップまでのそれぞれの配線長差分が、右上の波形は1mm、右下の波形は0.5mmの場合)

本稿では、FPGA へのDDR2 SDRAMインタフェース実装について、「ボード回路の設計」と「トポロジーの検証」について述べてきた。次回のステップ2では、FPGA用のIPコアを使ったDDR2 SDRAMインタフェースの「デザイン設計」と、その「シミュレーション」について解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.