第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜:FPGA Insights

本連載「DDR2 の実装からデバッグ手法」では、「ボードを使った回路設計」の一例として、FPGAを使った「DDR2 SDRAMインタフェース回路の設計」をテーマとして取り上げ、4回に分けて解説している。FPGAの開発ソフトウエアでサポートされている機能を使い、比較的簡単にデバッグが行える手法について、わかりやすく解説する。

これまで、FPGAの設計開発フローの中で、「これさえ知っていればFPGAの設計ができる」という4つの基本ステップを、4回にわたって連載してきた。これらの「基本ステップ」を踏まえて、現在はボードを使った回路設計の実践編「DDR2 の実装からデバッグ手法」へと進んできた。最新のFPGA開発ツールとIPコアを活用することで、FPGA を用いたDDR2 SDRAMインタフェース回路の設計が、想像していたよりも容易に行えることを実感していただけたのではないだろうか。

ただ、設計したすべてのチップが仕様通り、“一発で動作”すれば何の問題もないが、現実にはそうではない場合も起こりうるだろう。万一、回路設計者が当初に期待したように動作しない時や性能や特性マージンが十分に得られない時に、その原因を追究し、対処すべき課題を効率よく探し出すために、実機によるデバッグ作業が必要になるだろう。

本稿では、アルテラ社の開発ソフトウエア「Quartus II 」が備えているデバッグ機能を用い、比較的簡単な操作で実行できるデバッグ手法について解説する。

FPGA のデバッグ手法

DDR2 SDRAMインタフェース回路の実装において、回路設計者はプリント基板や FPGA のデザインが完了したら、実機を用いて検証作業を行う。FPGAに限らず、仕様通りに電子回路が動作しないことは、誰にも一度は経験があることであり、またデバッグ作業が、非常に骨の折れることを体験している技術者も多いのではないだろうか。特に、DDR2 SDRAM インタフェース回路のデバッグを、外付けのロジック・アナライザで行うには、IC 内部の信号を外部に取り出すための空きピンを、FPGA側に多数個用意する必要がある。しかも、どの信号(線)に不具合が生じているのかを探し出すのも非常に大変な作業である。

このようなデバッグ作業において、回路設計者の負荷を軽減することができるICチップや開発ツールが、いくつかのベンダーから提供されている。例えば、アルテラ社製 FPGA の場合、Quartus IIがサポートしているオンチップ・デバッグ機能の『SignalTap II Logic Analyzer』と『Debug GUI』を活用すれば、オンボード上で比較的簡単にデバッグすることができる。

詳細は後述するが、いずれの方法においても、複雑なデバッグを3つの作業によりで容易に実行することが可能となる。この方法により、デバッグの工数と回路設計者の労力を大幅に削減することができる。また、これらの機能を使用する上で、新たに特別なハードウエアやソフトウエアを用意する必要はない。Quartus II (ウェブ・エディションでも使用可能)を使い、JTAG(Joint Test Action Group)ポート 経由で FPGA にプログラミングできる環境が整っていればデバッグ作業が行える。

ステップ3で『SignalTap II Logic Analyzer』、ステップ4で『Debug GUI』の機能を用いたデバッグ手法を紹介する。SignalTap II Logic AnalyzerはFPGA内部のファンクション検証、Debug GUIはFPGA から DDR SDRAM Chip 間のタイミング検証に有効である。この2つの機能を組み合わせて用いることで、回路の動作に不具合が生じた場合などでも、原因の切り分け作業が容易となり、デバッグの作業効率を改善することができる。

・FPGAにロジ・アナ機能を組み込む

本稿では、SignalTap II Logic Analyzerの操作方法などについて、より詳細に解説する。本機能の概要は、Quartus IIがサポートしているデバッグ手法の一例として、「FPGAの設計開発フロー:〜ステップ4 プログラミング」の中でも簡単に紹介しているので、一読いただけるとより理解が深まることだろう。

SignalTap II Logic Analyzerの機能を一言でいうと、「ロジック・アナライザ機能をFPGA 内部に組み込む」ということである。もう少し詳しく説明すると、FPGA 内部でサンプリングした信号を FPGA 内部のメモリに蓄えておき、蓄えたサンプリング・データをJTAG ポート経由でパソコンに取り込んで信号波形を表示させる機能である。JTAGポートを利用しているため、FPGAとの接続は4本の配線で済む。もちろん、FPGAの内部信号を取り出すための余分な空きピンを用意する必要もなく、オンボード上で内部信号をサンプリングすることができる。

一般的に、FPGA内部の信号をサンプリングしようとしても、多ピンのパッケージはBGA(Ball Grid Array)が多く、外部からピンに直接コンタクトすることは難しい。このため、チェックしたい信号をすべてFPGAの空きピンを使って外部に出力し、別途用意したロジック・アナライザでタイミングの検証を行わなければならない。特に、DDR2 SDRAMインタフェースはパラレル通信のため、その数は80〜100ピンに達することもある。デバッグ作業のために、すべての信号を外部に出力するには、ボード上に膨大な数の出力ピンを準備しなければならず、そのためにボードの面積が大きくなってしまうという課題があった。

3つの作業でFPGA内部の信号を観測

SignalTap II Logic Analyzerの操作方法は非常に簡単で、以下にあげる3つの作業を行うだけでFPGA内部の信号を観測することができる。

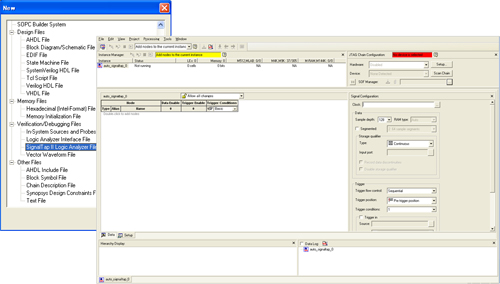

◆【作業 1】 STP ファイルの生成

Quartus II を用いて、「STP ファイル」を生成する。STP ファイルを生成するために必要な設定は、基本的にシンプルである。一般的なロジック・アナライザと同様に、GUI上でまず「サンプリング・クロック」を設定し、次に「サンプリングするノード」を選択する。それ以外でも例えば「サンプリングの深さ」や「トリガ」などを別途に設定することも可能ではあるが、シンプルな設定でよければ上記の2点を設定するだけでSTPファイルの生成を行うことができる。

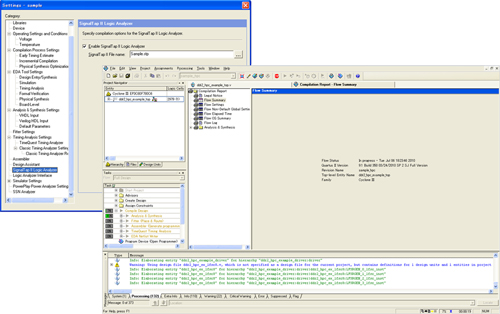

◆【作業 2】 コンパイル・プログラミング

【作業 1】で作成したSTP ファイルに対して“イネーブル”設定を行い、その上でコンパイルを実行する。コンパイルが終了した後は、FPGA にプログラミングを行う。

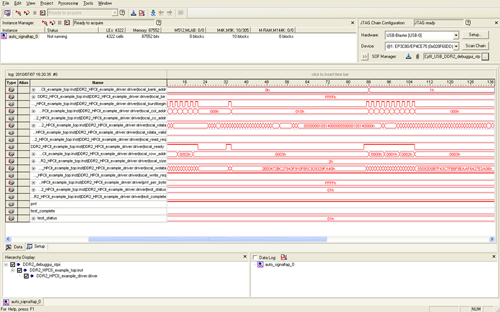

◆【作業 3】 サンプリング

上記の【作業 1】と 【作業 2】が終了すれば、FPGA内部の信号をサンプリングする準備が整ったことになり、あとは実行すればいい。

このように、SignalTap II Logic Analyzer を使用することで、オンボード上で簡単にFPGA内部の信号をサンプリングすることができる。しかし、「SignalTap II Logic Analyzer は内部ロジックを使用するため、デバッグ作業が終了した後も無駄に内部ロジックを使用してしまっているのでは」と懸念する設計者がいるかもしれないが、その点は心配ない。【作業 2】で行ったSTP ファイルの“イネーブル”設定を、デバッグが終了した後に“ディセーブル”に変更すれば、デザインに STP ファイルが反映されない。このため、デバッグ用の内部ロジックを実際のチップにそのまま埋め込むことはない。つまり、デバッグ作業中は STP ファイルを“イネーブル”にする。デバッグが終了した後に STP ファイルを“ディセーブル”にしてコンパイルを実行する。こうすれば、STP ファイルが含まれていないプログラミングファイルが完成する。このような柔軟性もFPGAの特徴の1つである。

今回のステップ3ではQuartus IIがサポートしているオンチップ・デバッグ機能の1つである「SignalTap II Logic Analyzer」について紹介した。次回のステップ4では引き続き、もう1つの「Debug GUI」を中心に、JTAGを使ったオンチップ・デバッグ機能について、わかりやすく解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●始めよう!FPGA設計:開発ソフトウエア無償版をダウンロード

●SignalTap II エンベデッド・ロジック・アナライザを使用したデザインのデバッグ

●【ビデオ】SignalTap II エンベデッド・ロジック・アナライザ

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年12月31日

Copyright © ITmedia, Inc. All Rights Reserved.