第28回 FPGAの組み込み開発最前線(前編):FPGA Insights

コンピュータやネットワークサーバー製品では、消費電力を抑えつつ、性能の向上を実現するために、プロセッサのマルチコア手法や専用ハードウエアによるデータの並列処理化が一般的に用いられている。組み込みシステムにおいても同様な傾向にある。本稿では、組み込み開発の最前線で起きている設計ニーズの変化について触れる。そして、その開発要件を満たすために有効な手段となるFPGAの機能などについて解説する。

高性能と低消費電力を両立

組み込みシステムでは、これまで性能や機能を向上させるために、動作周波数をより高くした最新のプロセッサを採用してきた。すでに動作周波数が1GHzを超えるプロセッサ/コントローラを搭載している組み込みシステムも少なくない。ところがこのような手法では、プロセッサの性能を向上させるよりも消費電力の増加率が大きくなるため、数年前から課題となっていた。近年は、組み込みシステムの開発において、機器の消費電力を抑えつつ、性能を維持、あるいは向上させていくことが、最重要事項の1つとなっている。

機器の高性能と低消費電力を両立させるためには、プロセッサ単体で高性能化を追求するよりも、マルチコア化やプロセッサとハードウエア・アクセラレータを組み合わせて並列処理した方が、その効果は大きい。さらに、マルチコアプロセッサとハードウエア・アクセラレータの技術を組み合わせるなど、さまざまなアプローチが試みられている。こうしたソリューションを提供できるICチップの1つがFPGAである。

組み込み開発にFPGAを活用するメリットとして「プロセッサとリコンフィギュラブルなアクセラレータとの組み合わせにより、柔軟なシステムを構成できる」、「プロセッサの周辺回路をFPGAに集積することでBOMコストを削減できる」などを挙げることができる。それに加えて、主要なFPGAベンダーは、FPGAに実装可能なプロセッサコアの品種拡充や、SoC設計を考慮したFPGA開発フローの整備などに取り組んでいる。

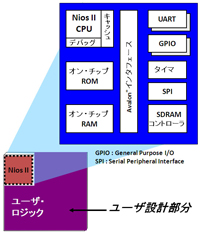

例えばアルテラでは、32ビットのソフトコア・プロセッサ「Nios II 」を提供している。このIPコアを活用してSoCを設計する利点は多い。Nios II はロイヤルティが不要で永久ライセンスとなっているため、コストダウンには有効である。性能面でも、マルチコア化が容易であり、アプリケーションに特化したカスタム命令の追加や、ハードウエアの追加が行えるなど、拡張性に優れている。しかも、Nios II は、「Stratixシリーズ」、「Arria シリーズ」、「Cycloneシリーズ」、「HardCopyシリーズ」といった同社の主要なFPGA製品でサポートされている(図1)。

FPGAに、プロセッサコアやDSP機能、大容量のメモリーIPなどを集積する手法は以前から提供されており、決して目新しい技術ではないが、ここにきて、開発コストを抑え「高性能と低消費電力の両立」を実現するための手段として、FPGAを採用する動きが加速している。

製品の仕様変更にも柔軟に対応

組み込みシステムの開発においては、搭載部品の変更、機能の追加などが繰り返し行われることが多い。その際、開発済みのASICやASSPでは期待する性能が得られなかったり、機能変更に十分対応できなかったり、消費電力が仕様を上回ったりすることがある。このような場合には、新しいICチップを再設計しなければならないケースもあり、開発コストや設計期間に影響が出てくる可能性が高い。

FPGAを用いると、このような影響を軽減できることが多い。これまでの設計資産を生かしつつ、より高性能で高機能なICチップを実現できるFPGA製品ファミリがベンダー側で用意されているからだ。例えば、アルテラの場合は、当初Cyclone II で設計に着手しても、性能や機能アップが必要であれば、Stratix II にアップグレードすることで容易に対応することができる。しかも、機器に実装するデバイスに変更が生じても、組み込んだNios II はそのまま利用できる。このため、Nios II向けに開発したデバイスドライバやミドルウエアを変更したり、修正したりする必要がない。この結果、低い設計リスクで製品のアップグレードがより短い期間で行えるため、長期的に市場で競争力を保つことができる。

FPGAを活用するメリットはほかにもある。アルテラの場合、チップのコストを抑えつつ、性能向上を図るために、搭載できるプロセッサコアを3種類用意している。高速タイプの「Nios II /f」、標準タイプの「Nios II /s」、エコノミータイプの「Nios II /e」である。より高い性能が必要であれば「高速タイプ」を用い、なおかつ実装するコア数を増やすことで設計要件に対応することが可能である。

一例だが、機能や演算性能をさほど必要としない、低コストな組込み機器向けには、低コストFPGAファミリのCyclone IVと無償で提供されている「Nios II /e」の組み合わせが良いだろう。Cyclone IVの「EP4CE22」を使用する場合、FPGAチップ全体に占めるプロセッサ部のロジック比率が3.5%以下/個となり、最小コストのプロセッサ・システムを構築する事が出来る。

より高い演算性能が求められるSoCをFPGAで実現するには、例えば「Stratix IV」と「Nios II /f」を組み合わせる事で対処出来る。Stratix IV は、最大で約82万ロジックエレメントのロジックを搭載しているため、このデバイスに「Nios II /f」を実装しても、FPGAチップ全体に占めるプロセッサ部のロジック数はわずか0.2%以下である。Nios II コアは、最大340MIPSの演算能力を備えており、これをマルチコア化することで演算性能をさらに高くすることができる(図2)。

本稿(前編)では、組み込み開発において、開発コストを抑えつつ、高性能と低消費電力の両立を実現するための手段として、FPGAがいかに有用であるかについて解説した。後編では、FPGAの演算性能を高めるための高速化手法や、SoC設計に向けて進化を続けるFPGAや開発ツールの最新動向などを紹介する。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.