第30回 「ARM搭載 FPGA によって格段に広がる SoC 開発の選択肢」(前編):FPGA Insights

SoC設計が大きな転換点を迎えつつある。製造プロセスの微細化が進んだことによって、SoCは性能や機能の向上が期待できる半面、従来のASIC手法ではその開発コストが膨大となり、多くのSoC開発が経済的に破綻をきたすようになってきた。そこで注目を集めているのがFPGAベースのSoC設計である。システム設計者にとっては、用途に最適なSoC開発を行うための選択肢が広がることとなる。本稿では、その中でも最先端プロセス技術を用いたSoC設計に着目し、最新FPGAの方向性や開発ツールの現状などについて解説する。

SoC(System on a Chip)とは、システム・レベルの機能をワンチップに集積したICを指す。この中はプロセッサブロックやメモリーブロック、周辺ロジックを含むロジックブロックなどで構成されている。製造プロセスの微細化によってICの集積度は格段に高まり、従来は複数個のICをプリント基板上で組み合わせなければ実現できなかったような機能や回路ブロックも、現在ではワンチップに集積することが可能となった。その上、高速演算処理をローパワーで実現することができ、BOMコストの低減も可能となるなど、システム設計者にとってSoC化するメリットは多い。

その一方で、最先端プロセスを用いたSoC設計では、増大する開発コストにより採算が合わなくなるといった問題が浮上している。例えば、28nmプロセス技術を用いてSoCの設計を行う場合、従来のASIC手法を用いると、製造に必要となるマスクの開発費用が10億円近くに達することも少なくない。開発環境などを導入すると数十億円規模の投資が必要となる。さらに設計が大規模かつ複雑になるために、SoCの開発期間もこれまでより長くなる。

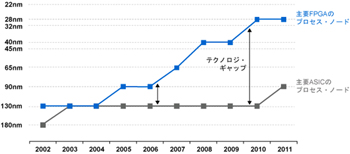

実際に、量産効果が見込まれる携帯電話端末向けや家庭用ゲーム機器向けなど一部の用途を除き、28nmプロセス技術のSoCをASIC手法で開発するには、経済的に破綻をきたすところまできているようだ。10年前から現在に至るまで、多くのASIC開発は130nm〜90nmのプロセスにとどまっている。このようなことも、FPGAベースのSoC設計を大きく後押ししている。特に、最先端のプロセス技術を使った多くのSoC設計では、 FPGAを用いるのが有効な手段の1つである、との見方が強まっている。(図1)

こうした中で、主要なFPGAベンダーは、28mnプロセス技術を使いハードコア・プロセッサを内蔵したFPGAの事業戦略を発表している。合わせて、FPGAベンダーが提供する開発ツールでは、IPコア間を内部接続するためのバス仕様も、従来のASIC/ASSPなどで一般的に使われている業界標準の規格が新たにサポートされるなど、流通しているIPコアの活用を含めて、ASICユーザーにも使いやすい開発環境が用意されつつある。このような動きは、最先端SoCの開発に取り組んでいるシステム設計者にとってASIC手法以外の新たな選択肢が広がることになる。

FPGAとプロセッサ・コアをワンチップに統合する「SoC FPGA」のアプローチは、決して目新しいものではない。2000年ころにXilinx社やAltera社などの有力FPGAベンダーがハードマクロの形でプロセッサ・コアを内蔵した第1世代のSoC FPGAを製品化している。しかし、製品コンセプトは優れていたものの、ビジネスとしては長続きせず、それらの製品は比較的短命に終わった経緯がある。

ハードコア・プロセッサを内蔵したFPGAがその当時、なぜ成功しなかったのか。その理由の1つはFPGAチップを製造するプロセス技術にあったといわれている。当時、Intel社やAMD社が製造するパソコン/サーバー向けの最先端プロセッサは、プロセス技術が130nm世代から90nm世代に移行していた。これに対して、FPGAの製造プロセスは、180nm世代から130nm世代への移行期にあった。このため、単体のプロセッサに比べて、「SoC FPGAは市場が要求する十分な性能が得られなかった。その上、SoCの形態に設計できても顧客が満足してくれるコスト設定ができなかった」と、当時を知る関係者は振り返る。

プロセッサ内蔵がFPGA設計の主流に

一方で、FPGAベンダーはソフトコア・プロセッサによるSoC FPGAのアプローチも同時に進めてきた。例えば、アルテラが供給している32ビットのソフトコア・プロセッサ「Nios / Nios II 」もその1つである。ソフトコア・プロセッサであれば、マルチコア化など並列処理のための回路構成が容易に行えるため、FPGAの特徴である“柔軟性”を最大限生かすことができる。

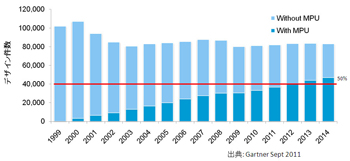

事実、FPGAにプロセッサIPを搭載したデザイン件数がこの10年間、着実に増えている。調査会社のGartner社がまとめたデータによれば、FPGAの設計件数に占めるプロセッサの搭載比率は、すでに4割台に達している。2012年以降は、その比率が過半数を超えると予測されている(図2)。

これまで、ハードコア・プロセッサ内蔵のFPGAでは事業としてあまりうまくいかなかったが、ソフトコア・プロセッサ内蔵のFPGAは、広い用途で活用されるようになってきたことを示したものだ。つまり、SoC FPGAのニーズがますます高くなることを裏付けている。

ところが、ソフトコア・プロセッサにも、ここにきて課題が表面化してきた。それは一般的に使われている組み込みシステム用プロセッサの動向である。これらのプロセッサは集積度が高まり、演算性能が格段に向上している。その上、製品のバリエーションも多く、市場のさまざまなニーズに応えやすい、ということがある。このため、FPGAベンダーが独自に開発しているソフトコア・プロセッサのみのサポートでは、顧客のニーズに対応できない状況になりつつある。

プロセスの微細化をリードするFPGA

今後のシステム開発において、FPGAが中核デバイスとなるためには、プロセッサのサポートが不可欠である。しかも、そのFPGAは高い演算性能を実現しつつ、低消費電力を達成していかなければならない。このような市場のニーズに応えていくためには、ハードコア・プロセッサの実装も再度考えていく必要がある。ハードコア・プロセッサは、ソフトコア・プロセッサに比べて、演算性能が高く、消費電力を抑えることができる。その上、チップ面積も小さくできることからコストメリットも得られるという特徴がある。

主なFPGAベンダーが、ここにきて再びハードコア・プロセッサ内蔵のFPGAを事業化する背景には、いくつかの理由がある。その1つが「プロセス技術の進化」である。前述の通り、10年前に第1世代のSoC FPGAで採用されていたプロセス技術は、パソコン用プロセッサに比べて1世代以上遅れていた。それが最新のFPGAは、最先端の28nmプロセス技術で製造されるなど、パソコン用プロセッサと同世代か先に進んだプロセス技術が用いられている。テクノロジーギャップがなくなったことで、ハードコア・プロセッサをFPGAに実装しても、演算性能やコストの面で市場のニーズに応えることが可能になったというわけだ。

淘汰が進むプロセッサ

FPGAベンダーがSoC FPGAに注力するもう1つの大きな理由として、世界市場でプロセッサ・アーキテクチャの淘汰が進んでいることを挙げることができる。これまで、4ビット〜64ビット品までさまざまなアーキテクチャのプロセッサが存在し、世界中のあらゆる電子機器に採用されてきた。それが、32ビット品以降のプロセッサでは“ARM”、“パワーPC”、“MIPS”、“IA”などに絞られてきたという現状がある。これにより、主要なプロセッサ・アーキテクチャをサポートしたFPGAであれば、使われる用途が幅広く、数量的にも量産効果を期待することができる。

それに加えて、システム設計者がSoC設計で重要視しているのが、これまで開発してきたソフトウエア資産の再利用である。近年ではシステム自体の機能が複雑になってきている。このため、ソフトウエア互換性を考慮したSoC設計は、開発期間の短縮や製品の品質/信頼性を維持していくうえでも重要な要件である。

これから開発される組み込み機器では、多くの用途で高機能なOSを用いることが前提となるであろう。このときに、市場で主流となっているOSに対応したプロセッサがサポートされていれば、機器のモデルチェンジなどでプロセッサを変更しても、同じOS上で動作するソフトウエア資産を流用することができる。つまり、FPGAベンダーにとっても主流となっているOSがポーティングされたプロセッサを用意しておくことで、ソフトウエア互換性という顧客のニーズに応えることが可能となる。

本稿(前編)では、SoC設計の現状や SoC FPGAが注目されている背景などについて述べた。後編では、FPGAベンダーが最先端SoCの設計に向けて提案しているFPGAソリューションなどについて解説する。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.