第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応:FPGA Insights

米Altera社は1月25日、28nmプロセス技術を用いたFPGA製品のポートフォリオを発表した。今回、ローエンド製品の「Cyclone V 」とミドルレンジ製品の「Arria V 」を新たに加え、ハイエンドからローエンドFPGAおよびASICまで、一気に28nm製品群を用意していく。これにより、FPGAユーザーは「性能/機能」や「消費電力」、「コスト」など、さまざまなシステムの要件に最適なFPGAを選択することが可能となる(写真1)。

Altera社の28nm製品としては、FPGAファミリのハイエンド品「Stratix V 」とASICファミリ「HardCopy V 」をすでに発表済みである。Stratix Vは2011年第1四半期よりエンジニアリングサンプルの出荷が始まる予定である。今回発表したArria Vは2011年後半より、Cyclone Vは 2012年第1四半期より、それぞれサンプル出荷を開始する計画である。

Altera社でプロダクト・マーケティングのシニア・ディレクタを務めるデビッド・グリーンフィールド氏(写真2)は、「さまざまなアプリケーションごとに異なる、顧客の多様な設計ニーズに対応していくためには、幅広いFPGA製品を用意していかなければならない」と語る。さらに今回、28nm製品群の全容を明らかにしたことについて「顧客が28nm製品に関する情報をより早く入手できれば、複数世代の製品企画を行う際にデバイスの選択肢が広がり、製品検討を早期に行える」と述べた。

最先端28nm Stratix V FPGAから低コスト・トランシーバ内蔵Cyclone IV GXまで、アルテラ製品群を最新情報と共に紹介し、誰でも今すぐ活用できるFPGAの利点と使いやすさを様々な角度から解説します。

>>本セミナーを視聴される方はこちら(30分)

4技術領域で技術革新

Altera社では、多種多様なアプリケーションごとに異なる性能や機能のニーズを満たすために、FPGAの製品仕様を以下に挙げる4つの技術領域で策定している。

1)プロセス技術

2)トランシーバ技術

3)製品アーキテクチャ

4)システムIP

プロセス技術:高性能とローパワーの2種類

28mn製品は、2つのプロセス技術を適用して製造される。ハイエンド製品に位置付けるStratix VとASIC製品のHardCopy Vは台湾TSMC社の28HP(High Performance)プロセス技術を使う。低コスト製品のCyclone Vおよびミッドレンジ製品のArria Vは同じくTSMC社の28LP(Low-Power)プロセス技術を用いる。これによって「顧客のニーズに個別に対応できるソリューションが提供できる」(グリーンフィールド氏)。

トランシーバ技術:600Mbps〜28Gbpsをサポート、用途ごとに最適化

28nm製品でサポートされるトランシーバ性能は、600Mbpsから28Gbpsまでと広範囲である。モジュール構造の設計によりデータレートごとに最適化を行い、それぞれの帯域で消費電力を最小化している。例えば バックプレーン・サポートやイコライザーの性能も帯域ごとに必要十分なものを適用する。データレートが5Gbpsで消費電力が88mW、10Gbpsで135mW、さらには28Gbpsと高速でありながら200mWと小さい消費電力を実現する。

製品アーキテクチャ:用途別に異なる実装

オンチップ・メモリの構造・容量は、アプリケーションによる要求に合わせることが重要である。例えば、100GbEラインカードなど、より高いデータ性能とビット密度が求められる用途向けの「M20Kブロック」、リモート無線ユニットなど多くのポート数や高いバッファリング性能が求められる用途向けの「M10Kブロック」を用意して製品により使い分ける。また全てのアプリケーションに汎用的に使われるFIFOなど小サイズのバッファに適した「MLABブロック」を全製品で使用できるようにしている。

外部メモリとのインタフェースも、そのニーズはさまざまである。例えば、暗視ゴーグルやハンディ・プロジェクタなど可搬型システムでは、低消費電力や短いレイテンシ、省スペースなどの要求が強い。このような用途向けには、「Mobile DDR」、「LPDDR2」、「400MHz DDR3」に対応するメモリ・コントローラをハードIPとして搭載する。ビデオスイッチャや放送用カメラ、リモート無線ユニットなど、性能と消費電力やコストのバランスが重要なミッドレンジの用途には、汎用的でコスト・パフォーマンスが高い「533MHz DDR3」に対応するメモリ・コントローラをハードIPで搭載する。ハードIPはFPGAデバイスのコストと消費電力を低減することに有効である。40GbE/100GbEスイッチなどの先端のワイヤライン通信システムを含むハイエンド・アプリケーションの場合は、最高の性能を求めつつ、インタフェース方式やビット幅における要求がさまざまである。このため、「800MHz DDR3」や「RLDRAM III」、「QDR II+」など複数のメモリのそれぞれに対応できるように、ソフトIPによるメモリ・コントローラをサポートする。

また、I/O関連では、ハイエンド向けには最高性能を追求するという観点から1.4GbpsのLVDSをサポートする。これをミッドレンジ向けにそのまま搭載してもコストと消費電力の要求への対応が困難になるため、1.25Gbpsの性能でバランスをとった LVDSを設計している。また産業機器などの要求に応えるために低コスト向けには3.3V@16mA駆動をサポートする。アプリケーションごとに異なるニーズの全てに対応しようとするとサイズ(コスト)と消費電力を最適化できないため、このように必要なものを適切な製品に実装することが重要である。

システムIP:システムレベルのIP開発を加速

Altera社はターゲット市場に重要なシステムIPに注力して社内で開発している。特にアプリケーションを超えて幅広い分野に必要となるシステムIPはハード化して FPGAに搭載することで、用途によって異なる「コスト/消費電力」、「性能」といった要件を満たしている。例えば、低コストからミッドレンジ向けにはハードIPとして、前述のメモリ・コントローラとトリプルスピード(10/100/1000Mbps)イーサネットMACを搭載する。ハイエンド向けには顧客ごとのシステム要求に柔軟に対応するためにメモリ・コントローラはソフトIPで対応するが、40G/100Gのシステムに必要となるPCS/MAC機能やInterakenプロトコルなどをハードIPでサポートする。このような機能は厳しい性能、消費電力、サイズの条件にミートするためにハードIPが必須である。また、今後ほとんどの市場で標準的に採用されることになるPCI Express(PCIe)インタフェースでは、低コスト向けにPCIe Gen2×1、ミッドレンジ向けに PCIe Gen2×4、そしてハイエンド向けには PCIe Gen3×8まで対応している。今後もシステムIPの提供を展開していく。一例として、2010年12月にOTN(Optical Transport Network)用IP市場で強みを持つ米Avalon microelectronics社を買収し、次世代通信市場向けシステムIPのさらなる拡充に取り組んでいる。

設計ニーズに応える28nm製品

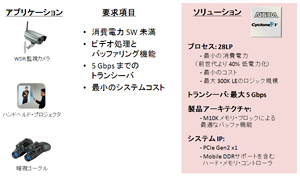

今回発表の28nm技術を使ったCyclone Vファミリは、モータコントロールやディスプレイ、ソフトウエア無線などの用途に適している。40nm技術を用いた前世代品に比べて、消費電力は約40%小さい。また、最大5Gbpsで動作する12個のトランシーバ、ハード化されたPCIe GEN2×1ブロック、および外部メモリ用のインタフェースとしてLPDDR2、Mobile DDR、DDR3に対応するハード・メモリ・コントローラなどを備えている(図1)。

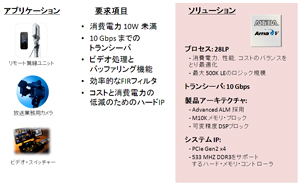

同じくArria Vファミリは、リモート無線ユニット、映像スタジオ・ミキサ、10G/40Gラインカードなどの用途に適した性能や機能を備えた製品である。前世代品に比べて消費電力を約40%削減した。データレートが最大10Gbpsのトランシーバ、外部メモリとのインタフェースとしてDDR3対応のハード・メモリ・コントローラ、可変精度DSPブロックによるFIRフィルタなどを内蔵することができる(図2)。

同社の28nm製品としては、上記の2ファミリ以外に、2010年4月に発表されたStratix VファミリとHardCopy V ファミリがある。Stratix Vは、40G/100Gラインカード、LTE用基地局、ハイエンドRFカード、軍用レーダーなどの用途に向けた製品である。Startix V GTは28Gbpsと14.1Gbps(バックプレーン)、GXとGSは14.1Gbps(バックプレーン)をサポートする。14.1Gbpsのサポートにより、16G Fibre Channel などの新しい高速プロトコルのサポートが可能になった。一方、HardCopy Vは、FPGAとASICの特徴を兼ね備えており、FPGAからASICへの移行を低リスクで可能とする製品である。こちらも14.1Gbpsのトランシーバを搭載する。

FPGA にて1 TFLOP という高速の処理速度を実現した、28nm Stratix V FPGA 含む、アルテラの技術革新を紹介し、固定小数点および浮動小数点による信号処理の両方をサポートするうえで、 アルテラの斬新なアーキテクチャ 「可変精度DSP」が果たす重要な役割について、そして28nm 最新FPGAがサポートする各種浮動小数点アプリケーションについても紹介します。

>>本セミナーを視聴される方はこちら(30分)

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●28nm FPGA の多機能性を向上させるパーシャル & ダイナミック・リコンフィギュレーション

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

Copyright © ITmedia, Inc. All Rights Reserved.