LVDSを基礎から理解する、高速、長距離、低EMIの理由(前編):【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】LVDS(第1回) LVDSを基礎から理解する、高速、長距離、低EMIの理由(前編) (クリックで動画再生)

LVDS(小振幅差動信号)とは、「Low Voltage Differential Signaling」という英文の頭文字を取って作られた言葉である。その特徴は、英文の日本語訳の通り、低い電圧振幅の信号を差動方式で伝送する点にある。電圧振幅は350mVと極めて小さい。これを差動方式で伝送することで、数百M〜数Gビット/秒と高い伝送速度を実現する。「高速」「長距離伝送」「低EMI」がLVDSの特徴である。

なぜ、LVDSが登場したのか。その背景には、マイクロプロセサやDSP、FPGA、ASICなどのデジタル信号処理チップの性能向上がある。こうしたチップの性能は高まるものの、入出力インタフェースのデータ伝送速度はそのほど向上しない。このため電子機器全体の性能でみたときに、入出力インタフェースがボトルネックになるケースが増えてきたからだ。こうした問題を解決する技術として開発されたのがLVDSである。

LVDSが市場に始めて登場したのはいまから約16年前のことだ。米National Semiconductor社が1994年にDS90C031/032 LVDSドライバ/レシーバを製品化している。この製品は低速なRS-422/485の高速版として様々なアプリケーションで使用された。なお、LVDSの基本技術は、1995年に「ANSI/TIA/EIA-644」として標準化された。

裾野が広がるLVDS関連製品

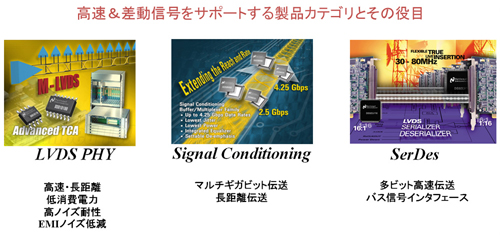

約16年前とかなり以前に製品化が始まったLVDSだが、現在でもかなり多くのLVDS関連チップが市場に投入されている。LVDSの生みの親であるナショナル・セミコンダクター社では現在、LVDSなどを含む通信/インタフェース関連チップを300品種以上販売している。同社の日本法人であるナショナル セミコンダクター ジャパンのマーケティング本部でプロダクトマーケティング課長を務める河西基文(かわにし・もとふみ)氏によると、「300を超える関連製品は、大きく3つの製品群に分類できる」という(図1)。

図1 LVDS関連製品の分類

図1 LVDS関連製品の分類LVDS関連製品は大きく3つに分類できる。LVDSなどに対応したPHY(物理層)チップ(ドライバ/レシーバ・チップ)、シグナル・コンディショニング・チップ、SerDesチップである。

1つめは、LVDSなど注1)のPHY(物理層)チップである。言い換えれば、LVDSなどに対応したドライバICとレシーバICである。一般的なデジタル信号処理チップでは、TTL/CMOSの論理レベルに対応している。TTL/CMOSでは高速な信号を長距離送ることができない。仮に送ったとしても、ビット誤り率(BER)が高くなる上に、高い強度のEMI(Electro-magnetic Interference)が放射されてしまう。そこで、TTL/CMOSの代わりにLVDSを使う。TTL/CMOSの信号をLVDSに変換して、高速信号を長距離伝送し、その信号を受信してTTL/CMOSの信号に戻すわけだ。こうした機能を実現するチップがドライバICとレシーバICになる。

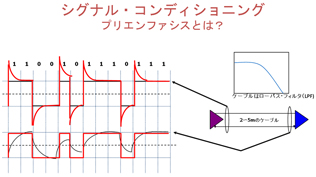

2つめは、シグナル・コンディショニング・チップである。このチップはLVDSなどを利用して、数百M〜数Gビット/秒と高い伝送速度で信号を送ったり、数百mもの長い距離にわたって信号を伝送したりすることを可能にするものだ。具体的には、信号に対してプリエンファシスやデエンファシス、イコライザといった処理を施す。 プリエンファシスとデエンファシスはいずれも、信号を伝送する配線の特性に合わせて、信号波形に対してあらかじめ処理を加える技術である(図2)。違いは、プリエンファシスが信号振幅を高める方向に処理する一方で、デエンファシスは低減する方向に処理する点にある。イコライザは、歪んだ受信信号を補正してきれいな波形を生成する技術である。

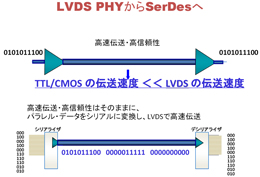

3つめは、SerDes(サーデス)チップである。SerDesとは、シリアライザ(serializer)とデシリアライザ(deserializer)を組み合わせた言葉である。例えば、10ビット幅のパラレル信号を1本のシリアル信号に変換するのがシリアライザで、逆に1本のシリアル信号を10ビット幅のパラレル信号に変換するのがデシリアライザになる。つまり、シリアライザで作成したシリアル信号をLVDS信号としてドライバで送信し、レシーバで受信したシリアル信号をデシリアライザで元の10ビット幅のパラレル信号に戻すといった使い方をする(図3)。

図2 プリエンファシスとは

図2 プリエンファシスとはシグナル・コンディショニング・チップで採用されている技術は大きく、プリエンファシスとデエンファシス、イコライザの3つに分けられる。図は、プリエンファシスの原理を示したものだ。ローパス・フィルタとして機能するケーブルによって失われる信号波形の成分を、送信時にあらかじめ補っておく技術である。

図3 シリアライザとデシリアライザ

図3 シリアライザとデシリアライザシリアライザとデシリアライザは、まったく逆の役割である。シリアライザでは、パラレル・データを高速のシリアル信号に変換する。一方、デシリアライザではシリアル信号を元のパラレル・データに戻す役割を果たす。

ケーブル伝送や基板間伝送が主用途

ここでは、3つの大きな製品分類のうち、PHYチップ、すなわちドライバ/レシーバ・チップに焦点を絞って話を進める。

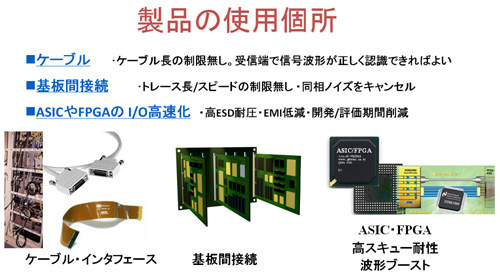

ドライバ/レシーバ・チップの主なアプリケーションは、次の三つに分けられる(図4)。第1に、ケーブルを介した信号伝送。第2に、プリント基板間での信号伝送、第三にFPGAやASICなどの入出力インタフェースの高速化やケーブル延長、保護である。いずれも、前述のLVDSの特徴である高速、長距離伝送、低EMIを十分に生かせるアプリケーションと言える。

図4 LVDS対応のドライバ/レシーバ・チップの3大用途

図4 LVDS対応のドライバ/レシーバ・チップの3大用途LVDSなどに対応したドライバ/レシーバ・チップの用途は、ケーブルを介した高速信号の長距離伝送と、プリント基板間の高速信号伝送、ASICやFPGAなどの入出力(I/O)インタフェースの高速化、ケーブル延長、I/Oの保護である。

ナショナル セミコンダクター ジャパンが販売するLVDS対応ドライバ/レシーバ・チップの中で代表的な製品は「DS90LV047A/048A」である。DS90LV047Aはドライバ・チップ、DS90LV048Aはレシーバ・チップである。同社の河西氏によると、「約10年前に製品化したチップだが、現在でも業界においてデファクト・スタンダードの地位を占めている」という。

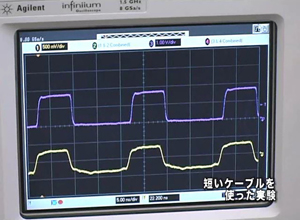

図5 LVDSの伝送波形

図5 LVDSの伝送波形ナショナル・セミコンダクター社のドライバ/レシーバ・チップ「DS90LV047A/048A」を使って、LVDS信号を実際に伝送した際の波形である。送信信号のクロック周波数は50MHz、すなわち100Mビット/秒のLVDS信号を伝送した。約1mのケーブルを伝送したため、立ち上がり時と立ち下がり時に若干鈍りが発生しているが、良好な波形が得られている。

図5は、DS90LV047AとDS90LV048Aを使った伝送実験で得られた実際のLVDS信号波形である。50MHzのクロック信号(デューティ比は50%)をDS90LV047Aに入力することで100Mビット/秒のLVDS信号を生成し、約1mの長さのケーブルで伝送した後の信号だ。つまり、DS90LV048Aに入力される直前の信号である。ケーブルのローパス・フィルタ特性によって、波形は若干鈍っているもの、良好な形状の信号波形が得られている。この波形であれば、DS90LV048Aで問題なく受信でき、50MHzのクロック信号を再生して出力できる。

今回は、LVDSの製品体系やアプリケーション動向などを中心に紹介した。ただ、読者の中には、「LVDSを使えばなぜ高速伝送や長距離伝送が可能になるのか、なぜEMIを低く抑えられるのか」という疑問を持たれた方もいらっしゃるだろう。その答えについては、後編で詳しく解説する。

注1)ここで「LVDSなど」と表記しているのは、300を超える関連製品の中にはCML(Current Mode Logic)やほかの差動技術を採用したチップも含まれているからである。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード