LVDSを基礎から理解する、さらなる高速/長距離化を可能にする技術(後編):【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】LVDS(第2回)LVDSを基礎から理解する、さらなる高速/長距離化を可能にする技術(後編) (クリックで動画再生)

ナショナル セミコンダクター ジャパンが販売するLVDS対応SerDesチップの中で代表的な製品である「Channel Link II」ファミリ。この製品では、LVDS信号伝送の高速化と長距離化を目的に、デエンファシスとイコライザと呼ぶ手法が搭載されている。いずれもシグナル・コンディショニングと呼ばれる機能であり、LVDSの3つの大きな製品分野の1つだ。後編では、このシグナル・コンディショニングについて詳細を解説する。

伝送路のローパス特性を補償する

シグナル・コンディショニングには、大きく3つの手法がある。プリエンファシス、デエンファシス、イコライザの3つである。

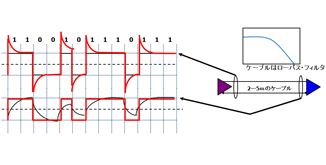

このうち、プリエンファシスとデエンファシスは、送信(ドライバ/シリアライザ)側で実行する手法である。ナショナル セミコンダクタージャパンのマーケティング本部でプロダクトマーケティング課長を務める河西基文(かわにし・もとふみ)氏によると、「プリエンファシスもデエンファシスも、考え方は同じ」と説明する。つまり、LVDS信号の伝送路の低域通過(ローパス)フィルタ特性を考慮して、送信波形に対してあらかじめ調整しておくというものだ。ただし、その調整方法が若干異なる。

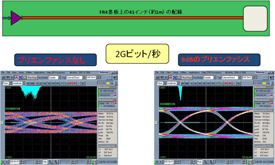

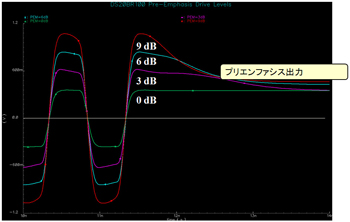

プリエンファシスは、ローパス・フィルタとして働く伝送路で減衰される高周波成分を補う方法である(図1)。例えば、図2のように、FR4基板上の約1mの配線(伝送路)で2Gビット/秒のLVDS信号を伝送する場合、プリエンファシスなしでは、受信端でのアイ・パターンはほぼつぶれてしまう。そこで、伝送路のローパス・フィルタ特性を考慮して、高周波成分を9dB持ち上げるプリエンファシスをかけることでアイ・パターンを完全に開かせることが可能になる。

図1 プリエンファシスとは

図1 プリエンファシスとはプリエンファシスとは送信(ドライバ/シリアライザ)側で実行するシグナル・コンディショニング手法の1つ。伝送路(ケーブル)のローパス・フィルタ特性に合わせて高周波成分を持ち上げる。プリエンファシスをかけないと受信端での伝搬波形は鈍ってしまうが、プリエンファシスをかけることで受信端での伝搬波形のアイの開口に寄与する。

図2 プリエンファシスの効果

図2 プリエンファシスの効果FR4基板上の約1mの配線(伝送路)を使って2Gビット/秒のLVDS信号を伝送する場合、プリエンファシスをかけなければ、受信端でのアイ・パターンはほぼつぶれてしまう。ここでは伝送路のローパス・フィルタに合わせて9dBのプリエンファシスをかけることでアイ・パターンは大きく開く。

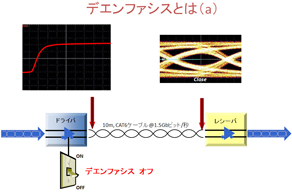

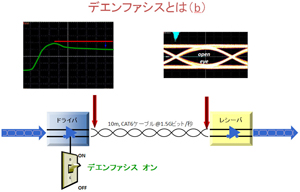

一方、デエンファシスは、プリエンファシスとはまったく逆の調整方法を採用する。すなわち、伝送路での減衰量が少ない低周波成分をあらかじめ減らしておく方法である(図3(a)、(b))。こうすることで、伝送路で失われてしまう高周波成分とのバランスを確保するわけだ。この手法でも、受信端での伝送波形のアイ・パターンはきれいに開く。

デエンファシスは、プリエンファシスと同様に、送信側で実行するシグナル・コンディショニング手法の1つ。伝送路(ケーブル)のローパス・フィルタ特性によって減衰してしまう高周波成分に合わせて、あらかじめ低周波成分を抑えておく。デエンファシスをかけないとアイ・パターンがつぶれているが(a)、デエンファシスをかけることでアイ・パターンが大きく開く(b)。

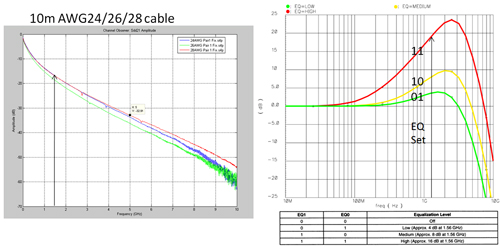

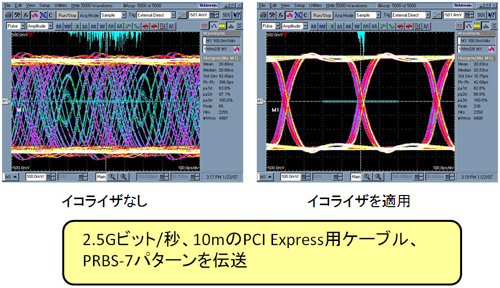

残る1つの手法であるイコライザは、受信(レシーバ/デシリアライザ)側で実行する手法である。実行する場所がプリエンファシスやデエンファシスと異なるものの、「基本的な考え方に大きな違いはない」(同氏)という。伝送路のローパス・フィルタ特性によって失われてしまう周波数成分を、受信側で持ち上げる(ブーストする)ことで補償する。例えば、あるケーブルでLVDS信号を10m伝送すると、1.56GHzの周波数成分が約18dBも(約1/8に)減衰してしまう(図4)。そこで、この周波数成分を受信側で補うわけだ。イコライザを適用する前はアイ・パターンがまったく開いていなかったが、適用することでアイ・パターンを完全に開かせることが可能になる(図5)。

図4 イコライザとは

図4 イコライザとはイコライザは、受信(レシーバ/デシリアライザ)側で実行するシグナル・コンディショニング手法である。伝送路(ケーブル)で減衰した周波数成分を持ち上げる。この例では、10m伝送することで1.56GHzの成分が約18dB減衰する。そこで、受信側で1.56GHzの成分を18dB持ち上げることで補償している。

図5 イコライザの効果

図5 イコライザの効果10mのケーブル(PCI Express)で、2.5Gビット/秒のPRBS-7パターンの信号を伝送する場合、イコライザなしではアイ・パターンが完全につぶれてしまう。イコライザをかけることで、アイ・パターンが大きく開く。

最適な補償手法はどれか?

シグナル・コンディショニングの手法には、このようにプリエンファシスとデエンファシス、イコライザの3つがある。この3つの手法は、どのようなメリットとデメリットがあり、それによってどのように使い分けるべきなのだろうか。

まずは、送信側で実行するプリエンファシス/デエンファシスと、受信側で実行するイコライザの使い分けを検討してみる。河西氏は「伝送速度が2~3Gビット/秒程度までで、伝送路の減衰量が10dB以下であれば、まずは、送信側で補償をかけるプリエンファシス、もしくはデエンファシスに見当をつける」という。その理由は、送信側で補償をかければ、受信端においてアイ・パターンが開いているか、いないかを測定により簡単に確認できるからだ。イコライザが内蔵されたデシリアライザ製品等では、受信端でのアイ・パターンはつぶれたままで、LVDS信号が正しく伝送できているかいないかを確認できない。

しかし、伝送速度が3Gビット/秒以上の場合や、減衰量が非常に大きな場合(ケーブルが長い)はイコライザに頼らざるを得ない。例えば、ある周波数の減衰量が34dBと大きな伝送路では、その周波数成分は1/50に減ってしまう。これをデエンファシスで補償する場合は、低周波成分を1/50に抑えなければならない。これでは信号振幅が小さくなりすぎてしまい、LVDS信号を正しく伝送できなくなる。

高速伝送に向くデエンファシス

図6 アナログ的なプリエンファシス

図6 アナログ的なプリエンファシスアナログ的なプリエンファシスとは、方形波をハイパス・フィルタに通したような波形が得られる手法である。この方法を使えば、ジッターの増加は限定される。一方、図1に示したプリエンファシスの波形はデジタル的な手法を用いたもので、ジッターの問題が発生する公算が高い。

ただし、こうした議論が成立するのは、「きれいなプリエンファシス/デエンファシスがかけられること」(河西氏)が大前提となる。同氏によると、プリエンファシス/デエンファシスには、デジタル的な方法とアナログ的な方法があり、きれいなプリエンファシス/デエンファシスとはアナログ的な手法だという。

デジタル的な手法とは、意図的にオーバーシュート、アンダーシュートやデジタルデバイスでは内部の高速クロックに同期したタイミングで先頭ビットの振幅を大きくするものだ。例えば、プリエンファシスの場合は、「1」が連続する信号の最初の「1」の振幅を2倍に持ち上げ、次の「1」はそのまま出力する。こうすることで高周波成分を持ち上げることが可能になる。しかし、信号がデジタル的に急激に変化してしまうことになる。この結果、受信端でのジッターが増える。一方、アナログ的な手法では、方形波を高域通過(ハイパス)フィルタを通したような滑らかな伝送波形が得られる(図6)。受信端でのジッターの増加は限定的である。

次に、プリエンファシスとデエンファシスの使い分けを検討してみよう。プリエンファシスの欠点は、信号の高周波成分を持ち上げるため、信号振幅が大きくなってしまう点にある。振幅が大きくなれば、信号の遷移に時間がかかる。つまり、高速なデータ伝送に対応できなくなる。

プリエンファシスは、どの程度までの伝送速度に使えるのだろうか。河西氏は、「2~3Gビット/秒程度まで」という。従って、それ以上の伝送速度ではデエンファシスを使うべきである。デエンファシスでは、低周波成分を抑えることで補償をかけるため、信号振幅は小さくなる。このため、高速なデータ伝送に対応しやすいからだ。「実際に、LVDSよりも高速なデータ伝送に用いられるCML(current mode logic)では、シグナル・コンディショニングの手法としてデエンファシスが使われる」(同氏)という。

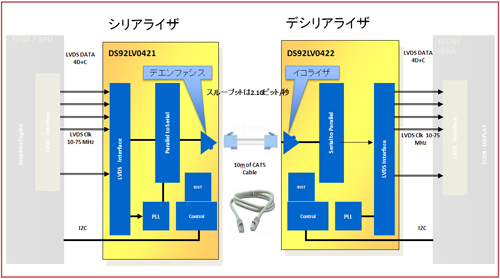

最後に、デエンファシスとイコライザを採用した新しいLVDS対応SerDesチップ「DS92LV0421/DS92LV0422」を紹介しよう。FPGAやグラフィックス・プロセッサなどから出力された4つのLVDSデータ信号を、1本のシリアル信号に変換して伝送するチップである。シリアライザのDS92LV0421にデエンファシス、デエンファシスのDS92LV0422にイコライザを搭載することで、高速化と長距離化に対応した(図7)。スループットは最大2.1Gビット/秒、伝送距離はカテゴリー5(AWG24)のより対線を使った場合に10m程度である。

図7 シリアライザとイコライザを採用したSerDesチップ

図7 シリアライザとイコライザを採用したSerDesチップナショナル セミコンダクター ジャパンが販売するSerDesチップ「DS92LV0421/DS92LV0422」である。4本のLVDSデータ信号とLVDSクロック信号を1対にシリアル化して伝送する。スループットは最大2.1Gビット/秒。伝送距離は、カテゴリー5(AWG24)のより対線を使った場合に約10mである。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード