電源回路設計の手順と勘所(3) FPGAの電源に課せられた要件を理解する:【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】電源回路設計の手順と勘所(3) FPGAの電源に課せられた要件を理解する (クリックで動画再生)

現在、FPGAを利用しているエンジニアの数はかなり多いだろう。かつては、非常に高価だったため、試作時などだけに使い、量産時にはASICを起こすといったケースが多かった。しかし、最近ではFPGAの価格はかなり下がってきている。その一方で、ASICの初期開発費(NRE:Non Recurring Expenses)は高騰している。このため、テレビなどの民生用電子機器や、携帯型電子機器などの量産品にも、FPGAを適用するケースが増えている。FPGAは、かなり手軽なツールになったと言えるだろう。

ただし、FPGAの設計に当たっては、トラブルが少なくないようだ。設計現場の声として良く耳にするのは、電源回路設計に関するトラブルである。FPGAのコア回路に供給する電源電圧は1V近辺と非常に低い上に、供給電流量は比較的多いからだ。しかも、出力電圧に重畳されるリップル電圧には厳しい制約条件が課されており、それを満足できないとFPGAが誤動作してしまう危険性がある。

FPGAに電力を供給する電源回路の設計は決して簡単ではない。ところが、FPGAの設計者はデジタル分野のエンジニアがほとんどだ。電源回路設計に関する知識を十分に身に付けたエンジニアは多くない。こうした、デジタル分野のエンジニアでも、トラブルを起こすことなく、FPGAの電源回路を設計するにはどうすればよいのだろうか。

厳しい要件を課せられるFPGAの電源回路

そこで米National Semiconductor社は、こうしたトラブルを未然に防ぎ、かつ簡単に電源設計できることを目的に、FPGAの電源回路設計に向けたオンライン設計支援ツール「WEBENCH FPGA Power Architect」を開発し、2010年9月からサービスを開始した(図1)注1)。

このオンライン設計ツールの特徴は、市場で入手可能なほとんどのFPGAを対象にしている点にある。しかも、それぞれのFPGAの電源回路に求められる要件が、あらかじめ登録してある。使用するFPGAのデータ・シートをユーザーが読み込んで、電源回路に関する要件を抜き出すという作業は一切いらない。データが登録されているFPGAのベンダーは、米Altera社と米Xilinx社、米Actel社、米Lattice Semiconductor社の4社である。ナショナル セミコンダクター ジャパンのマーケティング部門で電源関連ICを担当する山田浩二氏は、「各FPGAベンダーが新製品を発表すれば、当社がすぐに、そのFPGAの電源回路に必要な要件などのデータを登録する。従って、ユーザーは、新製品の発表と同時に、電源回路の設計検討を始められる」と指摘する。

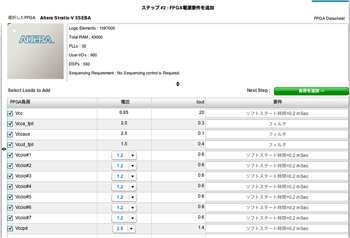

今回は、Altera社が2010年4月に発表した最新FPGA「Stratix V」を対象に、それに供給する電源トポロジーと電源回路の設計を実際に行ってみよう。このFPGAは、28nmの微細加工ルールで製造したもので、無線通信の基地局やネットワーク装置、医療機器などのアプリケーションに向けた品種である。ロジック・エレメントの搭載数の違いによって複数の製品が用意されているが、今回は搭載数が最も多い「5SEBA」を選択する(108万7000個)。

選択するとオンライン設計支援ツールの画面に、そのFPGAに必要される電源電圧レールがすべて表示される(図2)。「5SEBA」の電源レールは全部で12個もある。FPGAのコア部に供給する電源レール(VCC)は、電圧が0.85Vと低く、供給電流は20Aと非常に多い。

許容できる出力リップルはわずか60mV

FPGAの選択が済んだら、画面右端の「負荷を追加」ボタンをクリックする。すると、各電源レールに対する要件を設定する画面に移行する。なお、入力電圧範囲については、「5SEBA」の主要なアプリケーションである無線通信の基地局を想定して48V(最小値は44V、最大値は52V)と設定した。

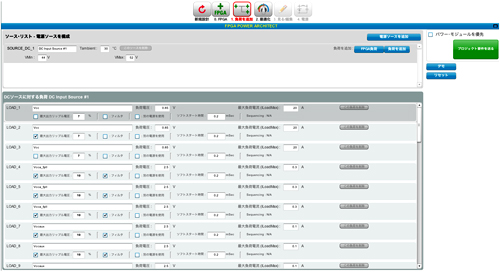

設定可能な電源要件は、「出力リップル電圧」と「フィルタ」、「別電源を使用」、「ソフトスタート時間」、「Sequencing」の5つである(図3)。それぞれの要件について、以下で詳細を説明しよう。

出力リップル電圧は、その名の通り、出力電圧に現れるリップル成分の許容範囲である。FPGAのコアに供給する電源電圧(VCC)は、0.85Vの7%と規定されている。「つまり、リップル成分は約60mVしか許されない。電源回路設計の観点から見れば、かなり厳しい要件であることは間違いない」(山田氏)。

次のフィルタについては、FPGAに集積されたPLL(Phase locked loop)などに供給する電源レール(Vcca_fpll)において使用が求められている。PLLなどのアナログ部では、ノイズの存在を嫌う。ノイズがあると、回路性能に大きな支障を来す可能性があるからだ。従って、アナログ部向けの電源レールに対しては、ノイズを除去するフィルタの挿入が求められているわけだ。

その次の「別電源を使用」も、ノイズに関連した要件だと言える。例えば、アナログ部向けに電源を供給する回路をデジタル部向けと共有してしまうと、デジタル部を原因として発生した電源/グラウンド層におけるノイズの影響をアナログ部も受けてしまう。そこで「別電源を使用」を選択すれば、アナログ部向けの電源回路とデジタル部向けの電源回路の電源層とグラウンド層を分離することができ、デジタル部を原因とするノイズの影響を排除することが可能になる。

ソフトスタート時間は、電源投入後に、電源電圧が立ち上がるまでの時間である。ms(ミリ秒)の単位で設定が可能だ。

最後の「Sequencing」だが、「5SEBA」については、デフォルトで「N/A」と記載されており、選択できなくなっている。その理由について、山田氏は、「かつては、FPGAの電源シーケンスは極めて重要なものだった。正しく設定しないと、FPGAがラッチアップを起こして、最悪のケースでは破損してしまう可能性があったためである。しかし、最近のFPGAは、チップの内部においてソフトウェアを使って電源シーケンスを制御するように改良が進んでいるため、ユーザーが電源シーケンスを配慮する必要がなくなっている。このため、選択できなくなっている」と説明する。

各電源レールの要件を記入すれば、負荷の設定は完了だ。次回は、今回の負荷設定を使って、実際に電源トポロジーや電源回路を設計する。

注1)「WEBENCH FPGA Power Architect」は、ナショナル セミコンダクター ジャパンのホームページから利用できる。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード