電源回路設計の手順と勘所(6) 電気的特性を評価する(後編):【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】電源回路設計の手順と勘所(6) 電気的特性を評価する(後編) (クリックで動画再生)

FPGAやASIC、DSPなどのコア回路に電力を供給する電源回路の設計は難しい。電源電圧が低く、供給電流が大きいためだ。前回は、そうしたFPGAのコア回路向け電源回路を、米National Semiconductor社がサービスを提供しているオンライン設計支援ツール「WEBENCH Power Designer」を使って実際に設計してみた。そして、その電源回路の「Steady State(定常状態)」をシミュレーションして出力電圧に含まれるリップル成分を解析し、FPGAベンダーが求める電源電圧の許容範囲に収まっていることを確認した。

ただし、電気的な特性の評価作業はこれだけでは不十分である。検討すべき項目がまだ残っている。具体的には、入力電圧の変化や負荷の動作変化による出力電圧変動を評価する必要がある。つまり、過渡応答特性を評価する必要があるわけだ。

負荷応答特性に注意せよ

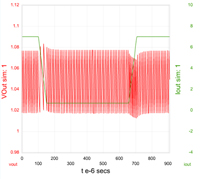

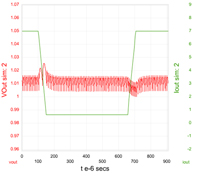

図1 負荷応答特性(ESRは0.06Ω)

図1 負荷応答特性(ESRは0.06Ω)当初に設計した電源回路の負荷応答特性である。出力コンデンサの容量は1000μFでESRは0.06Ωである。出力電圧の変動幅は1.015V〜1.085Vで、ピーク・ツー・ピーク値は約70mVである。

WEBENCH Power Designerで過渡応答特性を評価する場合は、シミュレーション画面において、シミュレーション・タイプの選択肢の中で「Input Transient」や「Load Transient」を選ぶ。

今回は、出力電圧を大きく変動させる危険性が高い「Load Transient」、すなわち負荷応答特性を実際に確認する。負荷応答特性とは、負荷の動作状態が急激に変化したことを想定して、供給電流を小さな値から大きな値へ、もしくは大きな値から小さな値へ変化させたときに、出力電圧がどのように変化するかを示すものだ。一般に、供給電流が減少した場合、出力電圧は上昇する。逆に、供給電流が増加した場合、出力電圧は下降する。従って、出力電圧のリップル成分のピーク・ツー・ピーク値は大きくなるため、電源電圧の許容範囲を超えてしまう危険性が高い。

「Load Transient」を選択し、「新しいシミュレーションを開始」ボタンを押すとシミュレーションが始まる。解析結果を図1に示す。出力電圧のリップル成分の変動幅は1.015V〜1.085Vと求まった。ピーク・ツー・ピーク値は約70mVである。前回、「Steady State」のシミュレーションで求めた出力電圧のリップル成分のピーク・ツー・ピーク値は約55mVだった。従って、負荷応答特性では、これを15mV程度上回ったことになる。果たして、設計した電源回路は、FPGAのコア部用として使うことは可能なのか。ナショナル セミコンダクター ジャパンの山田浩二氏は、「決して、悪くない結果である。電源電圧の許容範囲に対する制約条件を1V±10%だと仮定すれば、その範囲に十分に収まっているからだ。ただし、1V±7%や1V±5%といった厳しい制約条件はクリアできない。1V±7%である70mVを若干超えてしまっているためである」と評価する。

電源ICの特徴を理解せよ

だからといって、今回設計した電源回路がFPGAのコア回路用に使えないと決まったわけではない。出力電圧のリップル成分を抑え込む対策方法がほかにあるからだ。外付け部品の特性値を見直せばよい。

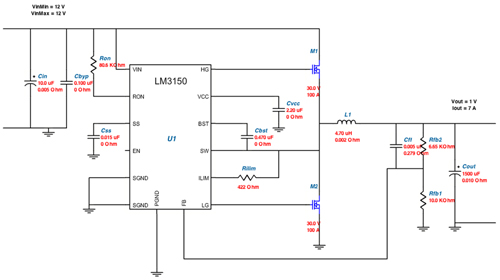

ただし、どの外付け部品の、どの特性値を見直すか。それを知るには、採用した電源ICの特徴を理解する必要がある。今回採用した電源IC「LM3150」は、高速応答が特徴のリップル制御方式を採用している。出力電圧に現れるリップル成分を検出し、それをフィードバックすることで出力電圧を安定化する制御方式である。従って、等価直列抵抗(ESR:Equivalent Series Resistance)が小さい出力コンデンサを選べば、出力電圧のリップル成分を抑え込むことができる。

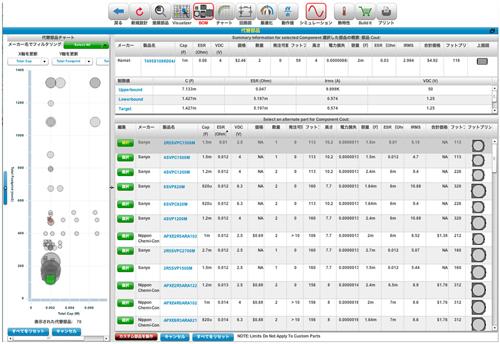

当初、設計した電源回路では出力コンデンサに、容量が1000μFでESRが0.06Ωのタンタル電解コンデンサを採用していた。この出力コンデンサをESRが小さい品種に変更する。変更する場合は、回路図において出力コンデンサをダブルクリックする。すると、出力コンデンサの選択肢が表示されるため、この中からESRが最も小さな品種を選べばよい(図2)。今回は、容量が1500μFでESRが0.01Ωと小さい有機半導体アルミ電解コンデンサ(OSコン)を選んだ(図3)。ESRは、当初使っていたコンデンサの1/6である。

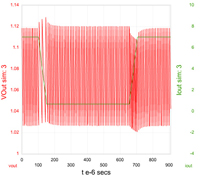

図5 負荷応答特性(ESRは0.14Ω)

図5 負荷応答特性(ESRは0.14Ω)出力コンデンサを、ESRが0.14Ωと大きい品種に変更した場合の負荷応答特性である。出力電圧の変動幅は1.02V〜1.13Vで、ピーク・ツー・ピーク値は約110mVと大きい。

図4 負荷応答特性(ESRは0.01Ω)

図4 負荷応答特性(ESRは0.01Ω)出力コンデンサを、ESRが0.01Ωと小さい品種に変更した場合の負荷応答特性である。出力電圧の変動幅は1.0V〜1.025V。ピーク・ツー・ピーク値は約25mVと小さい。

再び、「Load Transient」のシミュレーションを実行する。その解析結果が図4である。出力電圧の変動幅は1.0V〜1.025Vであり、ピーク・ツー・ピーク値で表すと約25mVである。当初の電源回路は約70mVだったため、リップル成分を約1/3と大きく抑え込むことに成功した。山田氏は、「これだけリップル成分が小さければ、FPGAベンダーが課している制約条件を十分に満足できる」という。従って、今回設計した回路は、FPGAのコア部向け電源回路に適用できる可能性が極めて高いと言えるだろう。

ここで確認のため、ESRが大きな出力コンデンサを採用した場合、出力電圧のリップル成分はどの程度の大きさになるのかをシミュレーションしてみよう。今回は、出力コンデンサの選択肢の中からESRが最も大きな品種を選択する。容量が1000μFで、ESRが0.14Ωのアルミ電解コンデンサである。ESRが最も小さな品種に比べるとESRは14倍と大きい。図5がシミュレーション結果である。出力電圧の変動幅は1.02V〜1.13V。ピーク・ツー・ピーク値は約110mVである。これでは、1V±10%の許容範囲ですら満足できない。

つまり、リップル制御方式を採用した電源ICでは、出力コンデンサのESRを低く抑えることが非常に重要になるわけだ。しかし、出力コンデンサのESRを低く抑えるという対策方法は、すべての電源ICに共通して使えるわけではない。電源ICの制御方式には、リップル制御方式のほかに、電圧制御方式や電流制御方式などがある。山田氏によると、「制御方式にはそれぞれ特徴がある。それらの特徴を把握した上で、それぞれの制御方式に合った対策方法を選択する必要がある」という。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード