LVDSを基礎から理解する(5) LVDS関連製品の賢い選び方(前編):【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】LVDSを基礎から理解する(5) LVDS関連製品の賢い選び方(前編)(クリックで動画再生)

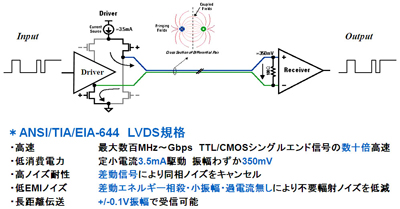

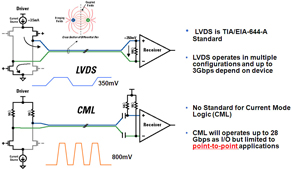

LVDSという名前を知らないエンジニアは少ないだろう。LVDSとは、Low voltage differential signalingの頭文字をとった造語で、3.5mAの定電流源を使用し350mVと非常に低振幅な差動信号を使って高速にデータを伝送するシリアル・インタフェース技術である(図1)。その伝送速度は、ANSIやEIA、TIAでの標準規格において、最大655Mビット/秒と定められているが、実際には1Gビット/秒を超える用途にもこの技術は適用されている。

代表的なアプリケーションとしては、ノート・パソコンやデジタル・テレビの内部で、ロジック・ボードと液晶パネルを接続するインタフェース部が挙げられる。ただし、アプリケーションはこれだけではない。LVDSは高速シリアル通信の基礎的な技術であり、他の高速規格にも参照され、現在では高いデータ伝送速度が求められる用途の多くでLVDSの基本的な技術が適用もしくは参考にされている。

こうした状況に対応すべく、各半導体メーカーではさまざまなLVDS関連製品を多く市場に投入している。例えば、LVDS関連製品の老舗メーカーである米ナショナル・セミコンダクター社では現在、300程度の製品を販売している。これだけ数多く投入されているLVDS関連製品の中から、最適なチップ(IC)をどうやって探し出せばいいのか。それにはまず、どのような製品が入手できるのか、各製品の特徴は何なのか、各製品のメリットとデメリットは何なのか、などのポイントを理解する必要があるだろう。さもなければ、LVDS関連製品を「賢く」選ぶことはできない。

TTL/CMOS信号の伝送距離を簡単に延長

300をも超える製品の中から、最適なチップを探し出す作業は決して容易なことではない。しかし、ナショナル セミコンダクター ジャパンのマーケティング本部でプロダクトマーケティング課長を務める河西基文(かわにし・もとふみ)氏は、「重要なポイントさえ抑えれば、決して困難な作業ではない」という。

そこで重要なポイントを説明するために、数多く存在するLVDS関連製品を3つのカテゴリーに分類することにする。1つめは「LVDSドライバ・レシーバ」。2つめは「LVDSシグナル・コンディショニング」。3つめは「LVDSシリアライザ/デシリアライザ(SERDES)」である。以下で、3つの各カテゴリーについて、それに含まれる製品、その特徴や用途などを説明して行こう。

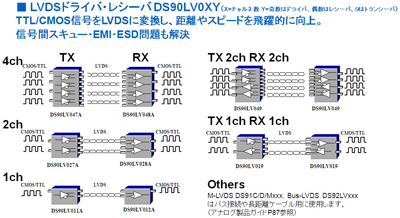

図2 LVDSドライバ・レシーバの使い方

図2 LVDSドライバ・レシーバの使い方TTL/CMOS信号に対応した送信回路の後段にLVDSドライバを、受信回路の前段のLVDSレシーバを置く。こうすることで、伝送速度の向上と伝送距離の延長を実現できる。LVDSドライバ・レシーバは1チャネル品や2チャネル品、4チャネル品などを用意している。

1つめのLVDSドライバ・レシーバは、比較的理解しやすいカテゴリーだといえる。主な役割は、TTLレベルやCMOSレベルの信号を、従来に比べて長い距離、かつ高い速度で伝送することにある(図2)。LVDSドライバをTTL/CMOSレベルの送信側に、LVDSレシーバをTTL/CMOSレベルの受信側に挿入し、差動伝送路を用意するだけで、TTL/CMOSTTL信号を遠く速く飛ばせるようになるわけだ。

差動伝送路については、伝送速度がTTL/CMOSの2倍、もしくは伝送距離が2倍という程度であれば、特別な専用ラインや専用ケーブルを用意する必要はない。伝送速度/伝送距離が2倍程度であれば、レシーバの終端抵抗の調整や必要であれば信号の反射エネルギーを小容量コンデンサで吸収できるようにするだけで、特性インピーダンスの定義のない一般的なケーブルでも使用することができる。

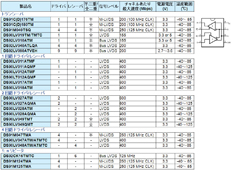

表1は、ナショナル セミコンダクター社が製品化しているLVDSドライバ・レシーバの一覧表である。ドライバとレシーバともに、1回路入り品や2回路入り品、4回路入り品などを用意している。例えば、8ビット幅のTTL/CMOSTTL信号を伝送したい場合は、4回路入りのドライバを2個と、4回路入りのレシーバを2個使えば、設計を大きく変更することなく、TTL/CMOS信号を長距離送れるようになる。

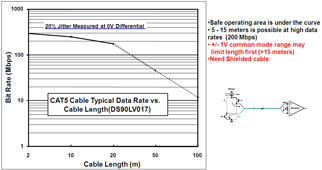

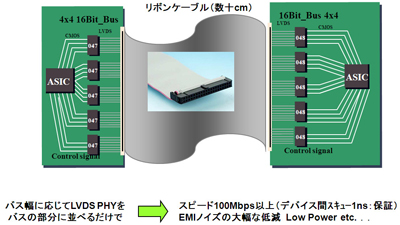

それでは、LVDSの伝送可能な最大速度や最長距離はどの程度なのだろうか。最大の伝送速度については、TTL/CMOS信号の入出力部によって制限を受けるため、実際には400M〜600Mビット/秒程度である。最長の伝送距離は、「イーサネットなどに使われる安価なUTP(AWG24番線を使うCAT6ケーブル)で接続した場合を例にすると、スピードに関係なく伝送可能な距離は15m程度となる。理由としては両側の回路(ボード)のグラウンド電圧差がケーブルによるローパスフィルタ特性よりも先に問題となるためである。」(同氏)という(図3)。

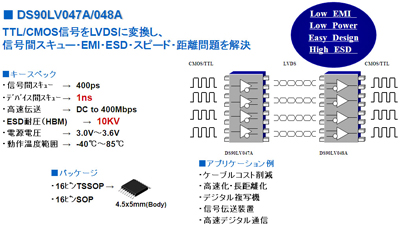

もっとも複数個のドライバを並べて、複数ビットのTTL/CMOS信号を伝送する場合は、ドライバ間のスキューが問題となる危険性がある。スキューが大きければ、それによって伝送距離が制限されてしまう。こうした疑問に対して河西氏は、「同じ型番のドライバを使う場合、同じ電源電圧、同じ周囲温度という条件下であれば、最大のデバイス間スキューはわずかに1ns。1nsという時間は、1GHz信号の1周期分である。従って、60MHzや80MHzといったTTL/CMOS信号を送るのであれば、何の問題もない」と太鼓判を押す(図4、図5)。

図5 LVDSドライバ・レシーバの実使用例

図5 LVDSドライバ・レシーバの実使用例16ビット幅のTTL/CMOS信号を、4チャネルのLVDSドライバを4個と、4チャネルのLVDSレシーバを4個使って、機器間をリボン・ケーブルで接続した例である。比較的距離が長い機器間でも接続できるようになる。

最大で10Gビット/秒にも対応可能

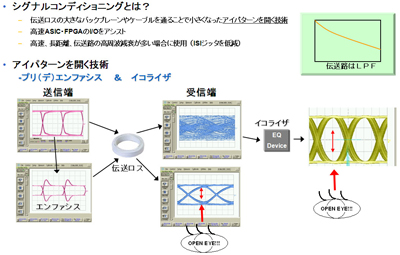

図6 シグナル・コンディショニング技術

図6 シグナル・コンディショニング技術送信回路において高周波成分を増幅することで、受信回路におけるアイ・パターンを大きく開ける技術がプリエンファシス。一方、受信回路において高周波成分を補うことで、アイ・パターンを大きく開ける技術がイコライザである。

2つめのカテゴリーであるLVDSシグナル・コンディショニングは、送信側に向けたプリエンファシス技術やデエンファシス技術、受信側に向けたイコライザ技術を採用した製品群である。主なアプリケーションは、FPGAやASIC、DSPなどを搭載したボードと、ほかのボードとの接続である。FPGAやASICなどには、LVDSなどの差動信号を出力する機能が搭載されているものの、そのままでは高速なデータを長距離送ることはできない。さらに、低価格のFPGAで使われている疑似LVDS信号(定電流源を使わないLVDS信号)では、差動伝送波形が大きく乱れてしまう傾向がある。こうしたケースなどで、FPGAやASICにシグナル・コンディショニング・チップを外付けすれば、従来よりもデータを高速に長距離伝送することが可能になる。もちろん、伝送波形の乱れは少なくなり、受信端での大きなアイ・パターンの開口が得られるようになる。

表2は、ナショナル・セミコンダクター社が市場に投入しているLVDSシグナル・コンディショニング製品の一覧表である。冒頭で説明した通り、ANSIやTIA、EIAの標準規格では、LVDSのデータ伝送速度は最大655Mビット/秒と定められている。しかし、技術的にはそれ以上の伝送速度をサポートすることが可能だ。一覧表をみると、LVDSで最大で3.125Gビット/秒に対応しているシグナル・コンディショニング・チップが複数ある。

ただし一覧表の中には、3.125Gビット/秒を超えるデータ伝送速度に対応したシグナル・コンディショニング・チップも存在している。その理由について、河西氏は「LVDSの技術では約3Gビット/秒程度までの対応となる。それ以上の伝送速度ついては、CML(Current Mode Logic)という別の技術を使用している。CMLを使えば、6Gビット/秒や10Gビット/秒といった伝送速度に対応できるようになる。技術的には、現時点で28Gビット/秒に対応できることも可能」と説明する(図7)。

CMLとはどのような技術なのか。それは次回に詳しく説明しよう。

LVDS関連の資料:

アナログ製品ガイド(2011年4月改訂) のインタフェース・セクション

LVDSオーナーズ・マニュアル第4版:高速CMLとシグナルコンディショニング

Signal Path Designer

#123 産業用ビデオ向けSerDesのEMI問題とシールドの必要性

#122 クロック/制御信号埋め込み型産業機器向けシリアライザ/デシリアライザ

#119 データセンタのサーバやSAN(ストレージ・エリア・ネットワーク)での高速信号駆動

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード