LVDSを基礎から理解する(6) LVDS関連製品の賢い選び方(後編):【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】LVDSを基礎から理解する(6) LVDS関連製品の賢い選び方(後編) (クリックで動画再生)

LVDS関連製品は数多い。米National Semiconductor社では、300を超える半導体チップを製品化している。この中から、設計中の電子機器に最適な品種を選ぶことは決して簡単なことでない。

最適な品種を探し当てるには、各LVDS関連製品の特徴を把握し、理解する必要があるだろう。そこで前編では、それぞれの製品の特徴を説明しやすくするために、LVDS関連製品を3つのカテゴリーに分類した。1つめはLVDSドライバ・レシーバ。2つめはLVDSシグナル・コンディショニング。3つめはLVDSシリアライザ・デシリアライザ(SERDES)である。前編では、1つめのLVDSドライバ・レシーバに加えて、2つめのLVDSシグナル・コンディショニングの一部を解説した。後編となる本稿では、LVDSシグナル・コンディショニングの続き部分から解説を始める。

電圧のエッジ・レートが高いCML

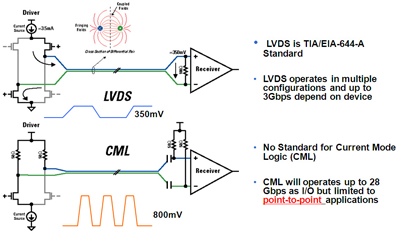

LVDSの伝送仕様を記述したANSIやTIA、EIAの標準規格では、最大データ伝送速度を655Mビット/秒と定めている。しかし、実際にはもっと高いデータ伝送速度にも適用することが可能だ。ナショナル セミコンダクター社では、3.125Gビット/秒に対応したLVDSシグナル・コンディショニング・チップが実用化されている。これ以上、高い伝送速度の領域にはLVDSは適用していない。そこで登場するのがCML(Current Mode Logic)である。

図1 LVDSとCMLの比較

図1 LVDSとCMLの比較LVDSの信号振幅は350mVで、CMLは800mVである。さらに、駆動回路と受信回路の構成も異なる。LVDSは3.5mAの定電流源を使うのに対して、CMLは数十mAの定電流源を使う。このため、エッジ・レート(信号の立ち上がり)が高いので、高速なデータ伝送が可能になる。

LVDSとCMLの最大の違いは、信号振幅とエッジ・レート(電圧の立ち上がり速度)にある(図1)。信号振幅については、LVDSは350mV。一方のCMLは、標準規格が存在しないため厳密な値は存在しないが一般に800mVと大きい。もちろん、信号振幅が大きければ、その分だけ信号の遷移時間がかかる。高速化には不利になるはずだ。CMLではこの問題を、大きな電流で駆動することで解決している。具体的には、LVDSでは、3.5mAと小さい定電流源を使って差動伝送路を駆動しているが、CMLでは、内部の電源電圧(Vcc)レーンに50Ωの終端抵抗を介してトランジスタのコレクタ側を接続する回路構成を採用しており、数十mAと大きな電流源で駆動する方式を採用している。このため、消費電力は大きくなるが、伝送速度を高められることになる。

ただし、CMLを使用する場合には注意すべき点が1つある。それは伝送データのDC(直流)バランスを確保する必要があることだ。「CMLには、標準規格がないため、使用する電源電圧(Vcc)にも規定がない。そのためデバイス間やボード間をAC(交流)結合で接続することが一般的になり、つまり、伝送データのDCバランスの確保が不可欠になるわけだ」(ナショナル セミコンダクター ジャパンのマーケティング本部でプロダクトマーケティング課長を務める河西基文氏)。

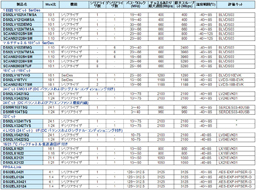

話を、LVDSシグナル・コンディショニング製品の一覧表に移そう(表1)。FPGAやASICなどから出力されたLVDS信号をケーブルや基板上の配線で送る際に、その距離を延ばしたいときは、信号のビット幅に応じて最適なチップを選択すればよい。入力数と出力数ともに、1チャネル品や4チャネル品、16チャネル品などが用意されているため、簡単に選べるはずだ。

ただし、これだけでは選択作業は完了しない。使用するシグナル・コンディショニング技術を決めなければならないからだ。一般にエンファシスとイコライザのどちらを使うかについては、必要な高周波成分の増幅量に依存する。伝送路の高周波の減衰が少ないなどの高周波成分をあまり増幅する必要がなければエンファシスを、長いケーブルなどで高周波の減衰が大きい場合は、大きく増幅するイコライザを使うべきである。具体的には、伝送路の基本周波数の減衰が6〜10dB程度であればエンファシス、10dBを超える場合はイコライザを使用する。さらに、20dB以上のような大きな減衰の場合は、エンファシスとイコライザの両方を使用し、より安定した長距離信号伝送も可能となる。

エンファシスやイコライザで必要な増幅量は、信号伝送で使用する周波数帯域や、シグナル・コンディショニング・チップを適用する伝送路で異なる。つまり、使用するコネクタやケーブル、プリント基板上の配線で大きく違うわけだ。多くの場合、必要な増幅量は設計段階では未知である。このため、河西氏は「エンファシスやイコライザで増幅量は、使用する差動伝送路(ケーブルや基板)の特性(挿入損失など)を実際に測定することがまず基本となる」と指摘する。

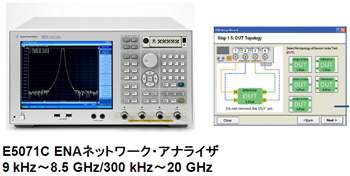

差動伝送路の測定は決して難しくない。従来は、差動伝送路の伝送特性を測定するには、専用の計測器を用意するだけでなく、正確なセットアップを実行する必要があった。しかし最近では、差動伝送路の測定に向けた4端子回路網対応のネットワーク・アナライザが用意されており(図2)、測定手順を解説したガイダンス機能などが搭載されているため、デジタル分野のエンジニアでも比較的簡単に測定できるようになっている。

こうした計測器が手元にない場合はどうすればいいのか。同氏は、2つの方法を薦める。「1つは、当社が提供している『LVDSオーナーズ・マニュアル』に掲載されている、ケーブルの銅線の太さに応じた減衰量などを参考にする方法である。このデータを使えば、実際に使用するケーブルの減衰量を類推できる。もう1つは、ケーブルやコネクタにメーカーに、伝送路のSパラメータ(減衰・反射)のデータ提供を依頼する方法である」(同氏)。

エンベデッド・クロックを採用

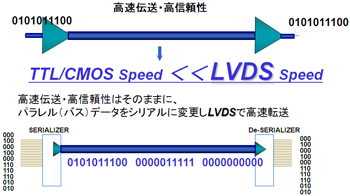

最後に3つめのカテゴリーであるLVDSシリアライザ・デシリアライザについて解説しよう。このカテゴリーのチップの用途は、10ビットや16ビット、18ビット、24ビット、32ビットなどのパラレル信号を、1対もしくは複数対のシリアル信号に束ねて伝送することにある(図3)。言い換えれば、パラレル信号を長距離伝送することに向けた製品群といえるだろう。SERDESチップは、パラレル信号をシリアル信号に、シリアル信号をパラレル信号に変換する際に使う。

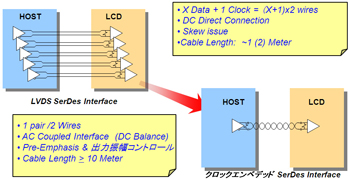

このカテゴリーの製品群には大きく2つの特徴がある。1つは、最新製品ではLVDS信号、もしくはCML信号の中にクロック信号の情報を埋め込んでいることである(図4)。つまり、エンベデッド・クロックを採用しているわけだ。従って、従来のようにクロック信号と別途、パラレルで送る必要がない。しかも、データ信号とクロック信号の間のスキューは物理的に存在しない。

図4 エンベデッド・クロック

図4 エンベデッド・クロック2000年以降に発売されたLVDSシリアライザ・デシリアライザでは、LVDS信号の中にクロック信号を埋め込むエンベデッド・クロックを採用している製品が多くなっている。これら製品では、従来よりも長距離のデータ伝送が可能になっている。

もう1つの特徴は、データ信号とクロックの間にスキューが存在しないため、エンファシスやイコライザを使うことで、長距離伝送や高速伝送が可能になることである。このため、特殊なLVDS専用ケーブルを使う必要はない。CAT6やUSB・SATA・HDMIなどの安価な汎用ケーブルも利用できる。

このカテゴリーの製品一覧表が表2である。入力信号と出力信号のバス幅と、バスのクロック周波数が把握できていれば、おのずと最適なチップが決まる。例えば、ナショナル・セミコンダクター社の「Channel Link II」では、24ビットのデータ入力信号、3ビットの低速制御信号、クロック信号を1本のシリアル信号に束ねて約10mの距離を伝送することができる(図5)。対応するバスのクロック周波数は10M〜75MHzである。バス信号の高速・長距離伝送のほかに産業用ディスプレイでの画像データ伝送などにも使える。

図5 LVDSシリアライザ・デシリアライザの製品例

図5 LVDSシリアライザ・デシリアライザの製品例米ナショナル セミコンダクター社のLVDSシリアライザ・デシリアライザの製品例「Channel Link II」である。バス信号の高速・長距離伝送のほかに産業用ディスプレイなどで、24ビットの画像データを伝送する用途でも使える。

LVDS関連の資料:

アナログ製品ガイド(2011年4月改訂) のインタフェース・セクション

LVDSオーナーズ・マニュアル第4版:高速CMLとシグナルコンディショニング

Signal Path Designer

#123 産業用ビデオ向けSerDesのEMI問題とシールドの必要性

#122 クロック/制御信号埋め込み型産業機器向けシリアライザ/デシリアライザ

#119 データセンタのサーバやSAN(ストレージ・エリア・ネットワーク)での高速信号駆動

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード