LVDSを基礎から理解する(6) クロック埋め込み対8B10B(その2):【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】LVDSを基礎から理解する(6) クロック埋め込み対8B10B(その2) (クリックで動画再生)

ThunderboltやDisplayPort、USB3.0、HDMI、シリアルATA、PCI Express、LVDSなど、高速シリアル・インターフェースにはさまざまな規格や仕様が存在する。こうした規格や仕様を細かく見ると、2つの大きな違いがあることに気付く。

1つは接続方法である。AC結合、もしくはDC結合のいずれかを採用している。ただし、最近策定された高速シリアル・インターフェースは、そのほとんどがAC結合を使う。もう1つの違いは、そのAC結合を実現する方法である。AC結合では、伝送するデジタル信号に直流成分が含まれていると、正確なデータ伝送が困難になる。そこで、この直流成分を排除するシリアル・コーディング技術が不可欠だ。高速シリアル・インターフェースで採用されているシリアル・コーディング技術は2つある。1つは8B10B方式。もう1つはクロック埋め込み(エンベデッド・クロック)方式である。

前回は、AC結合とDC結合について説明した。そこで今回と次回の2回にわたって、8B10B方式とクロック埋め込み方式について詳細を説明しよう。

1982年に開発される

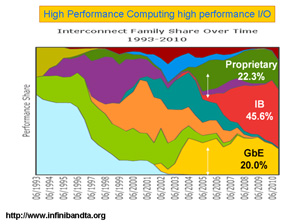

図1 8B10B方式とクロック埋め込み方式の市場占有率

図1 8B10B方式とクロック埋め込み方式の市場占有率ハイパフォーマンス・コンピューティング(HPC)における市場占有率である。8B10B方式を採用するインフィニバンド(IB)が45.6%、クロック埋め込み方式を採用する10GビットEthernet(GbE)が20.0%を占める。各社独自のプロプラエタリィ方式の市場占有率は22.3%である。

まず、8B10B方式とクロック埋め込み方式の説明に入る前に、ハイパフォーマンス・コンピューティング(HPC)市場で、どのような高速シリアル・インターフェースが使われているかを確認しておく。InfiniBand Trade Association (IBTA)の資料によると(図1)、8B10B方式を使うインフィニバンド(Infiniband)と、クロック埋め込み方式を使う10GビットEthernet 10Gbase-R、各社独自のプロプラエタリィ方式がそれぞれ約1/3ずつ市場を分け合っていることが分かる。つまり、現時点において、8B10B方式とクロック埋め込み方式が、高速シリアル・インターフェース市場における主要なシリアル・コーディング技術と言えるそれでは、最初に8B10B方式について説明する。8B10B方式は、8ビット長のデータを10ビット長のデータに変換することで、直流成分を排除するシリアル・コーディング技術である。その歴史はかなり古い。開発したのは米IBM社で、今から約30年前の1982年に特許を申請した。その当時は、テープやフロッピー・ディスクなどの記憶装置への適用に向けて開発されたようだ。現在では、通信インフラ装置やスーパー・コンピュータ、光ファイバ通信装置といった高速通信アプリケーションに使われている。従って、信頼性の高いシリアル・コーディング技術だと言える。

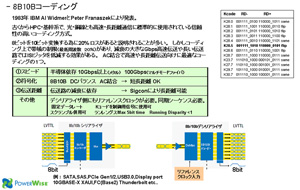

8B10B方式のコーディング方式は、以下の通りだ。まずは、上位3ビットと下位5ビットに分けて、それぞれに対して3B4B変換、5B6B変換を実行する(図2)。これらの変換には、決まった法則はない。いずれも、あらかじめ用意されたテーブルに使って、データをシンボルへと変換する。各シンボルは、プラス(+)とマイナス(−)の2種類が存在する。これを利用することで、ランニング・ディスパリティ(RD:running disparity)の0と1の差を±1以内に収めることを保証している。具体的には、直前のランニング・ディスパリティがプラスならば、次はマイナスのシンボルを、直前がマイナスならば、次はプラスのシンボルを出力する。こうして、「0」や「1」が5ビット以上連続しないようにするとともに、DCバランスを確保している。

レシーバがデータを受け取る際に必要となるクロック信号は、ドライバから送られてくるこの伝送データに埋め込まれていない。このためドライバは、レシーバに対して定期的に制御コード(K28.5 コンマキャラクタ)を送る必要がある。レシーバは、この制御コードを受け取ることで、レシーバに搭載したリファレンス・クロックをベースに同期を行い、その後この内部同期クロックを使って伝送データを受信する。

20%のオーバーヘッドは、実はメリット

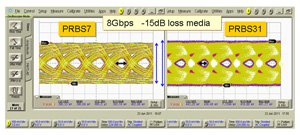

図3 低周波帯域制限の効果

図3 低周波帯域制限の効果8B10B方式では、20%のオーバーヘッドが存在する。しかしこのコード変換により、低周波帯域を制限できるため、ISIジッタが低減しアイの開口を確保しやすくなる。左図が8B10B方式に採用して伝送した場合、右図はそのまま伝送した場合である。左図の方がアイが大きく開いている。

8B10B方式のメリットとデメリットは何なのだろうか。LVDS関連製品のマーケティングを担当する河西基文氏は、「8B10B方式では、8ビットを10ビット信号として送るため20%のオーバーヘッドがある。この事実に対して、多くの人がデメリットだと理解しているようだが、実際の8B10Bコーディングには大きなメリットがある」と指摘する。

確かに、8ビットのデータを送るのに10ビットを使っているため、2ビットが余分になる。しかし、この2ビットのおかげで、シンボル間干渉(ISI:Inter Symbol Interference)ジッタを低減している。8B10Bシリアル・コーディングを実行することで20%以下の低周波成分が排除されるため、低周波側の帯域を制限できるためだ。従って、高速データを長距離伝送する場合、アイの開口を比較的確保しやすくなり、10Gビット/秒を超えるような高速のデータ伝送にうまく対応できることになる(図3)。

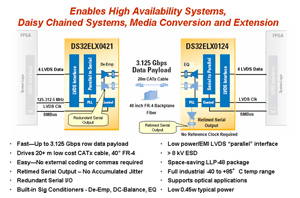

図4 8B10B方式を採用した高速シリアル・インターフェースICの例

図4 8B10B方式を採用した高速シリアル・インターフェースICの例「FPGA-Link」と呼ぶ製品である。ドライバICとレシーバICから構成されており、型番は「DS32EL(X)0421/0124」。最大3.125Gビット/秒のデータを、より対線ケーブルを使って約20m伝送できる。

デメリットとしては、レシーバ(受信)側にもドライバ(送信)側と同じ高精度リファレンス・クロックが必要なことと、同期コードを定期的に送信するプロトコルを実装しなければならないことが挙げられる。

8B10B方式を採用した高速シリアル・インターフェースICは数多くあるが、ここでは「FPGA-Link」という製品を紹介しよう(図4)。型番は「DS32EL(X)0421/0124」である。DDR(double data rate)形式の4本のLVDS信号、すなわち8ビットでデータを8B10B方式でシリアル・コーディングすることで1本の差動線路で伝送するドライバICとレシーバICである。データ伝送速度は最大で3.125Gビット/秒。ドライバICにデエンファシス機能、レシーバICにイコライザ機能を内蔵しているため、伝送距離はより対線ケーブル(AWG24番線)を使った場合に20m程度が得られる。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード