オンライン設計支援ツールの使い方(1) WEBENCH®ツールの新機能を理解する:【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

オンライン設計支援ツールの使い方(1) (クリックで動画再生)

米テキサス・インスツルメンツ(TI)社がインターネット経由で、無償で提供するオンライン設計支援ツール「WEBENCH® Designer」。提供している機能は豊富だ。電子機器で使用するアナログICの選定/絞り込み機能のほか、回路設計機能、動作シミュレーション機能、購買機能などを備えている。対象となるアナログICは、電源ICがメインであるが、LEDドライバIC、A-D/D-A変換器IC、オペアンプIC向けとしても機能限定ではあるが、サポートしている。

本ビデオ講座では、WEBENCH Designerの電源回路設計機能に焦点を当て、2010年と2011年に「電源回路設計の手順と勘所」というタイトルで、ツールの基本的な仕組みや使い方、機能などを解説した。それから1年弱経過した。その間に、新機能が追加されるなど、使い勝手がより一層向上している。そこで今回は、新機能の紹介のほか、より深い使い方について解説していく。

二つの新機能を追加

過去、1年弱の間に追加された新機能は二つある。いずれもFPGAとマイクロプロセッサに向けた電源回路設計ツールである「WEBENCH FPGA Power Architect」と「WEBENCH Processor Power Architect」に追加されたものだ。

一つは、電源シーケンスの設定が可能になったことである。2011年のビデオ講座の際は、ツール自体に電源シーケンスに関する表示があったものの設定できない状態(N/A)になっていた。今回、それが利用可能になったわけだ。

FPGAやマイクロプロセッサにとって、電源シーケンスは大きな問題の一つである。コア部と入出力インターフェイス(I/O)部の電源投入、電源切断の順番を間違えるとラッチアップを起こすというトラブルに見舞われるからだ。しかし最近では、FPGA自体で電源シーケンスの問題をソフトウエア的に解決できるようになっており、従来に比べると電源シーケンスの重要性が低くなっているという見方もある。

この見方に対して、日本TIで電源IC関連のマーケティングを担当する山田浩二氏は、こう述べる。「確かに、最近のFPGAの中には、シーケンス・フリーをうたう製品が増えている。具体的には、チップの内部で電源シーケンスを組んで、電源の投入と切断を管理している。この機能を使えば、電源シーケンスに関する問題を解決できるケースも多いが、すべての製品で対応出来ている分けでも無い。そうした場合は、従来同様外部の電源回路でシーケンスを組む必要がある」(同氏)。

オンライン設計支援ツールにおいて電源シーケンスを設定すると、それに適合した電源ICが選択されるようになる。具体的には、イネーブル機能やパワーグッド信号出力機能を備える電源ICが選択の対象になるわけだ。

追加されたもう一つの新機能は、LDO(low dropout)レギュレータICの強制配置機能が備わったことだ。従来は、スイッチング・レギュレータICしか使用できなかった。

なぜ、LDOレギュレータICが必要なのか。理由はノイズにある。例えば、FPGAにはアナログ回路ブロックやPLL回路が集積されたものがある。こうした回路はノイズを嫌うからだ。新機能を使えば、ノイズを嫌う回路への電力供給には、LDOレギュレータICの使用を強制配置することができる。

電源シーケンスを簡単に設定できる

それでは、実際にWEBENCH Designerを使いながら、二つの新機能を確認していく。

WEBENCH Designerは、日本TIのホームページから利用できる。画面の右端にあるボックスが入り口となっている。このボックスで、「FPGA/μP」のタブをクリックすると、FPGAとマイクロプロセッサの選択肢が表示される。今回はFPGAベンダーである米アルテラ(Altera)社を選択し、設計を行う。「FPGA Architect」ボタンを押すと設計画面へと移行する。

まずは、設計対象となるFPGAを選択しよう。今回は、「Stratix-? GT」の中から「EP4S100GS」を選んだ。ここで画面右端にある「負荷を追加」ボタンを押すと、設計対象のFPGAに電力を供給する必要がある各負荷の詳細設定画面が表示される。今回のケースでは、36個の負荷の情報が表示されている(図1)。

ここで、電源シーケンスを設定してみる。各負荷の設定パネルの中央部にある「Sequence」という表示をクリックすると、図2のような画面が表示される。この画面では必要に応じて、電源電圧の投入、もしくは切断のタイミングを任意に設定することが可能だ。具体的には、投入/切断のタイミングをマウスでつまみ、左右に動かすことで希望する電源シーケンスを実現できる。

LDOレギュレータICの適用については、各負荷の設定パネルに設けられている「LDO Supply」のボックスにチェックを入れるだけでよい(図3)。これだけで、その負荷に電力を供給する電源回路がLDOレギュレータICとなる。

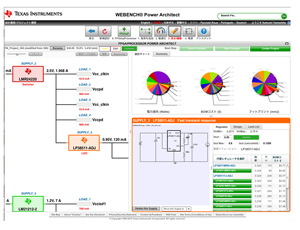

各負荷の詳細設定が終わったら、画面右端の「プロジェクト要件を送る」ボタンを押すと回路設計が始まる。得られた電源回路構成が図4である。ここで、画面右端の「Sequence」ボタンを押すと、指定した通りに電源シーケンスが構成されているかどうかを確認できる(図5)。LDOレギュレータICの使用については、画面右端の「設計の詳細を見る」ボタンを押し、次の画面で各電源ICの詳細を見ることで確認できる(図6)。

図6 使用する各電源ICの詳細を確認

図6 使用する各電源ICの詳細を確認「設計の詳細を見る」ボタンを押し、表示された画面を見ることで、使用する各電源ICの詳細を把握できる。つまり、LDOレギュレータICが使われているかどうかを確認できるわけだ。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード