高速伝送用シグナル・コンディショナ(後編) 四つの機能で高速化と長距離伝送を可能に:【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】高速伝送用シグナル・コンディショナ(後編) (クリックで動画再生)

日本テキサス・インスツルメンツ(TI)は2012年2月1日に、シグナル・コンディショナICの新製品を市場に投入した。投入した製品は全部で10品種ある。いずれの品種も特徴は三つある。すなわち、性能が高い点と消費電力が低い点、使い勝手が高い点の三つだ。

例えば、性能については、最大12.5Gビット秒の信号を、FR-4基板上のバックプレーンで約1.3m、AWG24ケーブルで約20m伝送することが可能だ。消費電力については、競合他社品の約半分と非常に低い。主なアプリケーションは、高い性能と低い消費電力が特に強く求められるサーバーやスイッチ、ルーター、ストレージといったデータ・センタ向け電子機器である。

CDR機能を搭載

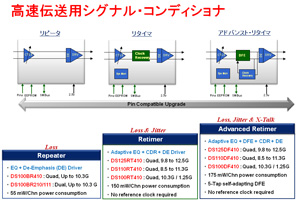

図1 高速伝送用シグナル・コンディショナ

図1 高速伝送用シグナル・コンディショナ大きく三つの品種に分類できる。このうち今回日本TIは、リタイマICとアドバンスト・リタイマICを新たに製品化した。リピータICはすでに、2011年に市場に投入している。

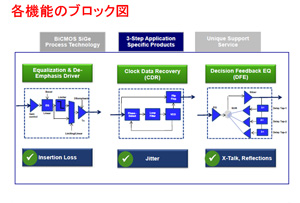

今回は、10品種のうち6品種に絞って、その詳細を説明していこう。発売したシグナル・コンディショナICは、搭載している機能の違いで大きく三つの種類に分けられる。すなわち、リピータICとリタイマIC、アドバンスト・リタイマICである(図1)。この中で、最も機能がシンプルなのがリピータICである。イコライザ(EQ)とデエンファシス・ドライバ(DE)という二つの機能で構成されている(図2)。イコライザとは、伝送路を通過することで失った信号振幅を、その伝送路の周波数特性に基づいて受信端で増幅(ブースト)するという機能だ。信号が伝送路を通過すると、その高周波成分が大きく減衰してしまう。そのため受信回路において、減衰してしまった高周波成分を増幅し、元の状態に戻す。一方、デエンファシス・ドライバは、伝送路で減衰してしまう高周波成分に合わせて、送信回路(ドライバ)であらかじめ低周波成分を削ってから伝送するという機能である。受信回路では、低周波成分も高周波成分も同様に減衰するため、波形の乱れは小さくなる。

図2 各機能のブロック図

図2 各機能のブロック図左はイコライザとデエンファシス・ドライバの機能ブロック図。挿入損失を補償できる。中央は、クロック抽出(CDR)の機能ブロック図。ジッタの補償に向ける。右は、判定帰還型等化器(DFE)の機能ブロック図で、クロストークなどの影響を除去できる。

日本TIはリピータICとして、「DS100BR410」と「DS100BR210/111」を製品化している。しかし、「この2品種は昨年(2011年)に製品化したもので、今回の6品種には含まれていない」(同社でシグナル・チェーン関連のマーケティングを担当している結城靖夫氏)という。

次に機能が多いのがリタイマICである。アダプティブ(自動調整)機能を搭載したイコライザとデエンファシス・ドライバに、クロック抽出(CDR:Clock and Data Recovery)を加えた三つの機能で構成したものである。クロック抽出は、PLL(Phase Locked Loop)回路を利用して、送られてきた信号の中からクロック成分を抽出する。そして、このクロックで送られてきた信号をたたき直す。イコライザとデエンファシス・ドライバは、信号の振幅方向を補償する機能だが、クロック抽出は時間方向を補償する機能である。すなわち、振幅の損失とジッタの両方を補償できるわけだ。

市場に投入した製品は、「DS125RT410」と「DS110RT410」、「DS100RT410」の三つである。いずれも、入出力のチャネルを四つ備えるクアド(Quad)品である。3品種の違いは、対応するデータ伝送速度にある。DS125RT410は、9.8Gから12.5Gビット/秒、DS110RT410は8.5G〜11.3Gビット/秒、DS100RT410は10.3Gビット/秒と1.25Gビット/秒に対応する。消費電力はチャネルあたり150mWである。

クロストークの影響を除去

製品化した3種類のシグナル・コンディショナICの中で、機能が最も多いのがアドバンスト・リタイマICである。リタイマICに搭載したアダプティブ・イコライザとデエンファシス・ドライバ、クロック抽出に加えて、判定帰還型等化器(DFE:Decision Feedback Equalizer)を搭載した。

DFEとは、クロストークなどを原因とする信号の乱れを抑える機能である。入力信号の一部をフィードバックし、それに一定の時間遅れを持たせた上で、ある係数を掛けて、入力信号に重ね合わせる。こうした処理を実行することで、信号の乱れを抑える。発売したICには、一定の時間遅れを持たせ、係数を掛けて重ね合わせる回路を五つ用意した。一般にこの回路をタップと呼ぶ。従って、5タップ構成のDFEを採用したことになる。「一般に、タップ数が多ければ、信号の乱れを抑制する効果が大きくなる。5タップも用意すれば、十分な効果が得られる」(結城氏)。

市場に投入した製品は、リタイマIC と同様に三つである。具体的には、「DS125DF410」と「DS110DF410」、「DS100DF410」である。いずれもクアド品。違いは、対応するデータ伝送速度にある。DS125DF410は、9.8Gから12.5Gビット/秒、DS110DF410は8.5G〜11.3Gビット/秒、DS100DF410は10.3Gビット/秒と1.25Gビット/秒に対応する。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード