性能向上が続くLDOレギュレータ、 高PSRR品や高速過渡応答品が新登場:【講座】回路設計の新潮流を基礎から学ぶ

LDO(Low Dropout)レギュレータの実現技術はすでに成熟しており、もはや性能向上はあまり期待できない――。そう認識しているエンジニアは、決して少なくないだろう。しかし、その認識は間違いである。LDOレギュレータの性能は今もなお、アプリケーションの進化に対応すべく高まり続けている。実際に、どのような性能が高まっているのか。本稿では、従来に比べて性能を大幅に向上させた二つの最新製品を紹介しよう。

低ノイズが最大の特長

まずはLDOレギュレータについて、簡単におさらいしておこう。LDOレギュレータとは、パス・トランジスタの抵抗分によって、入力電力を強制的に消費させることで希望する出力電圧に変換して出力する電源回路である。リニア・レギュレータの一種だ。リニア・レギュレータの中で、入力電圧と出力電圧の差が小さい品種をLDOレギュレータと呼ぶ。入力電圧を消費して、ある出力電圧に変換するため、出力電圧は入力電圧よりも必ず低くなる。従って、昇圧型や昇降圧型は実現不可能であり、降圧型のDC-DCコンバータしか実現できない。

LDOレギュレータの最大のメリットは、出力電圧に含まれるリップル成分が小さいことである。パス・トランジスタのオン抵抗で消費させて、希望する出力電圧に変換する方式を採用しているからだ。このため、入力電圧に大きなリップル成分が重畳されていても、出力電圧に現れるリップル成分を極めて低く抑えることが可能になる。このほか、回路構成が比較的単純なため、低価格な上に使い方が簡単で、プリント基板への実装面積が小さいこともメリットとして挙げられるだろう。

一方でデメリットもある。最大のデメリットは変換効率が低いことで、入力電圧と出力電圧の差が大きいと極めて低くなる。

メリットを生かし、デメリットを補う

LDOレギュレータには、出力のリップル成分が小さいというメリットがあるものの、変換効率が低いという大きなデメリットがある。従って、LDOレギュレータを有効に活用するには、メリットを生かしながら、デメリットを補う必要がある。

そうした活用方法の代表例が、前段にスイッチング・レギュレータ、後段にLDOレギュレータを配置するというものだ。すなわち、LDOレギュレータを「ポスト・レギュレータ」として使う。スイッチング・レギュレータは、LDOレギュレータとはまったく正反対の特性を持つ。高い変換効率が得られるものの、出力のリップル成分は大きい。そこで、前段のスイッチング・レギュレータを使って、高い入力電圧を、必要とする出力電圧よりも少し高い値に変換する。そしてLDOレギュレータで、リップル成分を除去しながら、必要とする出力電圧に変換して出力する。

この活用方法であれば、高い変換効率と低い出力リップルを同時に実現できる。すでに、さまざまなアプリケーションで使われている。具体的には、無線通信機器や医療用電子機器、産業用電子機器などにおいて、リップルやノイズに敏感なアナログ回路への電源供給で利用されている。

スイッチング・レギュレータの高周波化に対応

スイッチング・レギュレータを前段に、LDOレギュレータを後段に配置する。お互いのデメリットを補い合うという点で、まさに理想的な組み合わせである。

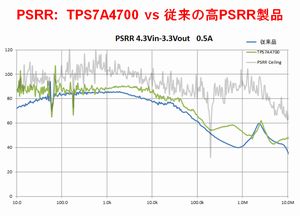

しかし、最近になって、この活用方法に一つの問題が浮上してきた。それは、前段に置くスイッチング・レギュレータの高周波化だ。「これまで、スイッチング周波数は500kHz以下が主流だったが、最近は1MHzに近い周波数で使用するケースも出てきている」(日本テキサス・インスツルメンツの北野智麗氏)。LDOレギュレータのリップル除去性能、すなわちPSRR(Power Supply Rejection Ratio)には周波数依存性がある。一般に、低い周波数におけるPSRRは高いものの、周波数が高まるとPSRRが低下する傾向にある。「10年前に製品化されたLDOレギュレータは、100kHzの周波数領域ではPSRRが0dBに近いものも少なくなかった」(同氏)という。

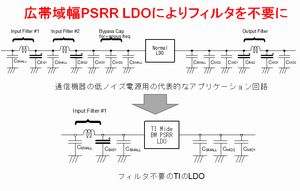

そこで米テキサス・インスツルメンツ(TI)社は、高い周波数におけるPSRRを大幅に向上させたLDOレギュレータIC「TPS7A4700」を製品化した(図1)。1MHzにおけるPSRRは、約50dBと極めて高い(図2)。「業界トップクラスの性能を実現した」(同氏)という。入力電圧に高周波の大きなリップル成分が含まれていても、このLDOレギュレータを使えば、出力電圧をほぼフラットにできる。そのため、外付けのLCフィルタなどの電源リップルフィルタを大幅に削減可能だ(図3)。

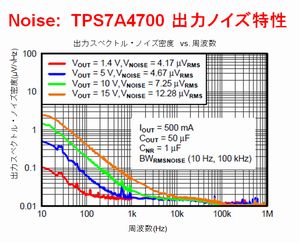

さらに、発売したLDOレギュレータICにはもう一つの特長がある。それは、LDOレギュレータ自身で発生するノイズも極めて低いことだ。10Hz〜100kHzにおける出力電圧ノイズは4.67μVrms(5V出力時)と低く、なおかつ出力電圧依存性が低いため、一般的なLDOレギュレータと異なり高い出力電圧でも出力ノイズを抑制できる(図4)。同社従来の低ノイズ品は5V出力時には80μVrmsとなり、5V出力時では約1/17に削減した計算になる。

図4 出力電圧ノイズも大幅削減

図4 出力電圧ノイズも大幅削減「TPS7A4700」では、LDOレギュレータ自身が発生するノイズも大幅に削減した。例えば、10Hz〜100KHzにおける出力電圧ノイズは4.17μVrms(1.4V出力時)と小さい。

PSRRの向上と出力電圧ノイズの削減を実現できた技術的なポイントは、回路設計技術の工夫だけではない。例えば、基準電圧源(リファレンス)の低ノイズ化などである。また半導体製造プロセスにもある。採用したのは、バイポーラ製造技術である。この技術自体は決して新しいものではないが、改良を加えることでPSRRの向上と出力電圧ノイズの削減を達成した。

ただし、「一つの工夫で大幅な進化を達成したのではなく、さまざまな工夫の積み重ねで実現した」(同氏)と説明している。

TPS7A4700の入力電圧範囲は3〜35Vで、出力電圧は1.4〜20.5Vである。出力電圧の設定に外付け抵抗は不要だ。複数端子の設定だけで出力電圧を希望する値に決定できる。最大出力電流は1A。ドロップアウト電圧(入出力電圧差)は1A出力時に307mV。出力電圧精度は±1.0%である。パッケージは20ピンVQFN。1000個購入時の参考単価は2.10米ドルからである。

このほか、負電圧に対応したLDOレギュレータ「TPS7A3301」も用意している。TPS7A4700に比べると、PSRRと出力雑音ノイズは若干劣るものの、「負電圧対応のLDOレギュレータとしては業界トップレベルの水準」(同氏)という。入力電圧範囲は−3〜−36Vで、出力電圧は−1.18〜−33V。最大出力電流は1A。ドロップアウト電圧(入出力電圧差)は1A出力時に325mV。出力電圧精度は±1%。PSRRは100kHzにおいて52dB。出力電圧ノイズは、10Hz〜100kHzにおいて16μVrms(Vout=Vref時)である。パッケージは20ピンVQFNと7ピンTO-220。1000個購入時の参考単価は2.70米ドルからである。

高速なFPGAにも対応

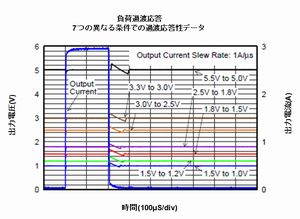

LDOレギュレータの性能を大幅に向上させた二つめの具体例を紹介しよう。それは、TI社が製品化している、過渡応答特性が極めて高いLDOレギュレータ「TPS7A7300」である(図5)。

高い過渡応答特性が求められる背景には、FPGAやマイクロプロセッサ、ASICといったデジタルLSIの高性能化がある。デジタルLSIは、動作状態に応じて負荷電流が大きく変化する。その際に、出力電圧を大きく変動させるわけにはいかない。変動幅が大きいと、デジタルLSIがリセットしたり、ラッチアップしたりする事態を招くからだ。従って、LDOレギュレータには、負荷変動に対して高速に追随する性能が求められるわけだ。

同社によると、「約10年前に製品化されたLDOレギュレータで高い過渡応答特性を実現するには、100μFの出力コンデンサを接続する必要があったが、この当時のコンデンサはESRが高くESRによる電圧ドロップが問題となっていた」(同社の北野氏)という。従って、TPS7A7300では過渡応答特性の向上に伴い小容量キャパシタで高い応答性を実現できるようになったので低ESRのセラミック・コンデンサを使用可能になっており、ESRによる電圧低下の低減も含めた高速負荷応答を実現した。出力コンデンサの容量は10μFで済むので、かなり大きな技術的な飛躍だと言えるだろう。

TPS7A7300の入力電圧範囲は1.5〜6.5V。出力電圧は0.9〜5.0Vの範囲で、複数端子の設定で調整でき、外付け抵抗は不要だ。出力電流は最大3A。ドロップアウト電圧は3A出力時に240mV。パッケージは、実装面積が5mm×5mmの20ピンQFNである。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード