JESD204B:これだけは知っておきたいアナログ用語

JESD204B

JESD204Bは、通信機器、医療機器、計測/テスト機器などの分野で需要が増加している高速A/Dコンバータ、D/Aコンバータを、FPGA、DSP、ASICなどの高速ロジック・デバイスに接続するためのシリアル・インターフェイス規格である。米国の標準化団体であるJEDECが策定した。

JESD204Bの概要

A/Dコンバータ、D/Aコンバータのデジタル・インターフェイスには、低速用途ではSPI、I2Cやメーカ独自のシリアル・インターフェイスが普及していたが、高速用途ではCMOS、LVDSなどのパラレル・インターフェイスが用いられていた。だが、パラレルでは信号線の本数が多いためボード上の実装面積が大きく、高速になるほどレイアウトも困難になる。そこで、JEDECでは高速データ・コンバータ向けのシリアル・インターフェイス規格の標準化を進め、2006年にJESD204規格を発表した。その後、2008年にJESD204A、2011年にJESD204Bと改訂版が登場している。

| 規格 | 発表 | 最大信号レート | マルチレーン | レーン間同期 |

|---|---|---|---|---|

| JESD204 | 2006年 | 3.125Gbps/レーン | なし | なし |

| JESD204A | 2008年 | 3.125Gbps/レーン | あり | あり |

| JESD204B | 2011年 | 12.5Gbps/レーン | あり | あり |

表1 JESD204、JESD204A、JESD204Bの比較

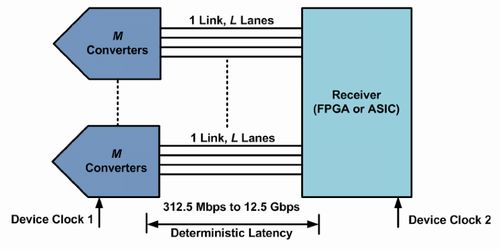

最新版のJESD204Bでは、1レーンあたり312.5Mbpsから12.5Gbpsまでの信号レートがサポートされ、レーンを束ねることにより信号レートをさらに高速化できる。また、コンバータ同期のためのフレーム・クロックに加えて、より柔軟なデバイス・クロックが規定された。サンプリングからデジタル・データ出力までの遅延時間を制御するdeterministic delayの機能も追加され、複数のコンバータのタイミング管理がきわめて容易になった(図1)。

図1 JESD204Bの概要

図1 JESD204Bの概要JESD204BはA/Dコンバータ、D/AコンバータをFPGAなどの高速ロジック・デバイスに接続するためのシリアル・インターフェイス規格。1レーンあたり最大12.5Gnps、複数レーンをまとめることでさらに高速化も可能だ。

JESD204Bの普及

JESD204を用いればボード上の配線を大幅に削減できることから、高速データ・コンバータやFPGAのメーカを中心に普及が進んでいる。旧バージョンのJESD204、JESD204Aも、配線の削減による低コスト製品で広く利用されている。一方、最新のJESD204Bに対応する高性能製品も登場している。

例えば、テキサス・インスツルメンツ(TI)社のADS42JB69は、最大3.125Gbpsで4レーンの伝送が可能なJESD204B対応のシリアルA/Dコンバータである。2チャネル16ビット同時サンプリングで250Mspsという超高速を実現している。

これだけは知っておきたいアナログ用語 バックナンバー

- DC-DCコンバータ

- スイッチング周波数

- POLコンバータ

- 同期整流

- LED駆動における直列接続と並列接続

- LED駆動と位相調光

- PWMとPFM

- 電源トポロジー

- EMI

- 特性インピーダンス

- SSCG

- コモン・モード雑音

- パワーMOSFET

- リニア・レギュレータ

- 電源シーケンス

- インダクタ

- コンデンサ

- 電源回路の制御モード:電圧モード制御、電流モード制御、リップル制御

- 熱抵抗

- オペアンプ

- A-Dコンバータ

- 計装アンプ

- パッシブ・フィルタ

- アクティブ・フィルタ

- ジッタ

- 8B10B

- 挿入損失(インサーション・ロス)と反射損失(リターン・ロス)

- AC結合とDC結合

- SDIとは

- プログレッシブとインターレース

- 差動プローブ

- プリエンファシスとデエンファシス

- イコライザ

- ヒステリシス制御方式

- コンスタント・オンタイム制御方式

- ECM

- ホットスワップ

- AWG

- クロック・データ・リカバリ

- LVDS

- アイ・ダイアグラム

- USB3.0

- フライバック方式

- 力率改善回路(PFC)

- MEMS

- KGD

- D-Aコンバータ

- 中間周波数

- SEPIC(セピック)

- スイッチング・レギュレータ

- ハプティクス(触感フィードバック)

- 圧電素子(ピエゾ素子)

- PSRR(電源電圧変動除去比)

- 負荷過渡応答

- FOD(異物検出機能)

- WPC(ワイヤレスパワーコンソーシアム)

- JESD204B

- SNRとSFDR

- 電池残量計IC

- Liイオン2次電池

- トライアック

- 定電流電源

- センサ

- アナログ・フロント・エンド(AFE)

- 高精度アンプ

- シグナル・チェーン

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード