高度な特性のアクティブ・フィルタも容易に設計できる、WEBENCH® Filter Designer:【講座】回路設計の新潮流を基礎から学ぶ

サンプリングやデジタル演算の高速化が進み、幅広い分野でデジタル・フィルタが普及しているが、連続時間で動作するアクティブ・フィルタには独特の良さがある。特に、AD変換の前段に用いるアンチエリアシング・フィルタや、DA変換の後段に用いるアンチイメージング・フィルタとしては、アクティブ・フィルタが必要だ。

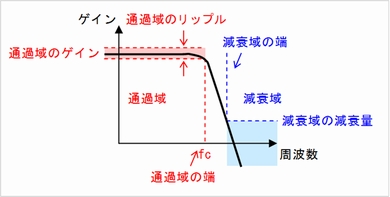

フィルタの仕様設計では、まずフィルタのタイプ(ローパス/ハイパス/バンドパス/バンドストップのいずれか)を選び、通過域と減衰域の端となる周波数を決め、通過域のゲイン、減衰域の減衰量を決める(図1)。さらに、必要に応じて通過域におけるゲイン平坦性(リップル許容値)、波形歪み特性(位相平坦性や群遅延平坦性)、ステップ応答でのセトリング特性(オーバシュート量とセトリング時間)などを決める。

これらの仕様から、まず仕様を満たすフィルタの次数とフィルタ応答(バタワース/チェビシェフ/ベッセル/ガウシアン/リニアフェーズなど)を決める。アクティブ・フィルタで実現するなら、ここから具体的な回路構成を決め、C、Rなどの定数を決め、さらにオペアンプやC、Rなどの具体的な品種を決めていくことになる。この間には複雑な計算を何度も行い、さらにカットアンドトライで値を変えながら、同じような計算を何度も繰り返すことが必要だ。

以前は、少しでも計算量を減らすために数表を活用したり、最近ではExcelなどの汎用ツールやフィルタ専用の計算ツールを利用することが多くなってきた。

WEBENCH® Filter Designerでフィルタを設計する

テキサス・インスツルメンツ(TI)が提供するWEBENCH® Filter Designerは、Webブラウザさえあれば無償で使用できるフィルタ専用のオンライン設計支援ツールだ。簡単なものから高度な特性のものまで、さまざまなアクティブ・フィルタを容易に設計できる。

WEBENCH Filter Designerは、回路構成の決定や定数の計算だけでなく、TIのオペアンプや各社の抵抗、コンデンサをライブラリから選択して具体的な回路を設計できる。他のWEBENCH設計支援ツールと同様に、ダイヤルを用いた最適化やシミュレーションによる動作検証もできる。次に、実際の設計例を見てみよう。

TIのトップページにあるWEBENCH®ツールのガジェットで、フィルタのタイプを選択して設計を開始する。ここでは、ローパス・フィルタを選択した。

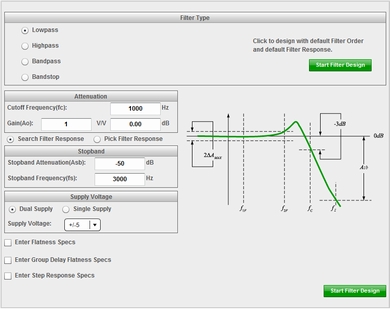

最初に、フィルタ仕様を入力する。ここではカットオフ周波数(通過域の端)を1kHz、通過域のゲインを1倍(0dB)、減衰量を-50dB、減衰域の端を3kHzに選び、さらに電源電圧を±5Vに選んでいる。ゲイン平坦性、群遅延特性、ステップ応答などの入力もここからできる(図2)。

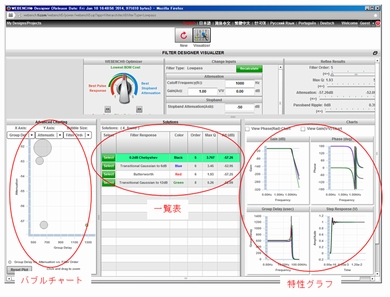

この仕様を満たすフィルタの候補として、ここでは5次チェビシェフ、6次ガウシアン(6dB)、6次バタワース、8次ガウシアン(12dB)の4つが表示される。これらについて一覧表で特性を比較できるだけでなく、画面左下のバブルチャートや、画面右下の特性グラフを使って視覚的に比較可能だ(図3)。

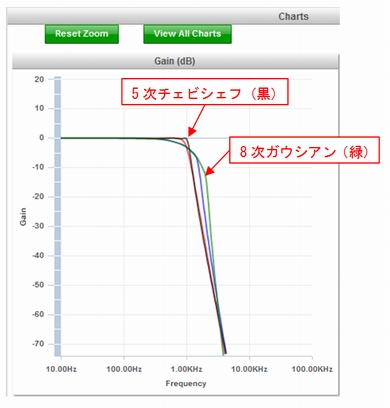

例えば、ゲインの特性グラフを見ると、5次チェビシェフは最も肩特性の切れが良く、8次ガウシアン(12dB)は最も肩特性の切れが悪いことが分かる(図4)。

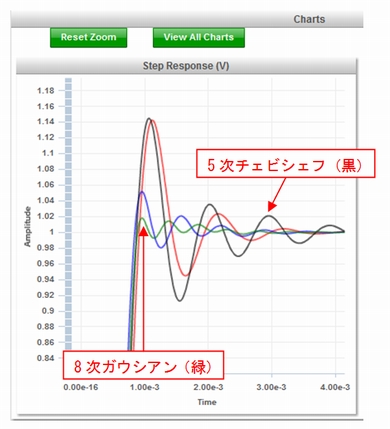

それに対して、ステップ応答の特性グラフを見ると、8次ガウシアン(12dB)は最もオーバシュートが小さくセトリング時間も短いのに対して、5次チェビシェフは最もオーバシュートが大きくセトリング時間も長いことが分かる(図5)。

WEBENCH Filter Designerは、古典的なバタワース、チェビシェフ、ベッセルに加えて、ガウシアンやリニアフェーズなどの新しいフィルタ応答をサポートしており、目的に応じて最適なフィルタを容易に選択できる。

次に、この中から最もステップ応答特性が良好な8次ガウシアン(12dB)を選び、具体的なアクティブ・フィルタを設計してみよう。

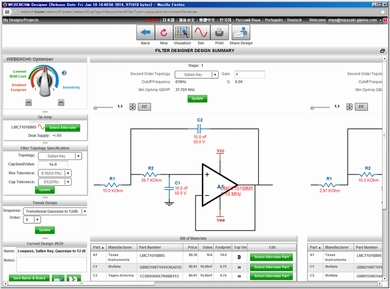

高次のアクティブ・フィルタは、一般に2次フィルタ(奇数次の場合は1次フィルタを追加)を必要な個数だけカスケード接続して作る。WEBENCH Filter Designerでも、その方法で具体的な回路を設計してくれる。ここでは、8次フィルタなので、2次のサレンキー型フィルタを4段カスケード接続した回路になっている(図6)。なお、サレンキー型のかわりに多重帰還型を用いることもできる。

図6 具体的なアクティブ・フィルタ回路

図6 具体的なアクティブ・フィルタ回路WEBENCH® Filter Designerが自動設計した8次ガウシアン(12dB)ローパス・フィルタ。2次サレンキー回路を4段組み合わせて構成している(図には1段目と、2段目の一部が見えている)。各回路は必要なカットオフ周波数とQをもつように定数が決定され、さらに実際のオペアンプ、抵抗、コンデンサの部品が割り当てられているので、そのまま試作、動作検証を行うことができる。また、それぞれ他の部品に置き換えることも可能。

各回路は実際のオペアンプ、抵抗、コンデンサの部品で構成されているので、そのまま試作、動作検証を行うこともできる。また、画面左上のダイヤルを用いて、コスト重視、サイズ重視、感度重視などの観点で自動的に最適化が可能だ。各部品を個別に他の部品に置き換えることもできる。

シミュレーションで動作検証

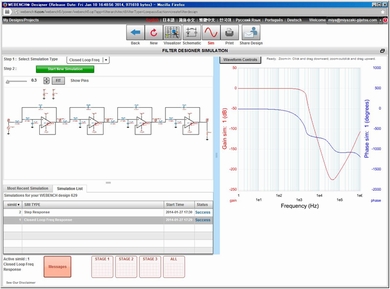

さらに、WEBENCH Filter Designerでは、具体的な部品で設計した回路をその場でシミュレーションして動作検証できる。シミュレーションの種類は、周波数応答、正弦波応答、ステップ応答の3つだ。

図7は周波数応答のシミュレーション例。なお、グラフの右側でゲインが上昇しているのは、オペアンプの帯域幅の上限によるものだ。1MHzで−100dB以上減衰しているので多くの場合問題ないと思わるが、さらに高い周波数まで使用したい場合は、より広帯域のオペアンプに置き換えれば良い。

図7 周波数特性のシミュレーション例

図7 周波数特性のシミュレーション例8次ガウシアン(12dB)ローパス・フィルタ全体の入力−出力間の周波数特性をシミュレーションした。測定ポイントを追加変更することにより、1段目だけ、2段目だけなど、必要に応じてさまざまなシミュレーションを行うことができる。

このように、WEBENCH Filter Designerを用いれば、簡単な用途から高度な用途まで、最適なアクティブ・フィルタ回路をすばやく設計することができる。また、複数の候補を視覚的に分かりやすく比較検討できるので、ただ設計が楽になるだけでなく、フィルタに対する理解を自然に深めることができるのも大きな特長だ。

※WEBENCHはTexas Instrumentsの登録商標です。その他すべての商標および登録商標はそれぞれの所有者に帰属します。

【関連リンク】

TIのWEBENCH Filter Designer

その他のWEBENCHオンライン設計支援ツール

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード