12ビットADコンバータで4Gサンプル/秒を達成、無線通信機器の受信回路の大幅な簡略化が可能に:【講座】回路設計の新潮流を基礎から学ぶ

映像、音、光、振動、温度、電磁波……。自然界に存在する情報はすべてアナログ信号である。このため、センサやトランスデューサ、アンテナなどを搭載する電子機器には必ずと言っていいほどアナログ信号をデジタル信号に変換するADコンバータが搭載されている。

ただし、一口にADコンバータと言っても、その性能は千差万別だ。ADコンバータには、分解能と最大サンプリング周波数(変換速度)という2つの基本性能がある。分解能であれば8ビット〜24ビット。最大サンプリング周波数は、低いものであれば数十〜数百サンプル/秒、高いものであればGサンプル/秒を超える半導体製品が用意されている。従って、設計対象となる電子機器において、検出するアナログ信号の特性をよく吟味し、数多くある半導体製品の中から最適な基本性能を備えるADコンバータを選択しなければならない。

例えば、検出対象となるアナログ信号がオーディオ信号の場合であれば、分解能は16ビット〜24ビット、最大サンプリング周波数は数十k〜数百kサンプル/秒が必要になる。映像信号であれば、分解能は8ビット〜14ビット、最大サンプリング周波数は数M〜数十Mサンプル/秒が最適だろう。無線通信信号の場合は、8ビット〜14ビット、最大サンプリング周波数は数十M〜数Gサンプル/秒を使う必要がある。

ダウンコンバータ回路を1段に

今回は、無線通信機器やレーダー/ライダー機器、テスト/計測器、防衛用電子機器などに向けたADコンバータに話題を絞って話を進めよう。こうした用途では、最大サンプリング周波数が極めて高いADコンバータが必要になる。なぜなのか。それは、対象となる無線(RF)信号などの変化が極めて高速だからだ。それに十分に追従できるADコンバータでなければ、RF信号を高い精度でデジタル信号に変換できない。

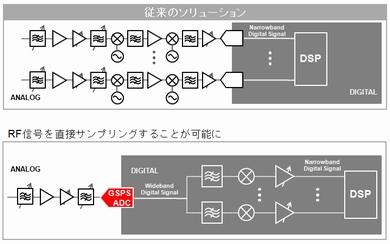

ただし、従来はそれほど高速なADコンバータが実用化されていなかった。そこで携帯電話の基地局などでは、「回路構成の工夫」で対応してきた。一般に、こうした基地局では、高い周波数のRF信号は受信した後に、FPGAやDSPなどで処理できるように、低い周波数のデジタル信号にダウンコンバートする必要がある(図1)。最大サンプリング周波数が極めて高いADコンバータがあれば、1回の変換(1段)で済む。しかし従来は、高速なADコンバータが入手できなかったため、3〜4段のダウンコンバータ回路を使うしか方法がなかった。

図1 無線通信機器のダウンコンバータ回路

図1 無線通信機器のダウンコンバータ回路超高速なADコンバータを入手できなかった従来は、3〜4つの変換段を使って、RF信号をデジタル信号に変換していた(上図)。変換段が複数になると、回路が複雑になる上に、部品コストの上昇や実装面積の拡大というデメリットが発生してしまう。一方、超高速なADコンバータを使えば、入力したRF信号を直接サンプリングすることが可能になるため、変換段を1つに減らせる(下図)。回路構成がシンプルになり、部品コストや実装面積を削減できるようになる。

変換の段数が多ければ多いほど、回路の複雑性と部品コスト、実装面積が増大する。逆に言えば、変換の段数を1段に減らせれば、回路の複雑性も、部品コストも、実装面積も大幅に削減できることになる。このため、超高速なADコンバータの実用化を望む声は大きかった。

フォールディング・インターポレーション方式を採用

今回、テキサス・インスツルメンツ(TI)は、こうした声に応えるべく、最大サンプリング周波数が4Gサンプル/秒と非常に高いADコンバータ「ADC12J4000」を発売した。しかも、分解能は12ビットと高い。12ビットの分解能があれば、携帯電話基地局に適用することが可能だ。入力信号の最大帯域幅は3.3GHzと広い。つまり最大3.3GHzのRF信号であれば、直接サンプリングできることになり、ダウンコンバータの変換段数を1段に減らせる。その分だけ、回路の複雑性や部品コスト、実装面積を削減できるわけだ。

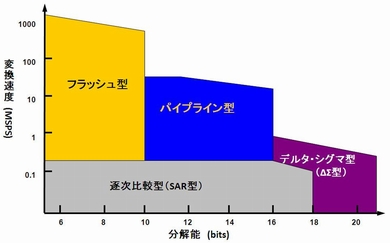

発売したADコンバータのアーキテクチャは、「フォールディング・インターポレーション」と呼ぶ方式である。一般に、ADコンバータにはさまざまなアーキテクチャが存在する。ΔΣ(デルタ・シグマ)方式や、逐次比較(SAR:Successive Approximation Register)方式、パイプライン方式、フラッシュ方式などである(図2)。この中で最も高い最大サンプリング周波数が得られるのがフラッシュ方式である。今回のフォールディング・インターポレーション方式は、フラッシュ方式と同等以上の最大サンプリング周波数が得られると同時に、12ビットという比較的高い分解能が得られる点が特長だ。

図2 ADコンバータのアーキテクチャ

図2 ADコンバータのアーキテクチャ縦軸に最大サンプリング周波数(変換速度)、横軸に分解能をとって、各アーキテクチャの実現可能な範囲を図示した。今回のフォールディング・インターポレーション方式はフラッシュ方式とほぼ同等の性能を実現できるが、分解能についてはすでに12ビットを実現できている。

A/D変換の仕組みはフラッシュ方式と同様に、並列処理を巧みに利用し、高速化を実現している。具体的には、1ビット・コンパレータ(比較器)とプリアンプ、抵抗器を数多く並べて同時に動作させるという仕組みだ。

ただし、TIが超高速なADコンバータを製品化するのは今回が初めてではない。2010年に、最大サンプリング周波数が3.6Gサンプル/秒の12ビットADコンバータ「ADC12D1800」を投入している。今回、最大サンプリング周波数をさらに高められた技術的なポイントは2つある。アナログ回路の改善と製造プロセスの改善である。

これらの改善によって、副次的な効果も得られた。それは、消費電力の削減だ。今回の製品の消費電力は1.9Wで、従来の3.6Gサンプル/秒品に比べると60〜70%の削減を達成した。

JESD204Bインタフェースを搭載

この他、「ADC12J4000」には特筆すべき点がもう1つある。それは、ADコンバータを適用した回路の設計難易度を大幅に低減する工夫が盛り込んである点だ。工夫は2つある。

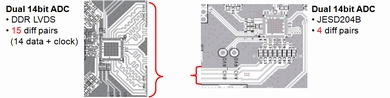

1つは、A/D変換を実行した後のデジタル信号の出力インタフェースに、従来のLVDSではなく、JESD204B準拠のシリアル・インタフェースを採用したことだ(図3)。JESD204Bとは米国の標準化団体「JEDEC」が策定したシリアル・インタフェース規格で、ADコンバータやDAコンバータを、FPGAやDSP、ASICなどのロジック・デバイスに接続する用途に向けたものだ。

図3 JESD204Bの効能

図3 JESD204Bの効能デュアルの14ビットADコンバータの出力に、左図はLVDSを使った場合、右図はJESD204Bを使った場合である。LVDSの場合は、データ・ラインが14本、クロック・ラインが1本となり、プリント基板のレイアウト設計が複雑になる。一方、JESD204Bを使えば、4つの差動ペアで済むため、設計を大幅に簡素化できる。

JESD204Bを採用したため、高速な信号をそのままロジック・デバイスに入力できる。データ伝送速度は最大8Gビット/秒。信号のライン数は、デシメーションや伝送速度に応じて、1〜8本の間で設定可能なため、プリント基板のレイアウト設計が大幅に簡素化できる。

もう1つの工夫は、デシメーションなどを実行するデジタル・フィルタ機能などを集積したことだ。外付けで用意する必要がないため、部品コストや設計時間、実装面積などを削減できる。

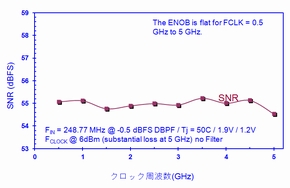

この他、「ADC12J4000」の基本特性は以下の通りだ(図4)。ノイズ・フロアは−149dBFS/Hz。第3次相互変調歪み(IMD3)は−64dBc。同社従来品と比較すると7dB改善したとする。ノイズ対電力比(NPR)は48.4dB。電源電圧は1.9Vと1.2V。パワーダウン・モード時の消費電力は10mW。パッケージは、実装面積が10mm×10mmの68ピンQFN。動作温度範囲は−40〜85℃である。「ADC12J4000」の性能評価に向けた評価モジュール「ADC12J4000EVM」も用意している。

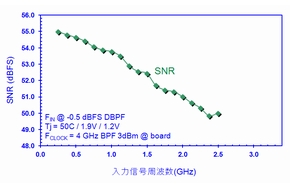

図4 ADC12J4000のSN比

図4 ADC12J4000のSN比左は、クロック周波数を変えた場合のSN比(信号対雑音比)の変化を、右は入力信号周波数を変えた場合のSN比の変化をプロットした図である。いずれも、SN比の変化は非常に小さく抑えられていることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード