設計支援ツールでアナログ回路を簡単設計(4) 複数負荷の電源構成設計を強力にサポートするWEBENCH Power Architect:【講座】回路設計の新潮流を基礎から学ぶ

ボード上にはさまざまな電源電圧で動作する負荷(LSI、部品、回路ブロック)が混在している。プロセッサやFPGAなどの大規模LSIには、1個のLSIでもコア用やI/O用など複数の電源電圧で動作するものがある。それに対応して、オンボード電源も複数の異なる負荷に電源を供給することが求められている。

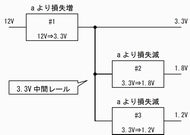

例えば、電源ユニットから供給される12V電源を降圧して、3.3Vのロジック電源、1.8VのDRAM電源、1.2Vのプロセッサコア電源を供給する例を考えてみよう。最も簡単には、12V⇒3.3Vの降圧型コンバータ、12V⇒1.8Vの降圧型コンバータ、12V⇒1.2Vの降圧型コンバータの3個の電源回路をそれぞれ別個に設計すれば実現できる。だが、それは最適な構成と言えるだろうか。

降圧型の電源回路では、一般に入出力間の電圧差VI-Oが大きいほど損失が大きく、また負荷電流ILが大きいほど損失が大きくなる傾向がある。それによって効率が低下するとともに、サイズの増加やコストの増加にもつながる。

LDOなどのリニア・レギュレータでは、損失はほぼVI-Oに比例する。同期整流などのチョッパ型DC/DCコンバータは、VI-Oが大きくても損失を小さくできるのが特長だが、それでも電圧差が大きいほど損失は大きくなる。12V⇒3.3V、12V⇒1.8V、12V⇒1.2VというようにVI-Oが比較的大きい電源回路を3個用いるのは、全体として損失が大きくなり、インダクタやコンデンサなどの受動部品にも負担をかける可能性がある。

いったん適当な中間レールまで降圧して、そこから必要に応じてさらに降圧していくことによって、トータルとして高効率、小型、低コストの電源システムを構成できる可能性がある。VI-Oが特に大きい場合は、中間レールは1段だけでなく、2段以上が良い場合もある。一方、中間レールを用いない方が良い結果が得られる場合もある。

図1に、負荷が3個の場合の電源構成例を3種類示す。この他にも、さらにいくつかの電源構成が考えられる。そして、どれが最適かはその時の負荷の仕様や重視する条件によって異なる。わずか3個の負荷でも電源構成の候補はいくつもあり、それぞれを実際に設計して比較・評価しないとどれが最適か判断できない。

- (a)、(b)はどちらも#1、#2、#3の3個の降圧型コンバータで構成される。(b)では#1の出力を中間レールに利用することによって、#2と#3は損失が減り、#1は損失が増える

- (c)は中間レール用の降圧型コンバータ#4を追加している。#1、#2、#3は(a)より損失が減るが、#4の分だけ損失、サイズ、コストは増える

- どれがトータルで最適になるかは、そのときの条件により異なる

複数負荷の電源構成設計の支援ツール、WEBENCH Power Architectを使ってみる

テキサス・インスツルメンツ(TI)のWEBENCH Power Architectは、このような複数負荷の電源構成の設計と最適化を強力にサポートしてくれるツールとして定評がある。このWEBENCH Power Architectを使って、実際に電源の構成設計を行ってみよう。

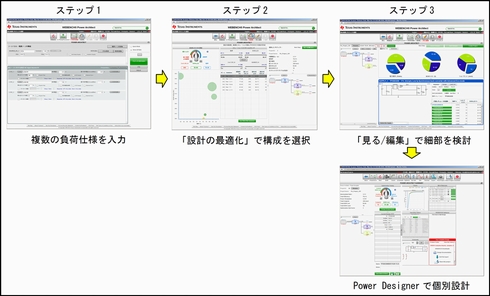

図2に示すように、WEBENCH Power Architectによる構成設計はわずか3ステップで実行でき、その後はWEBENCH Power Designerによる個別設計にシームレスに進むことができる。

まず「負荷を追加」画面(ステップ1)で入力仕様や負荷仕様を設定する。この画面では複数の入力仕様を設定でき、それぞれの入力ごとに複数の負荷仕様を設定できる。入力は12V±10%として、負荷は3.3V/0.5A、1.8V/1.0A、1.2V/2.0Aの3つを設定した。

| 負荷#1 | 負荷#2 | 負荷#3 | |

|---|---|---|---|

| 最小入力電圧 | 10.8V | ||

| 最大入力電圧 | 13.2V | ||

| 出力電圧 | 3.3V | 1.8V | 1.2V |

| 負荷電流 | 0.5A | 1.0A | 2.0A |

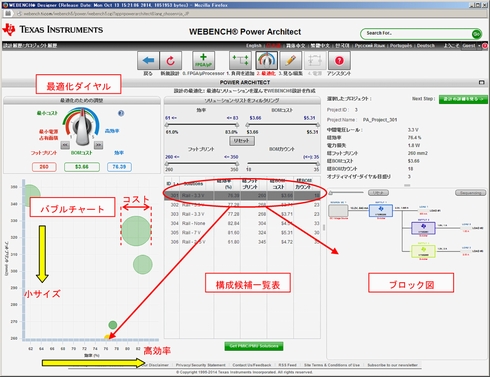

「プロジェクト要件を送る」のボタンをクリックすれば、複数の構成候補を効率、サイズ、コストの観点から視覚的に比較・検討できる「設計の最適化」画面(ステップ2)が開く。図3のように、この画面では仕様を満たす複数の構成候補がリストアップされ、それぞれの特長が分かりやすく表示される。

中央の表に構成候補の一覧が表示される。また、各候補の効率、サイズ(フットプリント)、BOMコストが左側のバブルチャートに表示される。一覧表で選択された候補は、バブルチャートでは黄色のバブルで表示されている。さらに、一覧表で選択された候補の電源構成が、右側のブロック図に表示される。

一覧表には6つの候補が表示されているが、現在選択されている候補は、最も小型(縦軸は下に行くほど小型)かつ低コスト(バブルが小さいほど低コスト)であることが分かる。それに対して、効率はやや低め(横軸は右に行くほど高効率)である。また、右側のブロック図を見れば、この候補は3.3Vを中間レールとして、そこから1.8Vと1.2Vを生成していることが分かる。

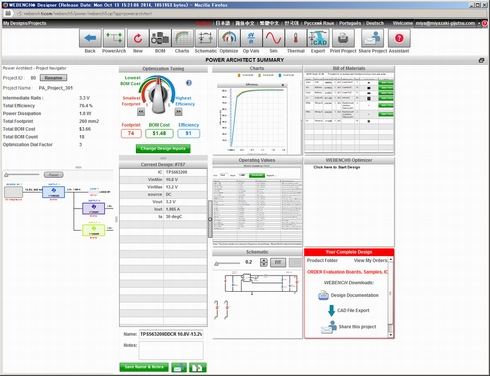

「設計の最適化」画面で最適な候補を1つ選び、「設計の詳細を見る」のボタンをクリックすれば、選択した構成の細部の状況を検討したり、部品を変更したりできる「見る/編集」画面(ステップ3)に進む。そこまで終わったら、そのままWEBENCH Power Designerに移行して個別の電源回路設計に進む。もちろんシームレスにシミュレーション機能も実行できる。

今回は1つの入力から3つの負荷を生成する例を示したが、入力や負荷が増えて複雑になるほど電源構成の最適化は手作業では困難な仕事になり、WEBENCH Power Architectの効果は大きくなる。

- TIのWEBENCH オンライン設計支援ツールの詳細

- WEBENCH Power Designer:単一負荷の電源設計向けオンライン設計支援ツール

- WEBENCH Power Architect:複数負荷の電源設計向けオンライン設計支援ツール

※ WEBENCHはTexas Instrumentsの登録商標です。その他すべての商標および登録商標はそれぞれの所有者に帰属します。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード