高速信号発生アプリケーションのクリティカルな要件:アナログ回路設計講座(4)

今回は、高速信号発生アプリケーションにおいてクリティカルな要件である“帯域幅”と“分解能”の双方を満たす回路について検討していく。

はじめに

高速信号発生アプリケーションにおいてクリティカルな要件は、帯域幅と分解能です。最新の信号発生アプリケーションでは、高速なデジタル・アナログ・コンバーター(D-Aコンバーター、DAC)を使用して、シングル・トーンから帯域幅数百メガヘルツの複雑なマルチチャネル波形まで、さまざまな種類の波形を生成します。これらのアプリケーションには、アナログ性能を損なわずにこれらの波形を生成できる速度を持つ高速D-Aコンバーターが必要になります。多くの信号発生アプリケーションでは、チャネル数とチャネル間隔が位相ノイズによって制限されます。従来、位相ノイズはD-Aコンバーターのクロック入力をドライブするクロックによって設定されますが、D-Aコンバーターによる付加位相ノイズが出力スペクトラムに出現し、生成可能な信号が制限されることがあります。あらゆる汎用の信号発生アプリケーションにとって理想的なD-Aコンバーターは、可能な限り高速かつ低ノイズで直線性に優れ、付加位相ノイズが極めて少ないものです。これらの仕様のいずれか1つでも欠けている場合、生成される波形はアプリケーションの要件を十分に満たせません。

帯域幅

信号発生アプリケーションを設計する際に最も重要な仕様項目となるのが帯域幅です。設計者は、目的の信号を生成するにはどれだけの帯域幅が必要かをまず決定します。必要な帯域幅は、個々のシグナリング・プロトコルまたはアプリケーションによって異なります。目的の帯域幅を達成するには、少なくともその2倍の速度のDACが必要です。帯域幅とサンプル・レート(fs)に関するこの関係はHarry Nyquistによって定義されており(ナイキストの定理)、離散化システムにおける信号の挙動もこの定理によって説明されます。

DCからfs/2まで達する信号を生成することも不可能ではありませんが、出力スペクトラムには生成した信号のイメージが出現するため、通常は現実的でありません。イメージはN*fs+/-fout(foutは生成した信号の周波数)に出現します。実際には、出力スペクトラムに現れるこのイメージを減衰するために再構成フィルターが必要です。生成した信号がfs/2まで達していなくても、その近くまで迫っている場合はフィルターの制約があるためイメージを除去するのは困難です。再構成フィルターは、現実の部品を使用してアナログ・ドメインに実装します。このフィルターで使用する部品はデジタル・フィルターのような理想部品ではないため、通過域のリップルと挿入損失を伴う非理想的な特性となります。一般に、このフィルターの次数を大きくするとリップルと挿入損失が大きくなり、理想フィルターの設計はますます困難になります。信号の帯域幅がfs/2に近くなるほど、サンプリング過程で発生するイメージを減衰しようとすると高次のフィルターが必要となります。フィルターの次数が大きくなると必要な部品が増え、挿入損失と通過域のリップルも大きくなります。

高サンプル・レートのDACを使用すると利用可能な帯域幅が拡大し、フィルター要件が緩和されます。こうすると、多くの部品で構成した複雑なフィルターは不要になり、設計が簡略化され、結果品質も向上します。例えば16ビット、2.5Gsps高速DACの「LTC2000」はサンプル・レートが2.5Gspsのため、fs/2周波数は1.25GHzです。したがって信号帯域幅が800MHzの場合、1.7GHz以降に信号のイメージが現れます。この場合、目的の周波数バンドとイメージ周波数の間には900MHzの間隔(ガードバンド)があるため、簡単なローパス・フィルターでイメージを容易に除去できます。これよりもサンプル・レートの低いDACを使用するとイメージと目的信号の周波数の間隔が小さくなり、より急峻で複雑なフィルターが必要になります。

fs/2まで達する信号を生成する際にもう1つ問題となるのは、DACには出力信号の高周波成分が減衰するSINC(sin(x)/x)ロールオフが必ず存在するという点です。このロールオフにより、サンプル周波数(fs)付近ではゲインがゼロになるため、サンプル・レートと同じ周波数に現れる信号を生成しようとしても、単にDC電圧の信号が生成されてしまいます。通常のアプリケーションでは、ナイキスト・ゾーン(DCからfs/2まで)の約60%までならそれほど大きなSINC減衰もなく利用できます。DCで信号レベルが0dBの場合、ナイキスト・ゾーンの60%で信号レベルは6dB減衰します。通常はこのロールオフの逆関数をデジタル・ドメインに実装し、出力信号で必ず発生するロールオフを補正します。こうすると、DACから出力される信号の周波数特性を平たんにできます。より高速なDACを使用すると、DACの出力周波数が高くなるにつれてSINC関数のロールオフが小さくなります。

位相ノイズ

信号発生アプリケーションでもう1つ考慮すべき重要な事項として、出力の位相ノイズがあります。出力信号に位相ノイズが現れると、信号の間隔および生成可能な変調次数が制限されます。信号生成の過程で付加される位相ノイズが大きいほどSNRが低下し、生成した信号のビット・エラー率(BER)が高くなります。時間領域における信号のゼロクロスの精度は、ジッタとして表されます。理想的な信号の場合、どの周期も同じタイミングでゼロクロスが発生します。しかし実際にはゼロクロスの発生タイミングにはある程度のばらつきがあります。このばらつきを周波数領域に変換すると、位相ノイズは基本周波数を中心としたスペクトル漏れとして観察されます。複数のトーンの間隔が近接している場合、あるトーンのSNRは隣接するトーンのスペクトル漏れの影響を受け、これによって信号のBERが大きくなり、出力信号の精度が低下します。このようなシグナル・インテグリティの低下は、出力信号への位相ノイズの混入を抑えることによって防ぐことができます。

信号発生システムへの位相ノイズの混入を防ぐ最も簡単な方法は、位相ノイズが極めて小さいクロックを使用することです。クロックの位相ノイズが小さいと、生成した信号の位相ノイズも小さくなります。もう1つの重要な点として、生成した信号のクロックの位相ノイズは生成した信号とクロック・サンプル・レートの比に比例して減衰します。つまり、高周波数のサンプル・クロックで低周波数の信号を生成した方が、同じクロックで高周波数の信号を生成するよりも出力信号の位相ノイズは小さくなります。生成したスペクトラムがワイドバンドの場合、生成した信号のスペクトラムの高域の方が低域に比べ位相ノイズが大きくなります。

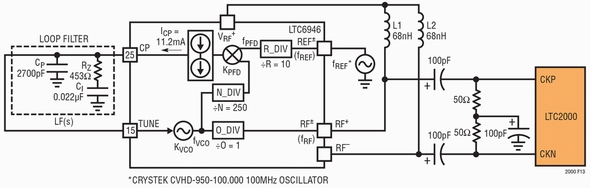

「LTC6946」は外付けVCOなしで370MHz〜5.7GHzの信号を生成できる周波数シンセサイザです。このデバイスは位相ノイズ特性に優れ、スプリアス成分が非常に少ないため、信号発生アプリケーションのクロック・ソースに最適です。LTC6946を使用して高速DACのLTC2000をドライブすると位相ノイズを大幅に抑えることができ、非常に要求の厳しい信号発生アプリケーションにも対応できます。LTC6946でLTC2000をドライブした場合の代表的な回路図を図1に示します。

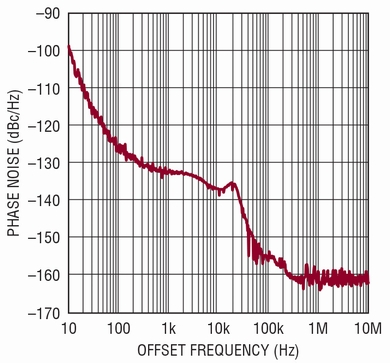

図2は、LTC6946とLTC2000を組み合わせた場合の位相ノイズをグラフにしたものです。LTC6946はVCOを内蔵して利便性を高めている一方、位相ノイズ特性はやや劣ります。さらに位相ノイズを低減するには、LTC6945と外付けVCOを組み合わせます。LTC6945とLTC6946のどちらの周波数シンセサイザも、最大の位相ノイズ源はVCOです。LTC2000の付加位相ノイズは、出力トーン65MHzでオフセット1MHzの場合-165dBc/rHzです。このため、LTC2000自体の付加位相ノイズよりもクロックの位相ノイズの方が圧倒的に大きくなります。出力信号の品質が他のノイズによって低下するのを防ぐには、アナログ出力部に適切なレイアウト手法を採用する必要があります。

適切なRFレイアウト

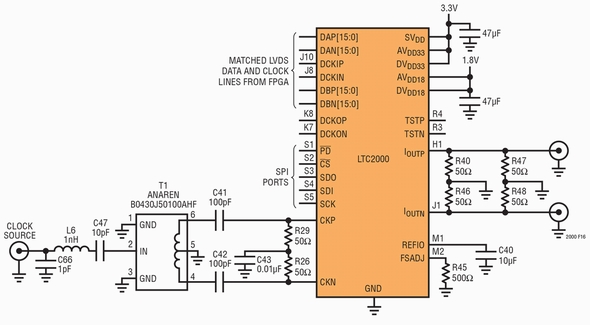

高速なDACとクロック・ソースを使用しても、適切なデザインおよびレイアウト規則に従ってPCBを設計しなければその効果を十分に生かすことができません。十分な対称性、バイパス、バリアを確保しないと生成したアナログ出力波形に歪みが生じ、ノイズやその他のスプリアスが発生することがあります。図3に、LTC2000の代表的な回路図を示します。

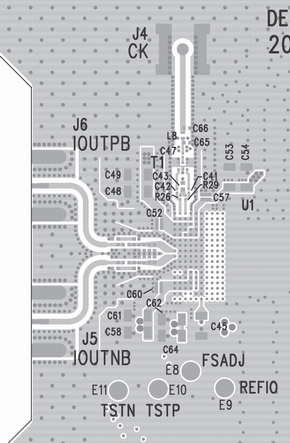

LTC2000のノイズ・スペクトル密度は500MHzまでの信号に対して>158dBm/rHzで、幅広い周波数の生成信号において高いSNRが得られます。LTC2000のSFDR(スプリアスフリー・ダイナミックレンジ)は出力周波数500MHzまでが>74dBで、1GHzまでが>68dBです。LTC2000の性能を最大限に引き出すには、適切なレイアウトが必要です。DACからの出力は差動ペアとして扱い、なるべく対称に配線する必要があります。出力ネットワークが対称でないと、差動ペアの各信号に電位差が生じる可能性があります。この電位差によってコモンモード妨害波が生じ、出力スペクトラムに不要な歪みとノイズが発生します。この妨害波を防ぐには、各出力の伝送線路を対称にレイアウトします(図4)。伝送線路沿いのビアも両側が対称となるように配置します。伝送線路に沿ってビアを配置すると、有害な信号が生成後の信号に結合するのを抑えることができます。

有害な信号からアナログ出力を保護するには、適切なレイアウト手法に基づいてビアを使用します。信号生成用DACのポートで特にレイアウトに注意が必要なのは、クロック入力、アナログ出力、データ入力の3つです。データ入力を出力またはクロックの近くに配線すると、データ入力がこれらの信号に結合して出力スペクトラムにスプリアスが現れます。同様に、不適切なレイアウトによってクロックがアナログ出力に結合すると、生成した信号のインテグリティが低下します。DACの性能を最大限に引き出すには、ボードを設計する際にデジタル部、クロック信号、アナログ出力部の間に適切なバリアを設ける必要があります。通常、デジタル信号、クロック信号、アナログ出力同士の干渉を最小限に抑えるには、これらの信号をそれぞれPCBの別々の層に配線することを推奨します。

図4に示したLTC2000のレイアウト例も、デジタル信号、クロック、アナログ出力を分離しています。この図でデジタル・トレースはPCBの内層に配線しており、LTC2000のパッド内のビア部分でのみ外部に露出しています。クロック・トレースは短くし、周囲をビアで囲んで信号を隔離し、デジタル・トレースやアナログ出力の配線の影響を受けないようにしています。出力トレースはなるべく対称となるようにし、バリアで囲んで有害な信号からアナログ出力を保護しています。これらのガイドラインに従ってレイアウトし、クリーンなサンプル・クロックを使用すると、LTC6946とLTC2000の組み合わせによって極めてクリーンな波形が得られ、非常に要求の厳しい信号発生アプリケーションにも対応できます。

まとめ

信号発生アプリケーションでは、イメージとの間に十分なガードバンドを確保して出力フィルターの複雑さを軽減しようとすると高いサンプル・レートが要求されます。サンプル・レートを高くすると、すべてのDACに必ず存在するSINCロールオフを軽減できます。サンプル・レート2.5GspsのLTC2000は、要求の厳しい信号発生アプリケーションにも対応できる十分な帯域幅を確保すると同時に、優れたスペクトルおよびノイズ特性を実現しています。信号発生アプリケーションにおいて、隣接するトーンの間隔を狭くするにはクリーンで低位相ノイズのサンプル・クロックが必要です。LTC2000のクロック・ソースにLTC6946を使用すると、外付けVCOなしで優れた位相ノイズ特性が得られます。LTC2000の付加位相ノイズは、出力スペクトラムでほとんど検出されません。適切なレイアウト手法を採用し、LTC2000の重要な信号の周囲にバリアを設けると、要求の厳しい信号発生アプリケーションにも対応できる理想的なノイズおよびスペクトル特性が得られます。こうするとスプリアス成分のない信号を生成でき、必要なフィルタリングは最小限で済みます。LTC2000は数百メガヘルツまでの範囲でスペクトル純度の高い低ノイズの信号を生成するのに理想的で、最新の信号発生アプリケーションで発生する問題を解決するのに必要なサンプル・レートと性能を備えています。

【著:Clarence Mayott/リニアテクノロジー、ミックスト・シグナル製品担当アプリケーション・エンジニア】

Copyright © ITmedia, Inc. All Rights Reserved.

提供:リニアテクノロジー株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2016年6月30日

industry 4.0の実現へ

スマート・ファクトリーに向けた変革であるインダストリー4.0。しかしながら、インダストリー4.0がもたらすメリットは最小限しか認識されていません。エレクトロニクス業界にもたらすインダストリー4.0のメリットを、あらためて考察していきましょう。

オートメーション分野で活用されるイーサネット

産業用イーサネットが製造分野にもたらすメリットについて解説します。最初に解説するのは、プラントのオートメーション・システムに適用される技術としてイーサネットが有用な選択肢になった理由についてです。

Dust Networks オススメ記事

ワイヤレス・センサ・ネットワーク技術が半導体工場の生産効率を高めた事例を紹介しよう。これまで人手に頼らざるを得なかった175本にも及ぶ特殊ガスボンベの常時監視を大きな工事を伴わず自動化し、ガスの使用率を高めるなどの成果を上げた事例だ。