高速データコンバータ向け新規格「JESD204B」の概要と適合テストでの課題:アナログ回路設計講座(40)

高速、高分解能のデータコンバータ(A/Dコンバータ、D/Aコンバータ)向けに策定されたシリアルインターフェース規格「JESD204B」。最高12.5Gbpsのデータ転送速度を誇るこの新規格とはどのようなものか説明するとともに、JESD204Bに対応するデバイスの検証に必要なテストについて確認します。

JESD204Bは、高速、高分解能のデータコンバータ(A/Dコンバータ、D/Aコンバータ)向けに策定されたシリアルインターフェース規格です。そのデータ転送速度は最高12.5Gbpsに達します。市場には、既にこの規格に準拠する製品が登場しており、その数は近い将来、大幅に増加すると予想されています。JESD204Bに対応するインターフェースがもたらす最も重要なメリットは、データコンバータとロジックデバイス(FPGAやASICなど)の間のデータ伝送帯域幅が確実に拡大することです。

他のインターフェース規格を新たに採用する場合と同様に、JESD204Bを導入する際にも新たな課題が生じます。システム開発者にとっての課題は、プリント回路基板設計の観点からJESD204Bを最適に実装する方法を知ることです。また、正常に動作しない場合に備えて、システムのデバッグ方法も把握しておく必要があります。一方、ICメーカーにとっては、新たなJESD204B対応デバイスをテストする方法を確立することが課題になります。それにより、比較的理想に近い環境で仕様を満たしていることを確認するだけでなく、最終的なシステムの稼働環境でJESD204Bが正常に動作することを保証することも可能になります。

本稿では、まずJESD204Bについて簡単に説明します。その上で、JESD204Bに対応するデバイスの検証に必要なテストについて確認します。さらに、最終的なシステムの稼働環境を再現するために利用可能な手法について解説を加えます。

JESD204B ―― データコンバータにとっての自然な進化

データコンバータは、オーディオ機器から計測器まで、広範なアプリケーションで使用されています。現在も進化を続けており、分解能とサンプルレートを高めるべく取り組みが進められています。それに伴い、データを入出力する方法もより複雑になっています。10〜20年ほど前には、データコンバータのサンプルレートは高速製品であっても100MSPS以下に限られていました。そのため、データの入出力には、TTL(Transistor-transistor Logic)レベルまたはCMOSレベルのパラレルデータバスを使用すれば十分でした。例えば、分解能が12ビットのデータコンバータでは、データの入出力に12本のピンを使用するといった具合です。このような仕様で、クロックに対して適切なセットアップタイム/ホールドタイムを確保することができていました。

しかし、サンプルレートが100MSPSを超えるようになると、シングルエンドの信号ではセットアップタイム/ホールドタイムを確保することができなくなりました。そのため、より高い速度を得るために、高速製品では差動伝送方式が使われるようになりました。ただ、それにはピン数の増加という代償が伴いました。例えば、分解能が12ビットの製品には、データ用に24本のピンが必要になるといった具合です。この問題に対処するために、シリアルデータインターフェースが使われるようになりました。例えば、6倍のシリアル化に対応する製品の場合、分解能が12ビットであっても2つの差動I/Oだけ(4ピンのみ)でデータを伝送できます。その後もデータ用のインターフェースの進化は続き、現在ではJESD204Bを採用した製品が開発されるようになりました。

標準化団体のJEDEC(Joint Electron Device Engineering Council)は、JESD204規格として2つのバージョンをリリースしています。1つ目のバージョンであるJESD204 2006は、定格の最高速度が3.125Gbpsのデータコンバータに対し、SerDes(Serializer/Deserializer)をベースとする高速シリアルインターフェースならではのメリットをもたらしました。この規格は2008年に改訂され(JESD204A 2008)、複数のデータレーンやレーン同期のサポートといった重要な機能強化が行われました。2つ目のバージョンであるJESD204Bは、JEDECのJC-16作業グループ(25の企業、約65人のメンバーで構成。プロジェクト150.01)によって策定されました。このバージョンでは、最高レーンレートの拡大、インターフェースを介したデタミニスティックな遅延のサポート、高調波クロッキングのサポートなど、多くの機能強化が図られました。

コンプライアンステストの公式仕様が存在しない

他の多くの高速シリアルインターフェース規格とは異なり、JESD204Bではコンプライアンステストの公式仕様が定められていません。通常、テストの仕様には、適合性(相互運用性)を保証するために実施しなければならないテスト項目が列挙されると共に、各テストを実施するための手順が記載されます。つまり、2つの価値が提供されるということです。さまざまなメーカーが使用する一貫性のある手順が存在すれば、規格に対する共通の理解が得られ、前提条件の違いを排除することができます。ただ、コンプライアンステストの公式仕様が存在しないからといって、すべてが台無しになるというわけではありません。一連のテストの内容と手順を定めるために必要なすべての情報は、JESD204Bの規格と、同規格が参照している規格に記載されています。必要な情報を集める作業は、個々のICメーカーやシステム開発者に委ねられています。

PHY層のテスト

物理(PHY)層のテスト(以下、PHYテスト)としては、個々のデータレーンが備えるドライバ回路とレシーバー回路の検証を行います。言い換えれば、リンクのアナログテストを実施するということです。デジタル機能や処理のテストは含まれません。PHYテストの実施に向けては、テスト項目の完全なリストを策定すべく作業を進めることになるでしょう。その際には、SerDesのPHYテストについて検討することになるはずです。これについては、OIF-CEI-02.0のセクション1.7を参照することにより、推奨されるリストを入手することができます。JESD204Bの規格では、それらの推奨事項を取り入れていますが、いくつかの変更箇所があります。例えば、JESD204Bでは、ランダムジッタを独立したテスト項目として扱っていません。ランダムジッタはトータルジッタに含めるという考え方を選択しています。また、OIF-CEI-02.0では、推奨テストパターンとしてPRBS31パターンを使用すると規定しています。それに対し、JESD204Bでは、JSPAT、JTSPAT、modified RPATを使用すると定めています。

OIF-CEI-02.0にもJESD204BのPHYのセクションにも記載されていませんが、必須のPHYテストに加えて、追加で実施を検討する価値のあるPHYテストが存在します。例えば、他のSerDesのコンプライアンステスト規格を参照すると、ペア間のスキュー(トランスミッタの場合)やペア間のスキュー耐性(レシーバーの場合)のテストについて規定されていることがあります。ここでこの話題を取り上げた理由は、そうしたテストをJESD204Bの規格にも追加するべきだと主張したいからではありません。実際、JESD204Bへの適合性を保証する上で、追加のPHYテストを実施する必要はないからです。ここでお伝えしたいことは、特定のPHYテストで不合格になった場合に、他のPHYテストを使用することで、不具合の原因に関する洞察が得られる可能性があるということです。

テスト項目のリストを策定したら、JESD204Bの規格を基にテストの判定値(上限値、下限値)を設定します。判定値には次の3つのセットがあることを覚えておいてください。

- LV-OIF-11G-SR

- LV-OIF-6G-SR

- LV-OIF-SxI5

JESD204Bに対応するデバイスは、複数の判定値のセットをサポートしていることがあります。この場合、そのデバイスが、それらすべての判定値を使ったテストに合格するかどうかを確認する必要があります。

JESD204BのPHYテストについては、ジッタに関連する用語が原因で混乱が生じる可能性があります。JESD204BとOIFCEI-02.0で使われている用語が、試験装置のメーカーが使用している用語と異なっているからです。図1に、標準的なジッタマップを示しました。試験装置のメーカーが使用している用語は、業界標準のデュアルディラックジッタモデルに基づいています。ジッタは非常に微妙な問題なので、用語の相違が原因となってテストの手順に問題が生じる可能性があります。表1に、ジッタ関連の用語に対するアナログ・デバイセズの解釈を示しました。

| JESD204Bにおける ジッタ関連の用語 |

JESD204Bにおけるジッタの名前 | 試験装置メーカーが使用する ジッタ関連の用語と解釈 |

|---|---|---|

| T_UBHPJ | 送信非相関有界高確率ジッタ | BUJ(PJとNPJ) |

| T_DCD | 送信デューティサイクル歪み | DCD |

| T_TJ | 送信トータルジッタ | TJ |

| R_SJ-HF | 受信正弦波ジッタ、高周波 | PJ > 1/1667×BR |

| R_SJ-MAX | 受信正弦波ジッタ、最大値 | PJ < 1/166,700×BR |

| 受信有界高確率ジッタ―相関 | DDJ | |

| R_BHPJ | 受信有界高確率ジッタ―非相関 | NPJ |

| R_TJ | 受信トータルジッタ | TJ |

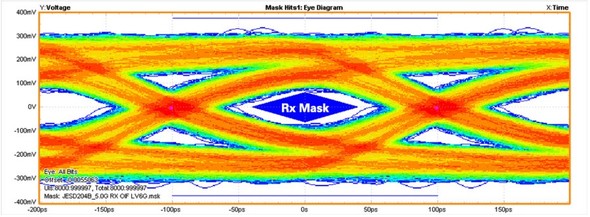

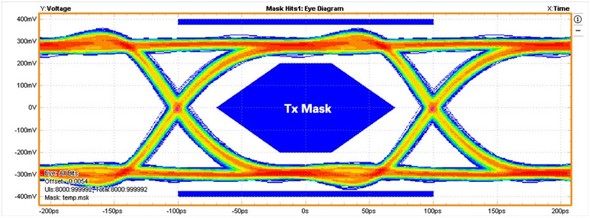

JESD204BのPHYテストについては、混乱を引き起こす原因となり得る要素がもう1つあります。それは、11.1Gbpsを超えるデータレートにおけるアイマスクです。JESD204Bでは、11.1Gbpsを超えるデータレートにおいては11.1Gbpsの正規化ビット時間を使用すると規定されています。そのため、12.5Gbps(ビット周期は80ピコ秒)でデバイスを動作させる場合にも、11.1Gbpsのビット周期(90.9ピコ秒)を使用することになります。ここで問題になるのは、アイマスクはUI(ユニット・インターバル)のエッジからでもUIの中心からでも作成できるという事実です。JESD204Bでは、どこを基準点にするのか明確には規定されていません。基準点がUIの中心である場合、12.5Gbpsではアイマスクが通常よりも大きくなります。そのため、トランスミッタは合格しにくくなりますが、レシーバーは合格しやすくなります。基準点がUIのエッジである場合には、12.5Gbpsにおけるアイマスクは通常よりも小さくなります。そうすると、トランスミッタは合格しやすくなりますが、レシーバーは合格しにくくなります。この問題が解決されるまでは、適合性を保証するために、両方のマスクに対してテストを実施することをお勧めします。

タイミングテスト

JESD204B向けのタイミングテストの完全なリストを策定するのは容易ではありません。規格全体で少なくとも十数個のタイミング図があり、どれをトランスミッタ、チャンネル、レシーバーに適用すればよいのか即座に理解するのは困難です。また、一部は特定のサブクラス(0、1、2)にしか適用されません。コンプライアンステストの公式仕様が存在すれば、例えそれが単にタイミング仕様を1つの表にまとめただけのものであっても役に立つはずです。タイミング仕様について、一度時間をかけて系統的に確認を実施すれば、混乱を避けることができるでしょう。

タイミングに関しては、システム開発者にとって喜ばしいこともあります。それは、JESD204Bに対応する製品のタイミング仕様を規定するのは、規格を理解するよりも容易だということです。サブクラス0と同2では、規定する必要があるのはSYNC~に対するデバイスクロックのタイミングだけです。サブクラス1で規定する必要があるのは、SYSREFに対するデバイスクロックのタイミングだけです。

プロトコルテスト

PHYテストと同様に、JESD204Bではプロトコルテストに関する公式なリストは定義されていません。規格を精査し、テストすべき機能のリストを作成する作業は各ユーザに委ねられます。ここでは、実施すべきプロトコルテストをリストアップした上で簡単に解説を加えることにします。

プロトコルテストのカテゴリの1つに、テストシーケンスがあります。PHYテストを実施するためには、JESD204B対応のトランスミッタからJSPATとmodified RPATを出力できるようにしなければなりません。また、プロトコルの観点から、それらのパターンが正しいことを検証する必要があります。JESD204B対応のレシーバーとJTSPATについても同じことが言えます。オプションとしてPRBSパターンをサポートしている場合、それについても検証を行う必要があります。短いトランスポート層のパターンと長いトランスポート層のパターンのテストも必要です。それらのテストは、トランスポート層を介してリンクが正しく動作していることを実証するために実施します。このようなテストが取り入れられている理由は、システム開発者がシステムのデバッグを行う際に役に立つからです。コンポーネントメーカーの立場から言えば、デバイスがサポートするすべての動作モードにおいて、それらトランスポート層のパターンの検証を実施する必要があります。リンクの構成(コンフィギュレーション)変数の数を考慮すると、テスト項目の数は非常に多くなります。

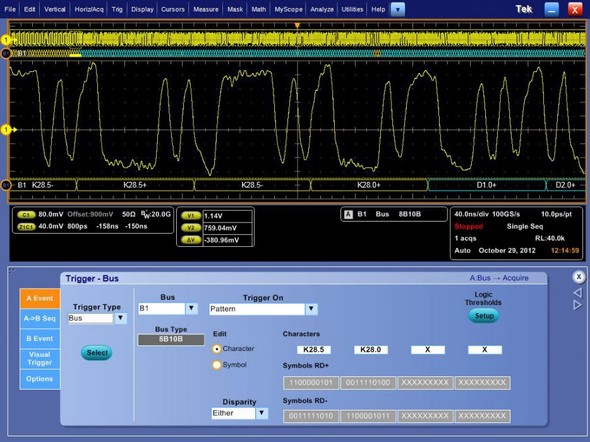

プロトコルテストについては、12.5Gbpsでテストを実施するにはどうすればよいのかという疑問が生じます。推奨される解決策の1つは、シリアルデータのデコード機能を備える高速オシロスコープを使用することです。ハイエンドのオシロスコープの多くは、JESD204Bで使用されるような8b/10bのデータでトリガするための専用ICを備えています。図2は、ILAS(Initial Lane Alignment Sequence)の最初の部分を示したものです。ここでは、JESD204Bのデータレーンの信号を6Gbpsでシリアルにデコードしています。

プロトコルテストのもう1つのグループは、ILASを中心として作成することができます。ILASは全体としてはかなり複雑ですが、個々の構成要素に分解すると、プロトコルテストについて理解しやすくなります。以下、トランスミッタで測定を行うことにより実施できるテストの例をいくつか列挙します。

- マルチフレームの長さは正しいですか?

- 各マルチフレームは、制御コード /R/ で始まり制御コード /A/ で終了していますか?

- 制御コード /Q/ は正しい位置にありますか?

- リンクのコンフィギュレーションデータの内容は正しいですか? また正しい位置にありますか?

- ILAS に含まれるデータの内容は正しいですか?

- ILAS が継続するマルチフレームの数はいくつですか?

- ILAS はすべてのレーンで同一ですか?

このように、ILASを中心とするプロトコルテストを実施することによって、さまざまな動作を検証できる可能性があります。

JESD204Bでは、ハンドシェイクについてはあまり多くの規定はありませんが、規定されている事柄についてはテストを実施するとよいでしょう。サブクラスに応じ、以下のような複数のテストを実施することができるはずです。

- SYNC~ 信号は、初期のハンドシェイク、エラーの報告、リンクの再初期化に使用できますが、トランスミッタとレシーバーのコンポーネントは、各目的に応じてそれぞれの役割を果たしていますか?

- レシーバーは、SYNC~ を正しい時刻、正しい継続期間でアサートしていますか?

- トランスミッタは、SYNC~ のアサーションの継続期間に基づいて正しく反応していますか?

- リンクを介して送信されるデータもハンドシェイク(つまりILAS)に関与しますが、その内容は正しいですか? また、SYNC~ のタイミングを基準にしていますか?

プロトコルの一部としてテストする必要がある小規模のデジタル機能も数多く存在します。例えば、以下のようなものです。

- スクランブル

- 8b/10bのエンコーディング/デコーディング

- スキュー/スキュー耐性

- コントロールビット

- テールビット

- SYNC~ 信号の結合

- フレームアライメントのモニタリング

- 訂正

これらすべての機能の検証を実施する必要があります。

プロトコルテストには、エラー処理と呼ばれるカテゴリもあります。JESD204Bの規格では、検出/報告する必要があるエラーとしては、以下のような最小限のものしか定められていません。

- ディスパリティエラー(disparity error)

- ノットインテーブルエラー(not-in-table error)

- 予期しない制御文字のエラー

- コードグループの同期エラー

しかし、実際に検出/報告される可能性があるエラーは他にもたくさんあります。JESD204Bに対応するデバイスで検出可能なタイプ(type)についても、プロトコルテストとして実施しなければなりません。タイプのプロトコルテストは、正常に動作しているリンクでは決して実行されることはありません。そのため、テストと検証は少し困難になる可能性があります。一般に、この種のテストには特殊な試験装置が必要になります。例えば、BERT(Bit Error Rate Tester)機能を備えるパターンジェネレータを使用すれば、エラーを含むパターンを生成して多くのテストを実施することができます。また、FPGAを使用してエラーパターンを生成するという方法も利用可能です。

エンファシスとイコライゼーションのテスト

JESD204Bでは、エンファシスとイコライゼーションについては何も規定していません。「プリエンファシスが必要になる場合があります」「イコライゼーション機能の実装が必要になる場合があります」といったわずかなコメントが存在するだけです。この規格ではプリエンファシスやイコライゼーションの適用は許されていると判断することはできますが、それ以外には何の指針も得られません。JESD204Bに対応するインターフェースを備えたデータコンバータ製品がエンファシスやイコライゼーションの機能も備えていた場合、どうすればよいのでしょうか。両機能を作動させるべきなのでしょうか。作動させるとすれば、どれくらいのレベルで作動させるべきなのでしょうか。この問題を解決するためには、シンボル間干渉(ISI:Intersymbol Interference)と呼ばれるジッタについて理解する必要があります。ISIとは、伝送ラインのフィルタリング効果によって生じるエッジのタイミング変動のことです。伝送ラインは、数学的には単純にローパスフィルタとしてモデル化できます。高速のシリアルデータを伝送ラインに送信すると、フィルタリングが施されて信号に歪みが生じます。エンファシスとイコライゼーションは、ISIによるフィルタリング効果を相殺します。それにより、チャンネル端での周波数応答ができるだけ周波数に対して平たんに近づくように機能します。その結果、ISIによる歪みが存在しない信号を得ることができます。

エンファシス、イコライゼーション、ISIの基本を理解したら、次のステップはそれらを設定することです。多くの人は、エンファシス/イコライゼーションを適用することにより、プリント回路基板上でどれくらいの長さのパターンを駆動できるようになるのかという疑問を抱くはずです。実際の基板設計では、ISIに影響を与える可能性がある変数が多すぎて、パターン長の観点からチャンネルについて規定することはできません。パターン幅、パターン長、ビアの有無、誘電体材料、コネクタの有無、パターンの材料、コーナ、受動部品、グラウンドプレーンまでの距離といったすべての変数がチャンネルの性能に影響を及ぼす可能性があります。では、どうすればチャンネルの特性をエンファシス/イコライゼーションと関連付けることができるのでしょうか。その答えは、挿入損失の観点からチャンネルについて規定することです。JESD204Bでは、挿入損失は周波数に対する信号の電力損失の尺度として定義されています。エンファシス、イコライゼーション、基板上のチャンネルは、挿入損失(およびゲイン)の観点から見ると、相互に関連を持っている可能性があります。関連する周波数(JESD204Bでは3/4のボーレートと規定)と挿入損失の上限値(JESD204Bでは-6dBと規定)を使用すれば、エンファシス/イコライゼーションによるゲインを選定することができます。その結果、選択した周波数における応答として、損失を上限値以下に抑えることが可能になります。例えば、9GHzにおいて-12dBの損失が生じる基板上のチャンネルにおいて、最終的に-6dBという値を得るには、エンファシス/イコライゼーションによって6dBのゲインを加える必要があります。

データコンバータのメーカーによっては、基板上の挿入損失に対するエンファシス/イコライゼーションの設定表を提供しています。多くの仮定に頼る必要がないので、これはより良い解決策になる可能性があります。

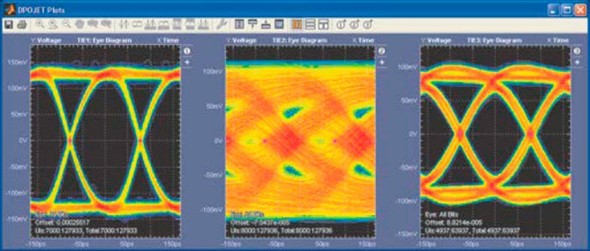

また、トランスミッタ用に上記のような表を作成する(そして、最終的なシステムの設計をエミュレートする)ために、さまざまなパターン長を備えるテスト用のボードを作製するという方法もあります。基板上のパターンの終端でアイダイアグラムを直接取得すれば、JESD204Bのレシーバー用マスクと比較することができます。さまざまなパターン長で試してみると、アイがレシーバー用マスクをかろうじて通過するパターン長が見つかるはずです。そのパターンの挿入損失を測定すれば、特定のエンファシスを設定するために必要な駆動能力が分かります。図3は、ISIのテスト用基板の終端で取得したアイダイアグラムです。一方、図4のアイダイアグラムは、ISIのテスト用基板の入力部で取得しました。データレートは5Gbpsで、エンファシスはオフにしています。この場合、ISIのテスト用基板では、4GHzにおいて8dBの挿入損失が生じます。

エンファシスの設定を変更しながら上記のプロセスを繰り返すことで、エンファシスの設定と挿入損失の関係を示す表を作成することができます。イコライゼーション機能を備えるレシーバーにも同様の手法を適用することが可能です。最初は、BERTに対応するパターンジェネレータにより、許容可能な最大トータルジッタ(ISIのジッタを除く)を出力している状態から始めます。さまざまなパターン長を備えるISIのテスト用基板を使用し、目標とするビットエラーレート(1×10-15)を超えるエラーがレシーバーから生じ始めるまで、パターン長を徐々に長くしながらテストを実行します。続いて、そのパターンの挿入損失を測定します。イコライザの設定を変更しながら、このプロセスを繰り返します。まとめると、JESD204B対応デバイスのメーカーがエンファシス/イコライゼーションのゲインのみを提供している場合には、最初の方法を使用して設定を選択すると良いでしょう。最も都合が良いのは、メーカーがチャンネルの挿入損失に対する設定表を提供しているケースです。

ところで、エンファシスとイコライゼーションという2つの機能のうち、どちらを使用するのが適切なのでしょうか。周波数応答の補正という観点からは、どちらか一方を使用すべきで、もう一方は使用すべきではないという明確な理由は存在しません。ただ、ほとんどの場合、エンファシスの方がより少ない電力で一定量のゲインを得ることができます。このことは、システムにおいて電力量が重要な意味を持つ場合、イコライゼーションではなくエンファシスを選択する理由になります。また、イコライゼーションではなくエンファシスを選択すれば、もう1つメリットが得られます。そのメリットとは、信号への影響をオシロスコープで直接観測できるというものです。

一般的には、エンファシス機能を備えるJESD204B対応トランスミッタとイコライゼーション機能を備えるレシーバーを組み合わせて使用することになるでしょう。では、両機能を作動させるべきか否かは、どのようにして判断すればよいのでしょうか。簡単に言えば、チャンネルの挿入損失を、エンファシスだけ、あるいはイコライゼーションだけでは克服できない場合に両方を作動させます。では、それぞれのゲインはどのように設定すればよいのでしょうか。挿入損失(およびゲイン)の観点から応答を規定することのメリットの1つは、損失/ゲインの足し算によって最終的な値を計算できることです。例えば、対象とする周波数において、損失が-20dBの基板上のパターン、エンファシスが6dBのトランスミッタ、イコライゼーションが8dBのレシーバーを使用するとします。その場合、トータルのゲインは-20dB+6dB+8dB=-6dBという式で算出することができます。

システム環境のエミュレーション ―― ノイズとジッタ

最終的なシステムを、ノイズとジッタが全く存在しないように設計することはできません。JESD204Bでは、システムで生じるジッタのエミュレーションについては完全に規定しています。一方で、電圧ノイズについての規定は存在しません。コンポーネントのメーカーとしては、最終的なシステムにおける電圧ノイズをエミュレートするためにノイズ耐性のテストを実施することは可能です。例えば、電源ノイズに対する耐性を測定するといった具合です。このテストでは、各コンポーネントのさまざまな電源領域にノイズを注入します。そして、コンプライアンステストが最初に不合格になるまで、ノイズの振幅を増やしていきます(SerDesでは、多くの場合、ジッタのテストが最初に不合格になります)。このテストを、基板上でノイズが発生し得る周波数範囲(数Hz〜100MHz前後)にわたって繰り返します。その結果として、周波数に対する許容可能な最大電源ノイズのプロットを得ることができます。さらに、同じテストを他のすべてのピンで実行します。すべてのテストの最終結果からは、基板設計に適用可能な実用的な推奨事項が得られます。例えば「特定の電源領域を分離すること」「このピンにはバイパスコンデンサを適用すること」「このピンの近傍には信号パターンを引き回さないこと」といった具合です。

測定時の信号品質を確保する

他の高速シリアルインターフェース技術のテストと同様に、JESD204Bのテストでも、正確な測定結果が得られるようにするためには、多くの推奨事項を適用する必要があります。また、正確な測定結果を得るためには、使用する計測器が十分な性能と信号品質(Signal Integrity)を備えていることを確認しなければなりません。以下、考慮すべき事柄をいくつか列挙します。

- ダイナミックレンジ

- オシロスコープにおいては、アンプのクリッピングが発生しないように、A/D変換のダイナミックレンジの全範囲を使用するべきです。クロック信号の測定を行う場合、クリッピングは許容できることがあります。しかし、データの信号を評価する際にクリッピングが生じると、ISIの問題を観測できなくなります。また、クリッピングは計測器のエッジ補間アルゴリズムに影響を及ぼすことがあります。

- サンプルレート

- オシロスコープを最高サンプルレートに設定すると、最高の時間分解能が得られます。そうすれば、信号とジッタを最も正確に測定することができます。例外として、時間精度を犠牲にし、より長い時間ウィンドウで測定を行いたいケースはあり得ます。

- キャプチャウィンドウ

- より長い時間ウィンドウにわたって信号を解析すると、電源のカップリングやスペクトラム拡散クロッキングのような低周波変調の影響を確認することができます。残念ながら、キャプチャウィンドウを大きくすると、解析処理にかかる時間が長くなります。多くの場合、SerDesシステムでは、追跡/拒否される CDR のループ帯域幅より下の領域で変調の影響を確認する必要はありません。

- テストポイントへの接続とディエンベッド

- トランスミッタ/レシーバーのテストポイントに、プローブを可能な限り近づける仕組みを必ず使用するようにしてください。高速信号伝送のテストを実施する場合やタイミング/振幅の測定を行う場合、トランスミッタ/レシーバーのテストポイントから引き出した長いパターンや治具において信号の不連続性が生じると、マージンテストの結果に深刻な影響が及ぶ可能性があります。

場合によっては、伝送ラインが長すぎて信号が劣化している位置にプローブの接続ポイントが存在する可能性があります。その場合、実際の信号を確認できるようにするために、伝送ラインをディエンベッドしなければなりません。そのためには、目標とするテストポイントと計測器の間の測定チャンネルのモデルを再構築する(Sパラメータによる線形法を使用)必要があります。オシロスコープで取得した波形データにそのモデルを適用することで、伝送ラインにおける劣化の原因を解明することができます(図5)

計測を行う際には、良好な信号品質が得られるように工夫を施す必要があります。それにより、JESD204Bのような高速技術の評価を正しく行い、特性を把握することが可能になります。

まとめ

JESD204Bに対応するインターフェースを利用することにより、データコンバータとロジックデバイスの間のデータ伝送帯域幅を確実に拡大することができます。このインターフェースを採用した新たな製品は、既に市場に投入されています。他の多くの高速シリアルインターフェース規格とは異なり、JESD204Bでは、コンプライアンステストの公式仕様が定められていません。そのため、設計したものを徹底的にテスト/デバッグしなければならないシステム設計者は、多くの課題を抱えることになります。幸い、JESD204Bでは、PHYテスト、タイミングテスト、プロトコルテストなどの手順を策定するための情報は十分に提供されています。

テストは、規格で定められた性能の検証と仕様への適合性の検証を行うための必須の作業です。また、テストを実施することで、エンファシス/イコライゼーションの必要性を判断したり、ノイズ/ジッタの原因を特定したりすることも可能になります。他の高速シリアルインターフェース規格の場合と同様に、正確で一貫性のあるテスト結果が得られるようにするためには、計測器の選定、セットアップ、プロービングなどに関する推奨事項を順守しなければなりません。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

提供:アナログ・デバイセズ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2020年12月8日

industry 4.0の実現へ

スマート・ファクトリーに向けた変革であるインダストリー4.0。しかしながら、インダストリー4.0がもたらすメリットは最小限しか認識されていません。エレクトロニクス業界にもたらすインダストリー4.0のメリットを、あらためて考察していきましょう。

オートメーション分野で活用されるイーサネット

産業用イーサネットが製造分野にもたらすメリットについて解説します。最初に解説するのは、プラントのオートメーション・システムに適用される技術としてイーサネットが有用な選択肢になった理由についてです。

Dust Networks オススメ記事

ワイヤレス・センサ・ネットワーク技術が半導体工場の生産効率を高めた事例を紹介しよう。これまで人手に頼らざるを得なかった175本にも及ぶ特殊ガスボンベの常時監視を大きな工事を伴わず自動化し、ガスの使用率を高めるなどの成果を上げた事例だ。