電源の電力密度向上に効く! 4つの最新アプローチ:機器の小型化に伴い高まるニーズ

機器の小型化や低コスト化を背景に、電源設計において電力密度の向上に対するニーズが高まっている。Texas Instruments(TI)はそれに応えるべく、半導体デバイスそのものの特性からパッケージ、発熱や放熱、電源回路の制御方式まで、多岐にわたるアプローチで電力密度を高める電源製品の開発に取り組んでいる。

進む小型化と、高まる電力密度向上へのニーズ

電源設計において、電力密度の重要性が高まっている。その背景には「産業機器や民生機器の小型化と多機能化、低コスト化のコンセプトがある」と話すのは、日本テキサス・インスツルメンツ 営業・技術本部の佐藤健弘氏だ。

電力密度とは、「所定のボードスペース当たりで供給できる電力」を表す指標だ。電力密度が高いということは、より小型な電源で、より多くの電力を供給できることになる。つまり、電力密度が高い電源を採用することは、「製品そのものを小型化できる」「電源が小型化した分、空いたスペースに機能を追加し、製品の差異化を図れる」「電源周りの部品点数削減による低コスト化を図れる」といった利点が生まれることになる。

佐藤氏は「電力密度を向上するという流れは産業界で何十年にもわたり見受けられている。電力密度を高めて、電源を小型化していくというトレンドは今後も続くと予測されている」と語る。Texas Instruments(TI)は、こうした電力密度向上のニーズに対し、さまざまなアプローチで取り組んでいる。

電力密度の障壁

佐藤氏は、電力密度を制限する要因として、受動部品、電力変換効率、放熱性能の3つを挙げる。

半導体スイッチや制御回路が、製造プロセス技術や集積化により、大幅に小型化されているのとは対照的に、インダクタやコンデンサ、トランスなどの受動部品は多くの場合、電源回路において最も大きなスペースを占有している。これを解消する一つの方法は、スイッチング周波数を高くすることだ。

ただし、スイッチング周波数を高めればさえよいのかというと、それほど単純な問題ではない。スイッチング周波数を高くすると、電力変換効率が下がる、つまり損失が大きくなってしまうからだ。

損失には、例えば降圧コンバータのスイッチング素子では、導通損失、充電関連の損失、デッドタイム時の損失や逆回復損失、オーバーラップ損失などがある。損失が発生するということは、つまり発熱するということでもある。そのため、電力変換効率の低下によって損失が上昇すると、発熱が大きくなり、より大きな放熱面積が必要になってしまう。小型化というニーズに逆行することになるのだ。

全体的な電力密度で重要な役割を果たす要素になっているのが、放熱性能だ。電源デバイスやソリューションサイズが小型化するということは、基板や放熱部品のサイズが縮小するということでもある。そうなると、システムレベルの熱設計は、ますます難しくなる。

電力密度向上に向けたアプローチ

このように、電源の設計にはいくつものトレードオフがあり、電力密度の向上はそれほど簡単ではないことが分かる。では、どうすればこうした課題を打破できるのだろうか。

佐藤氏は、スイッチング損失に向けた革新、パッケージの放熱特性の革新、制御方式による電力変換効率の改善、そして高集積化に向けた革新を、同時並行で進めていくことが鍵になると語る。実際、TIはこれらの技術革新に向け、長年にわたり投資を行ってきた。

電源プロセスノードの進歩とGaNの導入

まずはスイッチング損失の低減に向け、スイッチング素子(MOSFET)の特性自体を高める方法がある。MOSFETのFoM(性能指標)を向上すべく、TIは2つのアプローチに取り組んできた。電源プロセスノードの開発とGaN-FETの開発である。佐藤氏は「TIは、半導体の特性の向上、回路設計の向上、そして製造技術を含め、電源プロセスノードの革新を継続して行っている」と強調する。

例えば、以前の電源プロセスノードを用いた「TPS54319」は2MHzのスイッチング周波数で動作するが、新しい電源プロセスノードを用いた「TPS62088」は4MHzで動作する。これによりパッケージサイズは、3×3mmから1.2×0.8mmまで小型化しつつ、変換効率は同等レベルになっている。「約7年でこれだけの進化を遂げている」(佐藤氏)

さらに、半導体としてSi(シリコン)よりも優れた特性を持つGaNを用いることで、MOSFETのFoM(性能指標)が向上する。GaNデバイスの研究開発はTIがここ10年、イノベーションの最前線で投資を強化してきた分野である。オン抵抗が低い、出力電荷が小さい、逆回復時間がゼロといったGaNが本質的に持っている特性により、GaNパワーデバイスを用いたパワーコンバータは、Siより高いスイッチング周波数でも損失を大幅に低減できる。

TIの定格電圧600V、30mΩのGaN-FET「LMG342xR030」では、100V/nsを超えるスイッチング性能を持つ。スルーレートが高いので、とりわけオーバーラップ損失の低減に寄与する。

一方でGaN-FETは、ドレインやソースの寄生成分の影響を受けやすく、リンギングが発生しやすい。「そのため、ディスクリートのGaN-FETを構成しにくいという課題があったが、TIではドライバーICも搭載し、リンギングをできるだけ抑えつつ、使いやすさも追求したGaN-FETモジュールを提供している」(佐藤氏)

GaN-FETを用いることで、高い電力密度を持つ電源ソリューションを実現できるようになる。TIのリファレンス・デザインを例に挙げると、出力1kWのトーテムポール型PFC(力率補正)は電力密度が156W/in3と、従来の約2倍になっている。GaN-FETを使用した絶縁型DC-DCコンバータでは、スイッチング周波数を従来の数百kHzから1MHzまで上げられたことにより、トランスが大幅に小型化し、電力密度は従来の1.5倍に高まった。

制御方式で損失を抑える

制御方式による変換効率の向上も、損失を抑えるための効果的なアプローチだ。例えばアクティブクランプフライバック方式では、適切なクランプ制御により、ゼロ電圧スイッチング(ZVS)を実現できる。

「現在、スマートフォンやノートPCのアダプターなど70W以下の電源では、回路トポロジーとしてフライバック方式が多く用いられている」と佐藤氏は説明する。その際、疑似共振フライバック方式が用いられるのが一般的だが、同方式では原理上どうしてもスイッチングの損失とターンオフ時のリンギングが発生する。そこでスナバ回路によってリンギング発生を吸収するという対策が施される。一方、アクティブフライバック方式では、スナバ回路をFETで構成するクランプ回路に置き換えることで、スナバ回路で消費していたエネルギーをスイッチングに再利用する。これにより、リンギングの発生をなくし、ZVSを実現する仕組みだ。ZVSにより、クランプ損失やスイッチング損失をほぼなくすことができ、変換効率の向上につながる。

DC-DCコンバータの場合は、ヒステリシス制御を採用することで損失を抑えられる。ヒステリシス制御では、出力電圧が低下した際に、デューティ比ではなく周波数を変化させることで出力電圧を戻す。そのため負荷急変に対する応答速度が高く、従来の固定周波数制御(電圧モード制御/ピーク電流制御)に比べて出力電圧の低下を少なく抑えられ、その分、損失も少なくなるというメリットがある。

例えばTIのヒステリシス制御技術である「D-CAP」を用いた降圧コントローラ「TPS53114」と、電圧モード制御を用いた「TPS5124」を比べた場合、電圧降下は前者が53mVなのに比べて、後者は190mVになっている。さらに、TPS53114を用いた場合、コンデンサも、3個の22μF容量品で済むのに対し、TPS5124では100μF容量品が4個必要になる。「ヒステリシス制御を用いることは、部品点数の削減にもつながる」(佐藤氏)

パッケージ技術で放熱特性を上げる

発熱と放熱も、電力密度に直結する要素だ。基本的に部品サイズを縮小すれば、それに比例して温度は上昇する。そのため、小型化には熱の課題が常につきまとう。

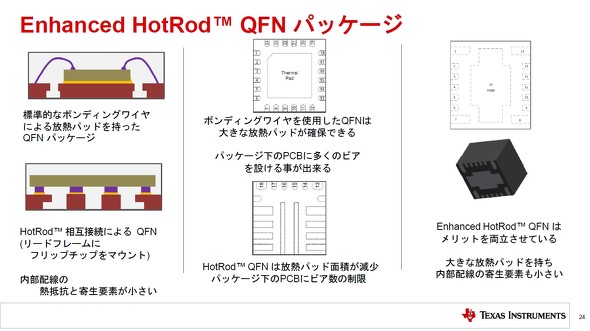

TIは半導体パッケージの放熱特性の改善にも注力してきた。「パッケージ技術の革新により、効率的にPCBやヒートシンクに放熱することが求められる」(佐藤氏)。そこでTIが開発したのが「HotRod QFN パッケージ」「Enhanced HotRod QFN パッケージ」である。

HotRod QFN パッケージは、ボンディングワイヤを用いた従来のQFNパッケージを、フリップチップタイプのパッケージに置き換えるものだ。ボンディングワイヤを排除することで、内部配線の熱抵抗と寄生成分を低減することを狙った。一方でHotRod QFNパッケージには、従来のQFNパッケージに比べてパッケージ底面の放熱パッド面積が減少し、パッケージ下のPCBに設けられるビア数が制限されてしまうという課題もあった。そこで、パッケージ底面に大きな放熱パッドを設けたEnhanced HotRod QFNパッケージを開発。標準的なQFNパッケージとHotRod QFNパッケージ、両方の利点を兼ね備えたものになっている。

「ただし、半導体のパッケージだけでなく、PCB上で電源部品のレイアウトを最適化したり、ヒートパイプや熱伝導グリス/シートを使ったりと、PCBおよびシステムレベルの全てで熱抵抗を改善していくことも重要だ」(佐藤氏)

統合技術を駆使して設計も簡素化

高集積化も、電力密度を高める有効な手段になる。佐藤氏は高集積化のメリットとして「部品点数やPCB占有面積の最小化や、寄生要素の最小化による性能の改善、設計工数の削減とPCBレイアウトの簡素化が挙げられる」と語る。

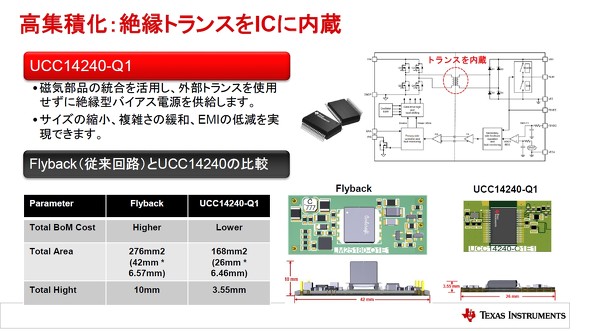

TIの同期整流降圧コンバータ「LMQ61460-Q1」は、入力コンデンサをICに内蔵したことで寄生成分を最小限に抑え効率が向上している。絶縁型DC/DCモジュール「UCC14240-Q1」は、絶縁トランスをICに内蔵した製品だ。従来のフライバックコンバータに比べ、部品点数と基板スペースを大幅に低減できる。

基板内にICを積層した電源モジュール「MicroSiP」「MicroSiL」も提供している。ICが基板内に埋め込まれていることに加え、インダクタやコンデンサがパッケージ表面に実装されている3次元構造が特長だ。MicroSiPにはコンデンサが、MicroSiLにはインダクタが実装されている。「3次元に積層されているのでスペース効率がよく、PCBでは実現できないサイズに収まっている」(佐藤氏)。例えば、MicroSiLモジュールである「TPS82085」は、ディスクリートで構成した場合に比べ、PCBの占有面積は40%以上小さくなっている。

「機器の小型化のニーズに対応するためには、電源回路の高密度化は必須になる」と佐藤氏は述べる。電力変換効率から半導体パッケージの放熱、電源回路の制御方式、電源デバイスの高集積化まで、電力密度の向上にさまざまなアプローチに取り組むTIの最新の電源製品を、ぜひチェックしてみてほしい。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ合同会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2023年1月26日

日本テキサス・インスツルメンツ 営業・技術本部の佐藤健弘氏

日本テキサス・インスツルメンツ 営業・技術本部の佐藤健弘氏