電源回路設計の手順と勘所(4) FPGAの電源トポロジーを最適化する:【ビデオ講座】アナログ設計の新潮流を基礎から学ぶ

【ビデオ講座】電源回路設計の手順と勘所(4) FPGAの電源トポロジーを最適化する (クリックで動画再生)

FPGAに電力を供給する電源回路の設計は、決して簡単ではない。実際に開発現場では、電源回路に関するトラブルが少なくないようだ。トラブルが発生してしまう理由としては、電源電圧の低下や供給電流の増大、出力リップル電圧の許容値減少などが挙げられる。

こうしたトラブルを未然に防ぐことを目的に、米National Semiconductor社では、FPGAの電源回路設計に向けたオンライン設計支援ツール「WEBENCH® FPGA Power Architect」を開発し、現在サービスを展開している。前回は、FPGAの電源回路に課せられた複数の要件を一つ一つ解説するとともに、複数の電源レールの設定方法を紹介した。今回は、その設定を利用して、実際に電源トポロジーの最適化を行った。

電源回路の実現手段にも注目せよ

電源トポロジーの最適化を実行する前に、前回の設定内容を確認しておこう。設計対象に選択したFPGAは、米Altera社の最新シリーズ「Startix V」の中でロジック・エレメントが最も多いチップ「5SEBA」である。電源レールは全部で12個あり、その中にはFPGAのコア向けに向けた0.85V、20Aという低電圧/大電流の負荷が含まれている。「出力リップル電圧」や「フィルタ」、「別電源を使用」、「ソフトスタート時間」、「Sequencing」などの要件については、FPGAベンダーが指定する値や設定をそのまま利用した。

電源トポロジーの設計を実行するには、電源レールの設定画面の右端にある「プロジェクト要件を送る」ボタンを押す。すると、シミュレーション(解析)が自動的に始まる。今回は、オプティマイザ・ダイヤルを「1」と「3」、「5」に合わせたときの結果を元に、最適な電源トポロジーを選択してみよう。

各々のダイヤル位置によって3つづつ候補が計算され、番号が振られるので、解析結果として、全部で9個の電源トポロジーが得られた注1)。この中で最も変換効率が高いのは、「500」番である。7Vの中間バス電圧を利用する電源トポロジーで、変換効率は82.86%に達する(図1)。非常に高い変換効率だ。ただし、総フットプリントは、6963mm2とかなり大きい。一方、総フットプリントが最も小さいのは「100」番である。5Vと2Vという2つの中間バス電圧を使う電源トポロジーで、総フットプリントは「500」番の約1/3の2224mm2と小さい(図2)。しかし、変換効率は57.90%と低くなってしまう。従って、変換効率を重視するのなら「500」番、総フットプリントを重視するのなら「100」番という選択になる。

ただし、ここで「502」番に注目してほしい。電源トポロジー自体は、総フットプリントが最も小さい「100」番と同じである5Vと2Vの中間バス電圧を使う構成である(図3)。総フットプリントは7883mm2と極めて大きくなってしまうものの、変換効率は79.02%と比較的高い値が得られる。「100」番に比べると変換効率は約20ポイントも高い。同じ電源トポロジーにもかかわらず、変換効率と総フットプリントがなぜこんなにも違うのか。

図3 電源トポロジーは「100」番と同じだが、変換効率が高い解析結果

図3 電源トポロジーは「100」番と同じだが、変換効率が高い解析結果「502」番の解析結果である。電源トポロジーは図2と同じだが、変換効率は79.02%と比較的高い。ただし、総フットプリントは7883mm2と極めて大きい。

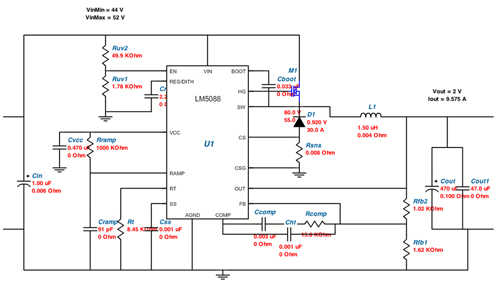

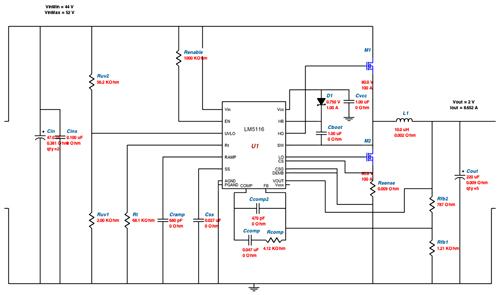

その理由について、ナショナル セミコンダクター ジャパンのマーケティング部門で電源関連ICを担当する山田浩二氏は、「使用している電源ICにある」と指摘する。例えば、入力電圧である52Vから中間バス電圧の5Vを作成する電源ICに、「100番」では電源制御IC「LM5088」、「502」番では同じく電源制御IC「LM5116」を採用している。LM5088とLM5116の違いは整流方式にある。LM5088はダイオード整流(図4)、LM5116(図5)は同期整流を採用する。一般に、ダイオード整流は、回路方式が簡単なため外付け部品が少ないというメリットがある一方で、変換効率の点で同期整流に大きく劣るというデメリットがある。このため「502」番は、「100」番に比べて高い変換効率が得られるものの、総フットプリントが大きくなってしまったわけだ。

図4 ダイオード整流を採用したDC-DCコンバータ回路

図4 ダイオード整流を採用したDC-DCコンバータ回路「100」番の電源トポロジーで採用した、52Vから2Vを作るDC-DCコンバータの回路図である。ダイオード整流を使う電源制御IC「LM5088」を採用した。

図5 同期整流を採用したDC-DCコンバータ回路

図5 同期整流を採用したDC-DCコンバータ回路「502」番の電源トポロジーで採用した、52Vから2Vを作るDC-DCコンバータの回路図である。同期整流を使う電源制御IC「LM5116」を採用した。制御方式は、National Semiconductor社独自の「エミュレーテッド・カレント・モード」である。

採用する電源ICが電源トポロジーを左右する

今回のシミュレーション(解析)で得た結果では、もう1つ注目してもらいたい点がある。それは、「100」番と「502」番はいずれも、52Vを2Vに前段のDC-DCコンバータで変換して、後段のDC-DCコンバータでFPGAのコア部に供給する0.85Vを作成する電源トポロジーを採用している点である。通常、中間バス電圧は、高めに設定するケースが多い。電圧を低くすると電流量が増え、電源配線での電圧ドロップが大きくなってしまうからだ。しかし、今回はかなり低い電圧である2Vを中間バス電圧に採用した。5Vや7V、12Vを選択した方が良いように思える。

こうした疑問について山田浩二氏は、「52Vから0.85Vを作成する場合、変換の段数は通常、2段にするだろう。このとき、前段と後段のどちらのDC-DCコンバータで、大きく電圧を落とすかが問題になる。入出力電圧差が大きければ大きいほど、変換効率が低くなるからだ。仮に、後段で大きく落とす方法を選択したとしよう。この場合は、前段である程度低い電圧に落としているため、後段で扱う電流量が大きくなっており、発熱量が膨大になってしまう。従って、あまり賢明な選択とは言えない。そこで、前段で大きく電圧を落とす方法を選択した」と説明した。

ただし、前段で52Vから2Vと大きく電圧を落とすことを選択した背景には、National Semiconductor社の独自技術の存在がある。「エミュレーテッド・カレント(電流)・モード」という技術だ。「この技術を用いれば、入出力差が非常に大きな電圧変換が可能になる」(同氏)という。前述のLM5116にエミュレーテッド・カレント・モードが採用されている。

上記の疑問に対する答えはもう1つある。それは、後段のDC-DCコンバータに入力する電圧が高いと、使用するインダクタの選択が難しくなることである。一般にインダクタでは、直流電圧を印加するとインダクタンス値が減るという現象が発生する。いわゆる直流重畳特性である。このインダクタンス値の減少幅は、直流電圧が高ければ高いほど大きくなる。つまり、後段のDC-DCコンバータへの入力電圧を高く設定すると、インダクタンス値の減少幅が大きくなり、その分だけインダクタの選択が難しくなるわけだ。

このように、FPGAに電力を供給する電源トポロジーを最適化するには、中間バス電圧の有無やその電圧値に加えて、DC-DCコンバータの回路構成、インダクタの選択なども考慮する必要がある。この作業をすべて、エンジニアの頭の中で実行するのは難しい。従って、オンライン設計支援ツールを活用すれば、より少ない作業量と作業時間で最適解を得られるようになるだろう。

注1)解析結果は、必ずしも常に一定というわけではない。外付け部品で使用するコンデンサやインダクタ、ダイオードなどの登録データが頻繁にアップデートされているからだ。例えば、入手が困難になりデータが削除されたり、新製品の発売で新たにデータが登録されたりすることがある。なお、BOMコストの欄が「0.00$」と表示されることがある。これは、部品表(BOM)に含まれる部品のうち、少なくとも1つの部品の価格が不定の場合に表示される。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード