性能で一歩先を行くTIのクロック製品、産業機器や通信機器などで効果を発揮:【講座】回路設計の新潮流を基礎から学ぶ

マイコンやFPGA、ASIC、ASSP、メモリなどのデジタル・チップはもちろんのこと、通信用チップやAD/DAコンバータなどのアナログ・チップの動作にも欠かせないクロック信号。それを供給する重責を担っているのがクロック/タイミングICである。

テキサス・インスツルメンツ(TI)は、このクロック/タイミング市場において高い競争力を誇っている。TIは、データ・コンバータやアンプ、パワー・マネジメントなどのアナログ製品分野でも、業界をリードしている。競合品に比べて、高い性能が得られる製品を市場に供給していることが最大の理由だ。

クロック/タイミング市場においても同様だ。TIの製品は、クロック/タイミング製品としての基本性能が競合品を上回る。具体的には、ジッタが少ないこと、位相ノイズが低いこと、スプリアスが低いことなどが挙げられる。

こうした性能が高ければ、クロック/タイミング製品を搭載した電子機器の特性を向上させられる。例えば、通信機器であればデータ伝送速度や受信感度の向上。産業機器や医療機器であれば、さまざまな制御や測定の精度を高めることが可能になる。もちろん、一般的な民生機器や携帯機器に使っても、その効果が得られる。しかしTIによると、「高性能なクロック/タイミング製品の効果は、高い特性が求められる通信機器や産業機器、医療機器、車載機器などで生かされる。従って、TIではこうした電子機器の市場に注力して、製品を展開している」という。

4種類の製品を投入

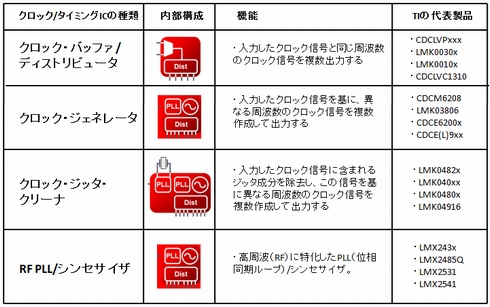

それでは、TIが市場に投入しているクロック/タイミング製品を具体的に見ていこう。TIの製品は大きく4つの種類に分類できる(図1)。具体的には、「クロック・バッファ/ディストリビュータ」、「クロック・ジェネレータ」、「クロック・ジッタ・クリーナ」、「RF PLL/シンセサイザ」の4つである。

図1 4種類のクロック/タイミング製品

図1 4種類のクロック/タイミング製品TIでは、「クロック・バッファ/ディストリビュータ」、「クロック・ジェネレータ」、「クロック・ジッタ・クリーナ」、「RF PLL/シンセサイザ」という4種類の製品を市場に投入している。

1つめのクロック・バッファ/ディストリビュータは、入力したクロック信号の周波数を変えずに、それをそのまま複数のクロック信号に分岐させて出力するものだ。同じ周波数のクロック信号を必要とする複数のデジタル・チップやアナログ・チップに、1個のクロック信号源と1個のクロック・バッファ/ディストリビュータだけで対応できることになる。そのため、部品コストを削減できるほか、プリント基板のレイアウトをシンプルにできる。

2つめのクロック・ジェネレータは、入力したクロック信号を基に、異なる周波数のクロック信号を複数個作成して出力するものだ。位相同期ループ(PLL:Phase Locked Loop)と電圧制御型発振器(VCO:Voltage Controlled Oscillator)などの回路から構成される。

この製品のメリットは、前述のクロック・バッファ/ディストリビュータと同じだ。つまり、1個のクロック信号源と1個のクロック・ジェネレータで、複数のデジタル・チップやアナログ・チップにクロック信号を供給できるため、部品コストの削減と、基板レイアウトの簡略化を実現できることである。ただしクロック・ジェネレータは、異なる周波数のクロック信号を供給できる点で、クロック・バッファ/ディストリビュータに比べてフレキシビリティ(柔軟性)が高いと言える。

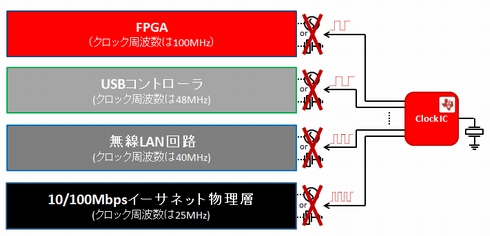

例えば、図2のような対応が可能になる。クロック周波数が100MHzのFPGAと、40MHzの無線LAN(Wi-Fi)回路、48MHzのUSBコントローラ、25MHzの10/100Mbpsイーサネット物理層(PHY)に対応する場合、従来であれば水晶デバイスを使ったクロック信号源が必要だった。ところが、クロック・ジェネレータを使えば、さまざまな周波数のクロック信号を作成できる。このため1個のクロック信号源と1個のクロック・ジェネレータだけで、4つの異なる周波数のクロック信号を供給できるわけだ。

図2 クロック・ジェネレータを使った回路を簡素化

図2 クロック・ジェネレータを使った回路を簡素化この例では、従来は、4つ水晶デバイスが必要だった。しかし、クロック・ジェネレータは、さまざまな周波数のクロック信号を作成できるため、1個のクロック信号源と1個のクロック・ジェネレータだけで、4つの異なる周波数のクロック信号をまかなえるようになる。従って、コストの削減と基板レイアウトの簡素化を実現できるようになる。

3つめのクロック・ジッタ・クリーナは、入力したクロック信号に含まれるジッタを除去する機能を搭載したクロック・ジェネレータである。2つのPLLで構成した「デュアル・ループPLL」とVCOからなる。この製品のメリットは、ジッタを大幅に低減できる点にある。TIの製品ではRMSジッタ:50fs以下に抑えることが可能だ。

4つめのRF PLL/シンセサイザは、使用する周波数領域が高い電子機器に向けたものだ。無線通信機器や医療機器、計測器、車載機器などが主な用途になる。PLL単体の製品のほか、PLLにVCOを組み合わせたシンセサイザも用意している。対応する周波数帯域、消費電力や雑音特性の違いなどで、複数の製品を用意している。

良好な位相ノイズやノイズ・フロアが得られる

前述のように、TIが提供するクロック/タイミング製品の性能は、競合品に比べて高い。どの程度、高い性能が得られるのか。いくつかの製品の具体例を紹介しよう。

クロック・ジェネレータの「LMK03806」は、ジッタが小さく、ノイズ・フロアが低いことが特長だ。Gbイーサネット物理層などで用いられる156.25MHzのクロック信号を発生させた場合、ジッタは12k〜20MHzの周波数範囲において0.200psRMS、ノイズ・フロアは−160dBc/Hzという値が得られた(図3)。いずれも、業界トップクラスの数字だ。

図3 クロック・ジェネレータのジッタ/ノイズ・フロア特性

図3 クロック・ジェネレータのジッタ/ノイズ・フロア特性「LMK03806」の場合である。ジッタは12k〜20MHzの周波数範囲において0.200psRMS、ノイズ・フロアは−160dBc/Hzといずれも良好だ。

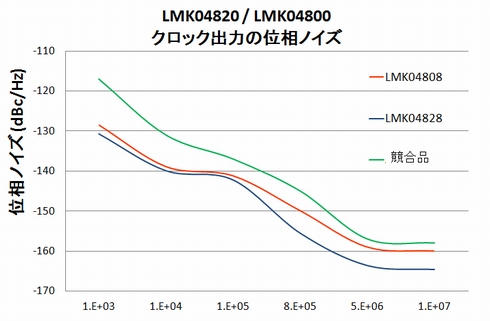

次は、クロック・ジッタ・クリーナの「LMK048xx」についてだ。LMK048xxの特長は、位相(フェーズ)ノイズが低い点にある。TIによると、「業界で最も位相ノイズが低いクロック・ジッタ・クリーナである」という。競合品と比較した結果が図4である。「LMK04808」と「LMK04828」の2製品とも、位相ノイズは競合品に比べて低く抑えられている。その差は、オフセット値によって異なるが3〜10dB程度である。なお、LMK04808は2.9GHz出力のVCOを搭載したクロック出力が最大14本の製品。LMK04828は、シリアル・インタフェース規格「JESD204B」に対応しており、最大クロック出力周波数は2.9GHzで、クロック出力数は最大15本の製品である。

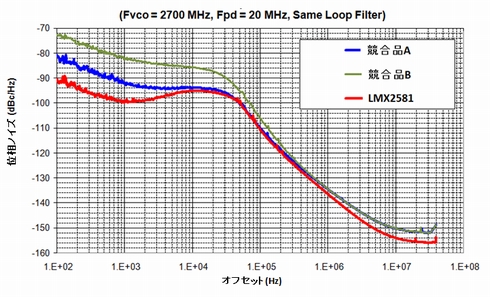

最後に、RFシンセサイザの「LMX2581」を競合品と比較してみた。LMX2581の特長も、位相ノイズが低い点にある。VCOの出力周波数が2.7GHzのとき、オフセット値を変えて位相ノイズを測定した結果が図5である。位相ノイズは、10dB〜20dB程度低く抑えられている。位相ノイズ性能指数(FOM:Figure of Merit)は、LMX2581が-229dBc/Hzで、競合品は-213dBc/Hzである。従って、LMX2581の方が高い性能が得られることが分かる。なお、LMX2581は出力周波数範囲が50M〜3.76GHzのシンセサイザである。

設計を支援するツールも用意

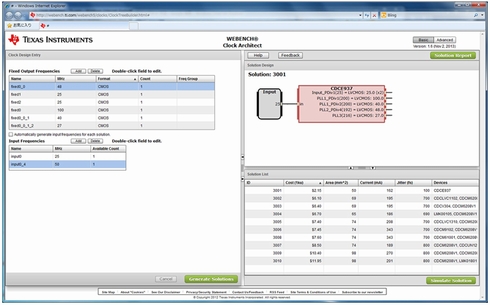

TIでは、性能の高いクロック/タイミング製品を市場に投入するとともに、それを電子機器に適用する設計作業のサポートに向けたツールの拡充にも取り組んでいる。TIが無償で提供するWEBENCH®オンライン設計支援ツールの中で提供しているクロック/タイミング製品向けツール「WEBENCH Clock Architect」がそれだ。

このWEBENCH Clock Architectは、複数のツールで構成されており、最適なクロック/タイミング製品を探すときに有用である(図6)。これは、クロック入出力の本数や周波数、形式などの情報を打ち込むと、性能(ジッタ、位相ノイズ)やコスト、消費電力などの観点で見た場合に最適な製品を提案してくれる。TIによると、「TIのクロック/タイミング製品は数多い。しかし、WEBENCH Clock Architectを使えば、すぐに最適な製品を見つけられる」という。

さらにWEBENCH Clock Architectには、複数の水晶デバイスを使って構成している電子機器のクロック供給網(クロック・ツリー)を、クロック・ジェネレータなどを利用して簡略化する方法を提案する機能もある。これを使えば、コストの削減や基板レイアウトの簡素化などが可能になる。

このほか、WEBENCH Clock Architectの中には、ループ・フィルタの設計や特性のシミュレーションなどを実行できるツールも用意されている。このツールは現在、機能の拡張や対応製品の拡充を急いでいる。

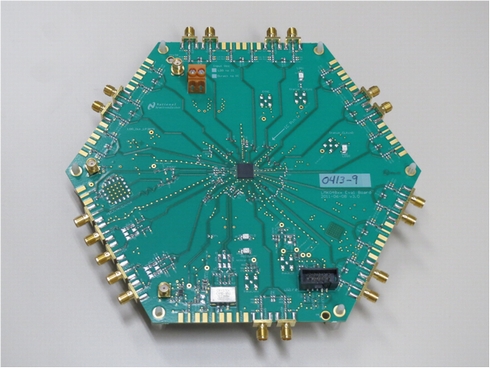

評価ボードも数多く用意している(図7)。オンライン設計支援ツールと評価ボードを組み合わせて利用すれば、電子機器のクロック/タイミングに関する設計に費やすコストや労力を大幅に削減できるようになる。

【関連資料】

クロック&タイミング・ソリューション(PDF:1.4MB)

高い柔軟性と使いやすさを実現するTIの包括的製品ポートフォリオ

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード