基板設計がうまくいかない、高速信号を手なずけるには

とどまることを知らない『高速化』

基板上に引いた信号線、この信号の高速化がとどまるところを知らない。2010年時点で既にIC内部の速度を基板上の信号速度が上回ってしまった。信号がこれほど高速になると、配線を「伝送線路」として捉える必要がある。

数十[mm]の配線であっても信号を送り出すドライバと受け取るレシーバの間で信号が変化してしまう。伝送線路では信号を正しくやりとりすることが難しくなる。これを避けるためには信号の立ち上がりや立ち下がりの時間変化率、配線長の2点について理解を深めておく必要がある。

米KEI Systemsで代表を務める前田真一氏(図1)は、ピーバンドットコムが開催した「P板.com 技術セミナー」(2015年9月16日)において、冒頭のように基板の課題をまとめた。「経験によって基板の問題を切り分けた後は、論理で解決する。どちらも必要であり、今回は論理を紹介する。伝送線路の基礎を学ぶことで確かな論理を身につけてほしい」(同氏)。

「特定の配線レイアウトにおいて伝送線路の課題を解決するには、IBIS(Input/Output Buffer Information Specification)のような解析モデルを用いたシミュレーションが必要不可欠だ」(同氏)。だが、IBISやシミュレーションソフトを使いこなすには、何が問題になっているのかを理解しておく必要がある。

今回は高速データ転送が引き起こす課題を理解するために、前田氏が講演で扱った転送方式や信号の基礎、伝送線路の定義を説明する。反射や終端、配線間の結合やクロストークノイズ、IBISやシミュレーションは次回紹介する。

高速化が進むと何が起こる

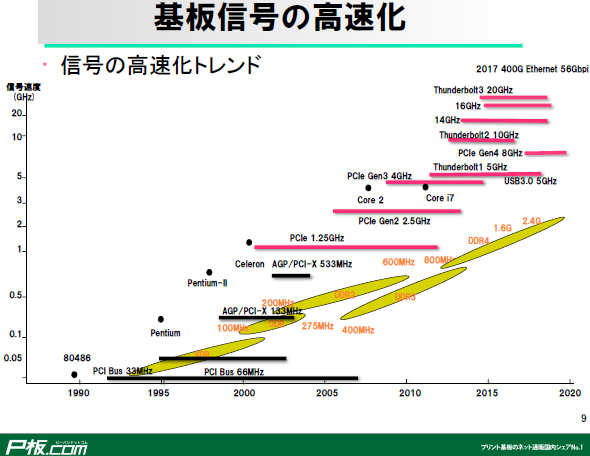

データ転送には、複数の信号線を用いて同時に信号を送るパラレル転送と、1本(1対)の信号線を用いるシリアル転送のいずれかを用いる。シリアル転送が本格化したのは、2000年ごろだ(図2)。それまで100[MHz]程度にとどまっていた転送速度が、シリアル転送によって一気に1.25[GHz]に向上、その後、プロセッサを追い越して、20[GHz]にまで高まったことが分かる。

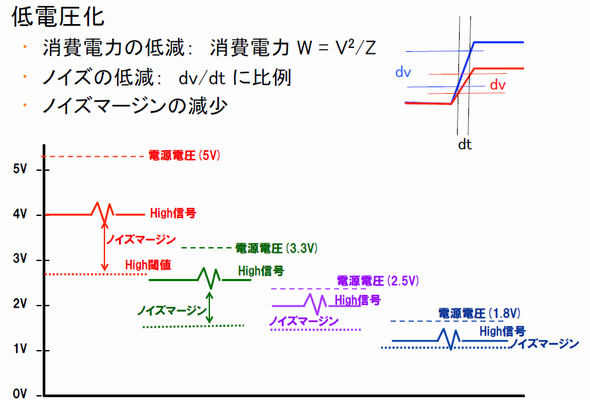

これと同時に進んだのが、低電圧化だ(図3)。当初の5[V]が1.2[V]以下にまで下がっている。これは消費電力が電圧の二乗に比例するためだ。低電圧化には副作用もある。現在のデジタル回路は0、1を表す電圧がきれいな矩形波として現れることはない。電圧が揺れ信号にノイズが載る。低電圧化が進むと、ノイズとして許容できるマージンが減ってしまうのだ。逆に言えば、同じ大きさのノイズであっても、低電圧化によってより影響が大きくなる。

パラレル転送の課題は配線長にあり

「パラレル転送では64ビットのデータを1[GHz]で転送することは無理だ」(前田氏)。これは複数の信号線間の同期を取ることが困難であるため。

「転送のマージンを考慮に入れなくても500[ps]でデータを転送する必要があり、マージンを入れるとこれが100[ps]とさらに短くなる。配線遅延は1[mm]で7[ps]にもなるため、配線できない上に厳密に同じ長さの配線を設計できたとしても、後ほど紹介する理由によって信号のタイミングがずれてしまう」(同氏)。

速度に劣るパラレル転送、だが、パラレル転送がなくなることはないという。「シリアル転送は確かに高速だが、同時に複数のビットを得る必要があるメモリやCPUでは、パラレル転送を使わなければリアルタイム処理が実現できないからだ」(同氏)。例えば、画像処理に用いるGPUでは256[ビット転送]が利用されている。ゲーム機「PlayStation 4」「Xbox One」は8[ビット]単位の入出力を行うメモリを16個、CPUに接続して同時に256[ビット]を転送している。この他、ICチップ内部のバスやPCIバスに向く。いずれもリアルタイム処理が必要だからだ。

基板上の配線を考えた場合、パラレルバス配線の課題は2つあるという。1つ目は8ビット転送で10本の信号線が必要であるため、配線面積が広くなること。

2つ目はデータのタイミング(同期)をとる必要があるために、基板上の同層にレイアウトする必要があることだ。「基板厚が1.6[mm]の場合、ビアを1つ打つと10〜15[ps]の遅延が起きる」(同氏)ためだ(図4)。配線が曲がる際には配線長をそろえるためにわざと蛇行したミアンダ配線が多用されているものの、さらに配線面積が増えてしまう。「加えて、クリップ状に蛇行させると後ほど解説する自己クロストークが起きやすくなるため、高さが低い矩形波のような配線のレイアウトが必要になる」(同氏)。

シリアル転送の課題は逆相ノイズ

シリアル転送は1対の信号線(レーン)を用いて、nクロックで1[バイト]のデータを転送するため、リアルタイム処理には向かないものの、同期がたやすく、転送速度が高い。従って、バッファリングが前提となっている入出力バスやデバイスバスに最適な転送方式だ。リアルタイム処理が不要であれば、レーン数を増やすことでもさらに高速化を実現できる。

シリアル転送に同期の問題が生じないのは、転送すべきデータにクロック回路からの信号を合成し、転送先で分離するSerDes方式を採っているからだ。元データのビット列が連続した0や連続した1の場合でも、クロックを確実に分離できるよう、当初は8-10変換方式(パラレルの8[ビット]をシリアルの10[ビット]に変換)が使われていたものの、変換クロック精度が技術の向上によって高まってきたため、最新のPCI Express(PCIe) Gen3では128-130変換方式を実用化できた。8-10方式を採用していたPCIe Gen2では転送速度のうち20%を、クロックを切り出すための信号が占めていたため、クロック信号2.5[GHz]に対してデータ転送速度は5[Gビット/秒]ではなく、4[Gビット/秒]に落ちていた。PCIe Gen3では、クロック信号4[GHz]に対して、データ転送速度は8[Gビット/秒]となった。これは第3の高速化技術ともいえるだろう。

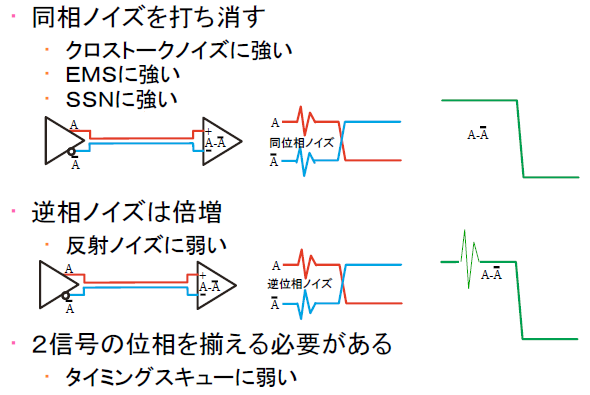

シリアル転送は、正負、逆位相の信号を同時に転送するデファレンシャル(差動)信号方式を必ず利用する。差動信号方式を採ると、信号電圧が2倍に拡大し、閾値に対して、ノイズマージンが倍になる。さらに、逆位相の信号の差をとることで、クロストークによってうまれる同相ノイズを打ち消す効果が得られる(図5)。

シリアル転送の2つの弱点も差動信号から生まれる。図5にあるように信号の反射によって生じる逆相ノイズが倍増してしまうのだ。さらに、2つの信号の位相をそろえる必要があるため、タイミングスキューに弱い。

基板上にシリアル転送線を設計する場合は、2本の差動信号を対に配線し、差動配線間の位相に注意しないといけないとした。

タイミングが課題となる高速システム

「高速システムでは電圧よりも、タイミングが最大の課題となる」(同氏)。

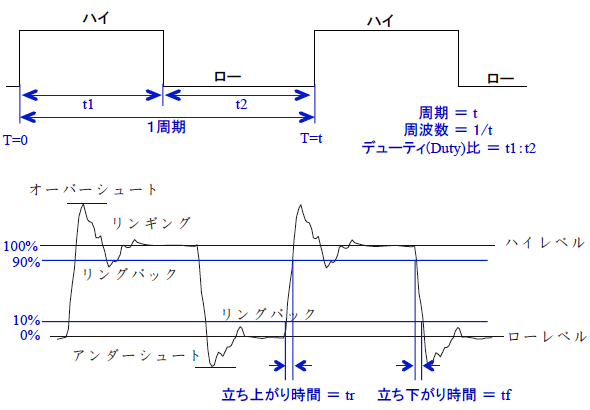

電圧の課題は理解しやすい。理想的な状態では矩形波になるデジタル信号は、図7のような複雑な波形となる。ロー(0)からハイ(1)に変わる際には、本来のハイの電圧を超えてオーバーシュートし、安定するまでリンギングとリングバックが起きる。ハイからローでもアンダーシュート以下同じ挙動を示す。

このような信号を受けたレシーバはローとハイを正確に判別できなければならない。あるICをとっても、ゲートによって電圧変化は異なる。ICのメーカーは出荷時などの検査によって保証値から外れたICをとり除くものの、基板の設計によってはノイズマージンが小さくなり、レシーバの誤動作につながる。

タイミングの課題はこうだ。信号が高速になることで1周期の時間が短くなる。すると、周期の長さの誤差(ジッタ)の影響が大きくなる。「例えばDDR4メモリだと、1[GHz]で動作する製品がある。クロック信号の立ち上がりと立ち下がりごとに信号を送るDouble Ratedデータ転送方式を採るため、信号を送る幅は500[ps]だ。もしも100[ps]のジッタが生じたとしたら、残りの時間で10個のデータを転送する必要がある。PCIe Gen3やUSB 3.1ならもともと200[ps]しか余裕がなくなる」(同氏)。

伝送線路の目安は1[ns]当たり25[mm]

ある配線が信号をゆがみなく伝える理想線路となるのか、それとも伝送線路となるのか、どうすれば判断できるのだろうか。

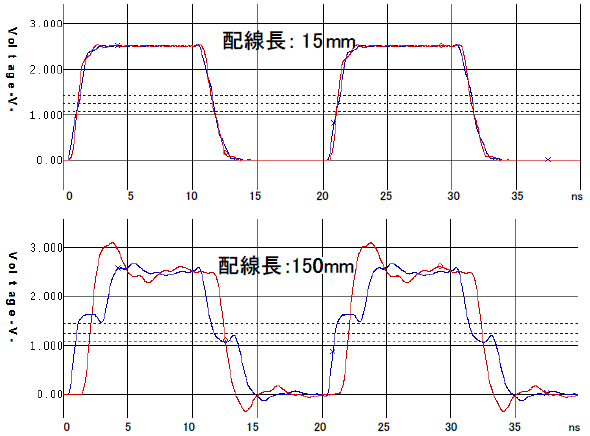

前田氏によれば、波長(周波数)と配線長さで決まるという。例えば周波数50[MHz]で信号を送るとしよう。配線長が15[mm]と短いときには、ドライバ(青)とレシーバ(赤)の波形はほとんど一致しており、ノイズもない(図8)。ところが配線長を150[mm]に伸ばすと、タイミングはもちろん、波形も大きく異なる。伝送線路としての振る舞いが強くでている。

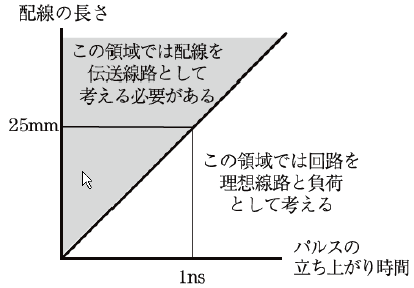

「信号の立ち上がり、立ち下がり時間がそれぞれ1[ns]のとき、配線長25[mm]が判断の分かれ目になる」(同氏、図9)

他の配線との結合を考える

伝送線路の問題は単独の配線でも起きる。さらに基板上に複数の配線をレイアウトすると、別の問題が起きる。結合だ。

結合には配線Aが生み出す電界によって、配線Bが影響を受ける電界結合(キャパシタンス)と、生み出す磁界による磁界結合(相互インダクタンス)の2種類がある。いずれも電流の時間変化率に比例しており、信号の立ち上がりや立ち下がりが速いほど、大きな電界、磁界が発生し、強い結合が起きる。信号が高速化するほど、状況が悪化するということだ。

周囲の配線に信号が流れると、影響を受ける。この問題を解決する方法は複数あるものの、現実的なのは常に一定の状態を保つ電源やグランドと結合することによって、周囲の配線の影響を和らげる手法だ。「95%の結合をグランドなどが占めるようにすれば、残り5%の結合が周囲の配線との間で残っていても、安定する」(同氏)。

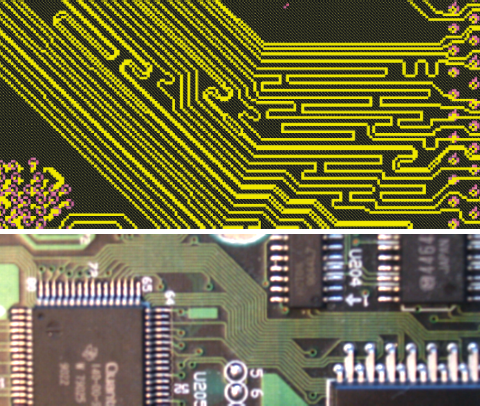

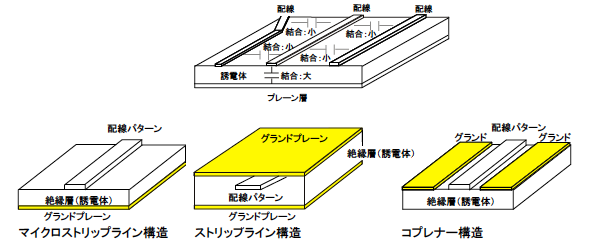

基板上でグランドなどと結合させる手法は確立している。図10のように黄色で示したグランドを配線パターンの近くに配置する。「複数の手法を組み合わせることができれば、なおよい。例えばマイクロストリップライン構造とコプレナー構造だ」(同氏)。

結合を数値で表した指標が特性インピーダンスと差動インピーダンスだ。

特性インピーダンス(Zo)は、配線自体がもつ単位長さ当たりのインダクタンス(L)とキャパシタンス(C)によって決まる。Zo=√(L/C)という関係で計算できる。LとC自体は配線幅や配線間隔、基板の誘電率で決まる。

Lは周波数に比例し、Cも周波数に比例するため、Zoは信号の周波数とは関係なく一定だ。配線長さが増えても、CとLが同様に増えるため、やはり依存しない。ところが、Cは基板材料の誘電率εに強く依存する。

「基板上の信号の速度が光速の約半分になるのは、εのためだ。FR-4(ガラス布基材エポキシ樹脂)の場合εrは4.3程度だ。V=c/√ε(=1/(Zo・C)であることから、計算で求めることができる」(同氏)。これによって配線長1[mm]当たり、6〜7[ps]の遅延が生じる。

シリアル転送では差動信号のインピーダンス(差動インピーダンス、Zdiff)も考慮しなければならない。差動信号では配線は常に平行になっている。

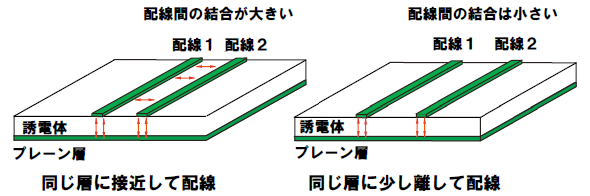

配線間隔が狭い場合、配線間の結合は強くなり、Zdiff < 2*Zoという関係にある。配線間隔を広く取ると、配線間の結合は弱くなり、Zdiff 〜 2*Zoとなる。

配線間隔が広がると差動インピーダンスは高くなるものの、ある値を超えるとほぼ一定になる。「図11の右のように、差動信号の配線を離しても、プレーン層との結合が生じるためだ。特性インピーダンスを配線1本当たり50[Ω]とると、合計で100[Ω]になる。実際には、配線面積が増えてしまうため、図11の左のように配線することが一般的だ。ただし、プレーン層との特性インピーダンスが50[Ω]のままでは配線間の特性インピーダンス、例えば15[Ω]を引く計算となり、合計して85[Ω]しかとれない。つまり、プレーン層との特性インピーダンス自体を55[Ω]にする設計が必要だ」(同氏)。

特性インピーダンスや差動インピーダンスの設計が、高速信号に与える影響は大きい。ジッタやノイズが増えて波形が劣化するからだ。具体的には反射ノイズの発生を抑え、終端の工夫へとつながっていく。詳細は次回解説する。

セミナー 参加者募集中

テーマは「伝送線路の基礎」

本記事で紹介したP板.com主催の技術セミナー「伝送線路の基礎」が2015年10月13日に大阪で、2015年10月14日に名古屋で開催されます。伝送線路配線にご興味のある方、お困りの方は是非ご参加ください! 参加費は無料。現在、P板.comの特設ページで参加を受け付けています。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

提供:株式会社ピーバンドットコム

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年11月8日

技術セミナー 開催!!

本記事で紹介したP板.com主催の技術セミナー「伝送線路の基礎」が2015年10月13日に大阪で、2015年10月14日に名古屋で開催されます。伝送線路配線にご興味のある方、お困りの方は是非ご参加ください! 参加は無料です。

図1 米KEI Systemsの前田真一氏

図1 米KEI Systemsの前田真一氏 図2 信号の高速化トレンド パラレル転送の信号速度(黒線)、シリアル転送の信号速度(赤線)、プロセッサの動作周波数(黒点)、メモリの信号速度(黄色)を示した。

図2 信号の高速化トレンド パラレル転送の信号速度(黒線)、シリアル転送の信号速度(赤線)、プロセッサの動作周波数(黒点)、メモリの信号速度(黄色)を示した。 図3 電源の低電圧化でノイズマージンが減少

図3 電源の低電圧化でノイズマージンが減少 図4 ミアンダ配線(上)と等長配線(下)

図4 ミアンダ配線(上)と等長配線(下) 図5 差動信号の利点と欠点

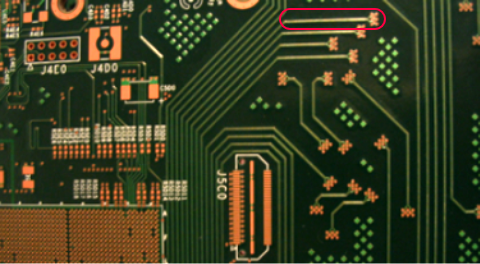

図5 差動信号の利点と欠点 図6 2対の差動信号線をごくわずかな間隔で基板上にレイアウトした(赤枠部分など)

図6 2対の差動信号線をごくわずかな間隔で基板上にレイアウトした(赤枠部分など) 図7 理想的な波形(上)と配線に流れる実際の波形(下)

図7 理想的な波形(上)と配線に流れる実際の波形(下) 図8 ドライバとレシーバの波形が一致する場合(上)と一致しない場合(下)

図8 ドライバとレシーバの波形が一致する場合(上)と一致しない場合(下) 図9 伝送線路として扱わなければならない配線を見分けるには

図9 伝送線路として扱わなければならない配線を見分けるには 図10 特性を安定させる基板の構造

図10 特性を安定させる基板の構造 図11 差動インピーダンスを考慮した基板設計

図11 差動インピーダンスを考慮した基板設計