基板設計がうまくいかない、反射や損失を回避する手法

終端抵抗をとり付ける意味は? プロセッサなどの背面にパスコン(バイパスコネンサ)が必要な理由は? クロストークノイズを防ぐ主な手法は? いずれも高速信号を扱う際に十分理解しておかなければならない内容だ。

ピーバンドットコムが開催した「P板.com 技術セミナー」(2015年9月16日)では、前回に続き、米KEI Systemsで代表を務める前田真一氏(図1)が、これらの問いに丁寧に答えていった。

まずは反射ノイズを防ぐ

「反射ノイズを考慮しなければならない場面はこうだ。高速信号を扱う回路で配線長を短くできないとき、つまり配線を『伝送線路』として扱う場合だ。反射ノイズを防ぐにはインピーダンスをそろえて、そもそも反射を起こさないように設計すればよい。そのために終端抵抗を利用する」(前田氏)。

前回紹介した通り、データ転送信号の速度が1 [GHz]以上を超えた時点で高速信号としてのとり扱いが必要になる。正確には周波数よりも、信号の立ち上がり(立ち下がり)時間(dv/dt)と配線長の関係が重要だ。例えば立ち上がり、立ち下がり時間が1 [ns]なら、配線長が2.5 [cm]以上のときに伝送線路としての扱いが必要になる。

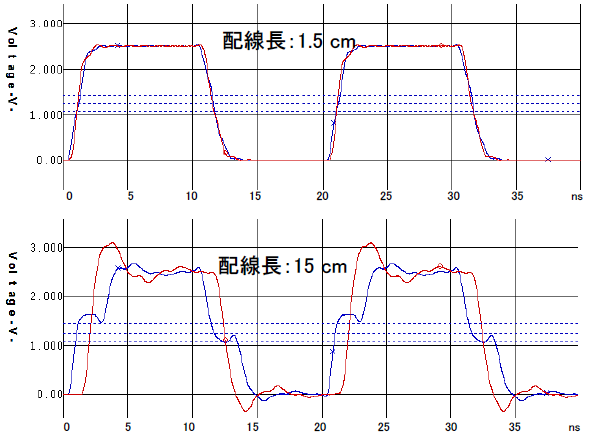

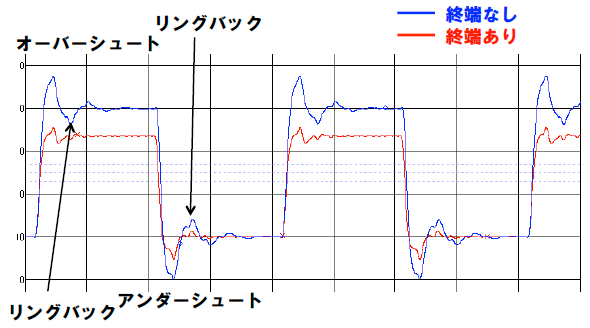

実際に、周波数が50 [MHz]と低くても、配線長が15 [cm]あると、図2下のように信号を送り出すドライバ(青色)と受け取るレシーバ(赤色)の電圧にオーバーシュートやアンダーシュート、リンギングが現れてくる。本来はどちらもほぼ台形の信号になるはずだが、反射が起こって信号がゆがんでいる。これが伝送線路の特徴の1つだ。

インピーダンスの変化が反射を生む

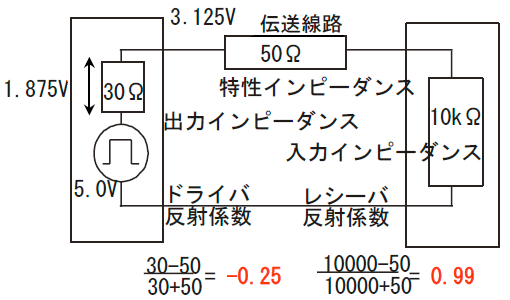

伝送線路では、インピーダンスが変化する場所で信号が反射する。ドライバ側の出力インピーダンス(Zo)と、伝送線路の特性インピーダンス(Z)、レシーバ側の入力インピーダンス(Zi)が分かれば、反射ノイズの計算はさほど難しくない。ドライバ側の反射係数は、(Zo−Z)/(Zo+Z)、レシーバ側は(Zi−Z)/(Zi+Z)と表すことができる。

図3の回路では出力インピーダンスが30 [Ω]、特性インピーダンスが50 [Ω]、入力インピーダンスが10k [Ω]*1)、信号電圧が5 [V]なので、ドライバ側の反射係数は−0.25、レシーバ側は0.99と計算できる。

*1) ドライバから伝送線路を見たとき、√(L/C)が負荷(50 [Ω])になる。CMOS ICの入力インピーダンスは一般に数k [Ω]程度と高い。

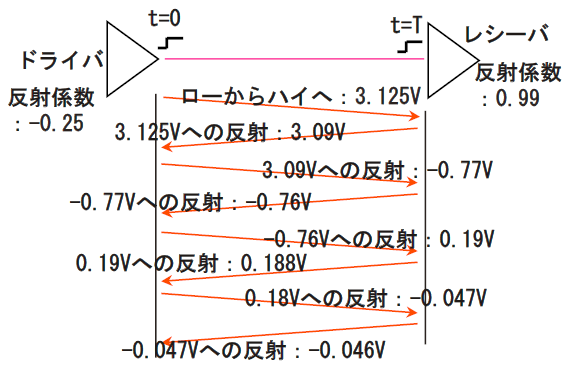

図3の回路で信号がどのように反射するのかを示したのが、図4だ。5 [V]の信号を1回だけ出力したとしよう。30 [Ω]と50 [Ω]の分圧によって、ドライバからの出力電圧は3.125 [V]に下がり、レシーバに到達する。レシーバでは反射係数0.99を乗じた3.09 [V]が跳ね返る。ドライバに戻ってきた3.09 [V]が−0.25倍されて、−0.77 [V]がレシーバに向かう。このような動作が定常状態になるまで続く。

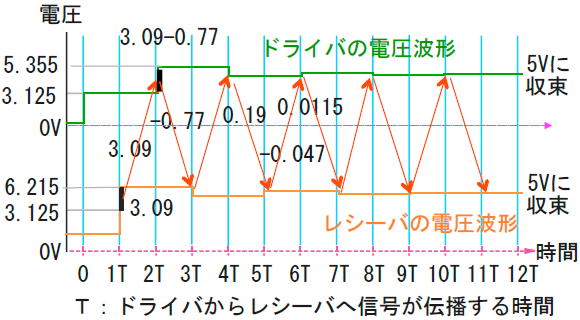

同じ内容を時間と電圧を軸にとって描くと図5になる。図2とは電圧やタイミングが異なるものの、手計算でも大まかな傾向を再現できている。

インピーダンスを合わせる終端抵抗

このような反射ノイズを減らすには、出力インピーダンスか入力インピーダンスのどちらかを特性インピーダンスと同じにすればよい。反射係数の式からもそのことが理解できる。具体的には終端抵抗をとり付けることで対応でき、オーバーシュートやリンギングを効果的に抑えることができる(図6)。

ただし、図6には終端抵抗の欠点も現れている。信号振幅が減ってしまう。前回紹介したノイズマージンが減るということだ。「ある程度反射を抑えつつ、閾値、ノイズマージンを確保するためには、50 [Ω]の終端ではなく70 [Ω]ぐらいの高めの終端抵抗を入れるとよい場合がある。反射と電圧レベルの低下を調整しながら終端抵抗の値を決めなければならない。例えばDDRメモリは出力インピーダンスが高いため、終端抵抗に50 [Ω]を入れると下がりすぎてしまう」(同氏)*2)。

*2) 前田氏は米Intelが開発したメモリインタフェースである「Rambus」をとりあげてインピーダンスの考え方の難しさを紹介した。「Rambusではドライバの出力インピーダンスを35 [Ω]にすることに決めていた。35 [Ω]を実現しようとすると、基板上の配線が太くなってピン間移行ができない。回路設計の考え方だけで規格化しており、実装をあまり考慮していなかったといえる」。Rambusがあまり普及しなかった理由の1つだ。

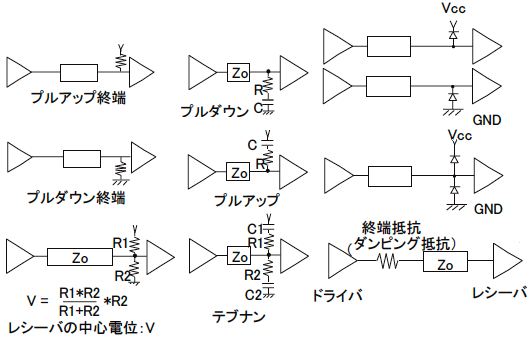

終端抵抗を利用するとき、考えなければならないことは大きく2つある。種類と挿入位置だ。

図6で利用した終端抵抗は「プルダウン」と呼ばれるもの(図7)。入力側の直前でグラウンドと抵抗で接続している。回路を流れる信号がふだんローであれば、プルダウンが適する。これは消費電力を考えた結論だ。プルダウンでは信号がハイのときに電流がグラウンドに流れ込み、消費電力増につながる。

従って、回路を流れる信号がふだんハイであれば、プルアップを使うべきだ。ハイとローの比率がほぼ同じであれば、図7左下のような構成を使ってもよい。無駄になる電力はプルアップやプルダウンを採用した場合と同じだ。

プルアップやプルダウンで無駄な電流を避けるため、図右下のように終端抵抗と直列にコンデンサを入れる手法もある。ただし、高速信号では信号の立ち上がり、立ち下がりが遅くなるため、利用されていない。低速信号用の手法だ。

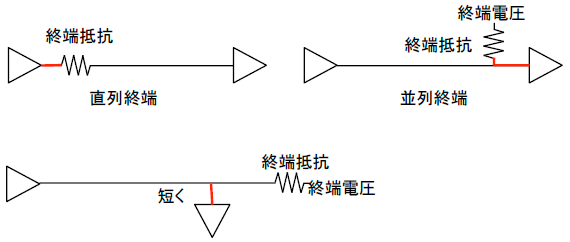

終端抵抗を挿入する位置は複数ある。代表的なのが、ドライバの直近とレシーバの直近だ(図8)。ドライバやレシーバと終端抵抗を1つの素子として扱うことが可能な距離に入れなければならない。ドライバやレシーバから終端抵抗までの距離(図8の赤線)をスタブ長と呼ぶ。

「スタブ長が集中定数として成り立つ短さに抑える必要がある。信号の立ち上がり、立ち下がり時間が100 [ps]であれば1.5 [mm]以内に入れなければならない」(同氏)。

終端抵抗を入れにくい素子もある。例えばBGAやFPGAのように端子が多い素子だ。パッケージから配線を引き出すだけで、数 [mm]必要な場合もある。線長がかさんでいるため、出力側には挿入しにくいだろう。そのような場合は図8(下)のように短い分岐を入力側に入れる。

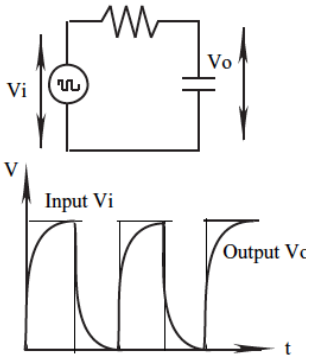

終端抵抗をうまく挿入できない場合、積分回路を利用することもできる(図9)。信号の立ち上がり立ち下がりを滑らかにする効果があるからだ。

ただし、終端抵抗と比べて使い方が難しい。立ち上がり立ち下がりが遅くなるものの、遅くしすぎるとそもそも立ち上がりなどが起きなくなるからだ。「積分回路中のCとRの積で決まる『時定数』を計算して、微調整する必要がある。CMOS ISではCが2〜5 [pF]であるため、Rの値を調整して立ち上がりと立ち下がりのエッジを小さくしながら、タイミングを調整する」(同氏)。

クロストークノイズを生む2つの要因

反射ノイズ以上にやっかいなのが「クロストークノイズ」だ。なぜやっかいか。3種類のノイズがあり、こちらを立てればあちらが立たずという関係にあるからだ。

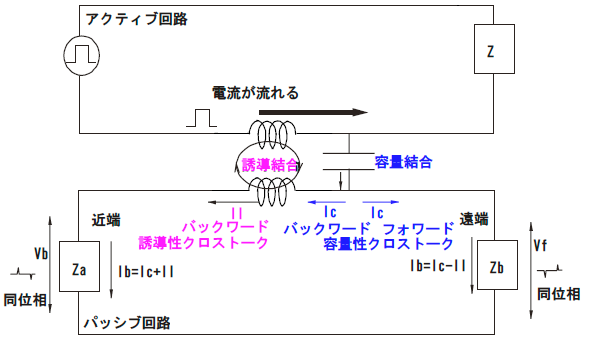

クロストークノイズを引き起こす原因は2つ。1つは近接した配線間の誘導結合が引き起こす電流だ。トランスと同じ仕組みで生じる電流である。もう1つは配線同士などの静電結合が作り出す電流。ある配線と別の配線やプレーン層が勝手にコンデンサを形成し、信号が通った直後に電圧を誘導する。この電圧が電流を生み出す。

この2つの原因によって3種類の電流ノイズが生まれる(図10)。

図上のアクティブ回路に電流を流すと、パッシブ回路(ビクティムとも呼ぶ)に誘導結合(ピンク色)と静電結合(青色)が生じる。誘導結合はアクティブ回路と逆向きの電流(バックワード誘導性クロストーク)を生む。容量結合はアクティブ回路と逆向きの電流(バックワード容量性クロストーク)と、同じ向きの電流(フォワードクロストーク)を流す。

3種類のノイズを合成した結果はどうなるか

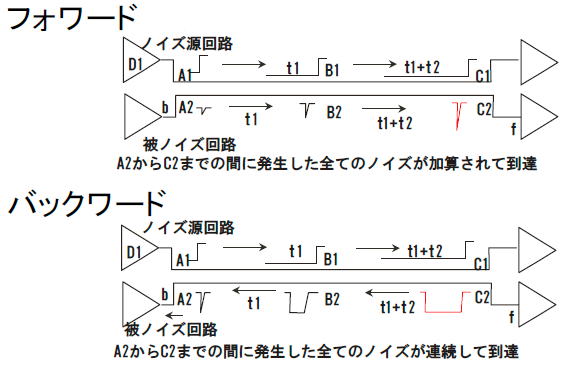

3種類の電流ノイズは1回だけ発生するのではない。配線が並行である限り、信号の伝播に従って、ドライバからレシーバ方向に移動しつつ、連続的に発生する(図11)。

3種類の電流ノイズを足し合わせると、特徴的な波形が現れる。並行配線長のあらゆる地点で発生したフォワードクロストークノイズは信号と同時に届く。レシーバ側のノイズは瞬間的で大きい(図11右上)。

ドライバには2種類のバックワードクロストークが戻ってくる。レシーバへ信号が進んでいくと最初のノイズ発生地点の後ろに次々とノイズがつながっていくため、ドライバに戻ってくるノイズにはピークがなく平らだ(図11右下)。ノイズの発生幅は、信号がドライバを出てからレシーバに到達する時間の2倍になる。

このバックワードクロストークノイズはアクティブ回路側にさらにバックワードクロストークノイズを生み出す。ドライバに現れるフォワードクロストークノイズが落ち着いた直後、しばらくほぼ一定の電位を保つのはこのためだ。

クロストークノイズを低減する3つの手法

以上の挙動から、クロストークノイズの大きさについて、3つのことが分かる。第1に、並行線長が長いほど、クロストークノイズは大きくなる。第2に配線幅が太いと、容量性クロストークノイズが大きくなる。細いと、誘導性クロストークノイズが大きくなる。

第3に信号の変化率(dv/dt)が大きいと、誘導性クロストークノイズが大きくなる。「低電圧化がクロストークノイズの低減に役立つのはこのためだ。ここでは先ほどの積分回路をつかって信号を鈍らせる手法も利用できる」(同氏)。

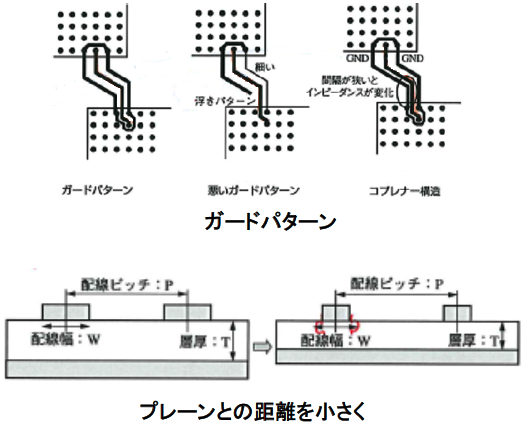

クロストークノイズを低減するには、これら3つの挙動を利用すればよい。まずは配線間隔を広げ、並行配線となっている部分の長さを短くする。

配線間の結合を少なくする工夫も効く。プレーンとの結合を強くすればクロストークノイズが減る(図12下)。この他、配線の周囲にガードパターンを配置する手法もある(図12上)。「細いガートパターン、浮いたガードパターンは付けない方がましだ。近くの配線と結合してガードパターン自体の電位が揺れてしまう」(同氏)。

パラレルバス配線で起こるクロストーク

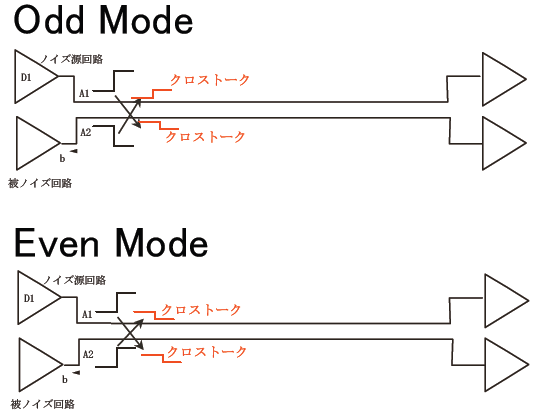

メモリバスのように、複数の配線へ同じタイミングで信号を出力する回路がある。このような回路では、さらに複雑な挙動を考慮しなければならない。odd modeとeven modeだ。「前回、パラレルバス配線が難しい理由を解説した。odd mode、even modeは、パラレルバス配線が難しいもう1つの理由である」(前田氏)。

odd modeとは、隣接する配線に対してドライバが逆位相の信号(ハイとロー)を出力した場合に起こる。誘導性クロストークのみが現れ、クロストークは隣の信号と同相になる。立ち上がり立ち下がりが早いまま、信号伝播をお互いに加速する(図A-1)。

隣接する配線に対して同位相の信号を出力した場合がやっかいだ。even modeと呼ぶ。クロストークは隣の信号と逆相になるため、互いに信号伝播を遅らせるように働く。立ち上がり立ち下がりが遅くなり、信号も鈍ってくる。

「odd modeとeven modeがどのような頻度や順番で起こるのかは予測ができない。前回解説したパラレルバス転送では同期をとるために配線長をそろえている。ところがodd modeとeven modeの問題があるため、配線長を全く同一にしても遅延が起こり、タイミングの許容誤差が小さくなってしまう」(同氏)。

損失は周波数と配線長さに比例する

反射とクロストークを考慮した設計が高速信号では必要だ。設計が甘い場合、レシーバに正しい信号を届けることができない。回路設計の難しさは反射とクロストーク以外にもある。以下では高速信号特有の「損失」と「電源ノイズ」について触れる。

「信号伝送の周波数が500 [MHz]程度であれば、損失は考えなくても構わないが、1 [GHz]なら考慮が必要だ。損失は周波数に比例して増大するからだ」(同氏)。

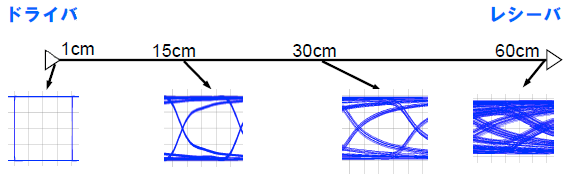

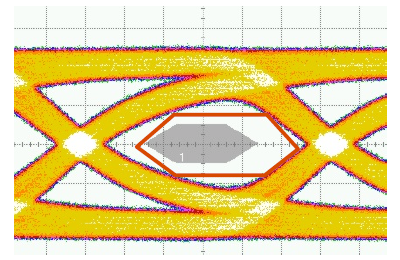

損失は配線長さにも比例する。するとどうなるか。図13のようになる。ドライバから1 [cm]の距離では波形がほとんど乱れていない。ところが、15 [cm]ではアイパターンが狭くなっている。これは信号の立ち上がり立ち下がりが遅くなっている様子を見ていることになる。

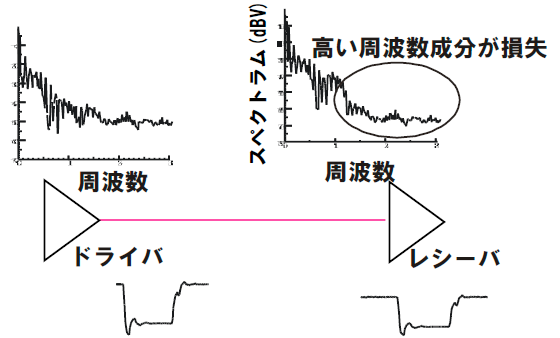

図13は信号の損失が周波数に依存するために起こる現象だ。ドライバが出力する信号とレシーバが受け取る信号を周波数軸表示で表すと、図14のようになる。レシーバ側では高い周波数成分が損失している。矩形波に近い波は高集波成分を必ず含む。高集波成分がなくなると、立ち上がり立ち下がりが必ず遅くなる。

配線が短い場合や低速信号では損失によって立ち上がり立ち下がりが遅くなる効果のみが現れ、長い配線や高速信号では、それに加えて振幅も小さくなる。

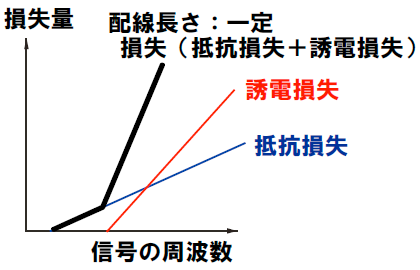

なお、損失には2つの原因があり、その合算が実際の損失になる(図15)。抵抗損失は表皮効果により生じ、誘電損失は基板のFR-4などの誘電体による。

同時スイッチングノイズはパスコンで対応

高速信号ではこれまで紹介したドライバとレシーバ間の伝送線路が原因で起こるノイズの他に、電源とグラウンドの安定性が引き起こすノイズがある。

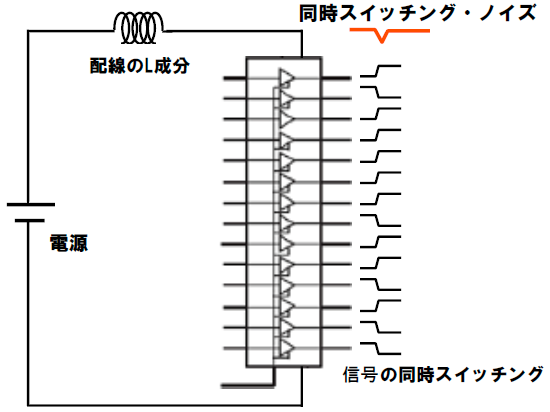

その1つが同時スイッチング(SSO)ノイズだ。CMOS回路は信号のスイッチング時にのみ電流が流れ、それ以外のときには流れない。このため、多数のドライバが同時にスイッチングするような回路では、瞬時に大電流が流れる。CPUなどが当てはまる。

基板の電源供給源からICまでの配線は、小さいながらインダクタンス(L)成分がある。このようなL成分は周波数が高くなるほど値が増える。ここで同時スイッチングが起こると、電流増加に抗って電源供給が遅れる。つまり、短時間とはいえ、ICの電源電圧が低下した状態が続く(図16)。

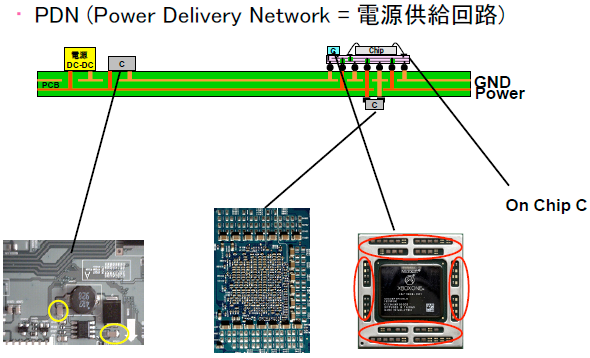

これでは回路が正常に動作しなくなる。これを防ぐ工夫の1つが電源供給回路に設けたバイパスコンデンサ(パスコン)だ。SSOによって下がった電圧をパスコンが補う。

パスコンはSSOに対抗するため、なるべくCMOS回路のそばに置かなければならない(図17)。図17中央下のようにCMOS回路のすぐ背面にびっしりと配置されたパスコンは珍しくない。配線距離を短くする工夫だ。

さらに動作周波数が上がると、基板の背面では間に合わなくなり、図17右下のようにパッケージ上にコンデンサを載せてパスコンを補う設計も現れた。基板上のパスコンが役立つのは100 [MHz]程度まで。さらに1 [GHz]程度まではパッケージ上のコンデンサが役立つ。それ以上になるとチップ内にコンデンサをレイアウトする必要が出てくる。

見落としがちな小さなLC成分とリターンパス

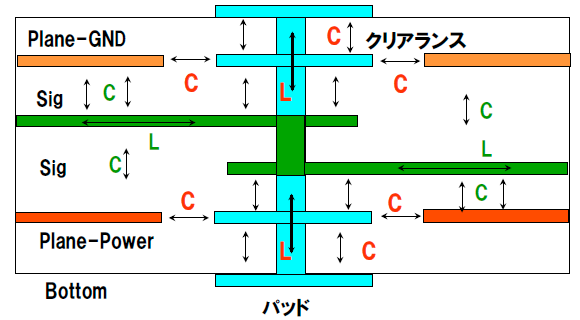

高速信号では特有の問題が幾つも現れる。基板の設計では、ビアなどが持つごく小さなL成分やC成分が問題になる。「MHzオーダーでは無視できた問題だ。特にビアが持つL成分やC成分はビアの電気的特性が予測しにくいことから設計が難しい。3次元電磁界解析ソフト(3次元フィールドソルバ)などの利用が望ましい」(同氏)。

基板で問題になるL成分とC成分を図18に示した。「図中央上にあるビアの上部と下部(水色)はL成分を持つ。オープン構造であることから信号を全反射し、信号が鈍る。オープンなビアを後からとり除くバックドリルや、非貫通ビア(IVH)といったビアの手法が対策となる」(同氏)。

基板を設計する場合に見落としがちなのは、リターンパスの確保だ。電圧源から負荷に向かった電流はかならず電圧源に戻る必要がある。高速信号では、電圧源に戻る配線(リターンパス)と信号線の間にあるC成分を電流が通過する。図18にあるCで電流が流れるということだ。「ところがグランドプレーンと電源プレーンの間は通常、つながっていないため、電流が流れない。これが悪影響を及ぼし、信号が鈍ってしまい、オンオフが認識できなくなる場合もある」(同氏)。

タイミング問題は悪化するばかり

「高速信号において悪影響を及ぼすノイズを紹介してきたが、最も厳しいのはタイミングだ。パラレルバス配線では打つ手が少ない。500 [MHz]程度では問題にならないが、5 [GHz]になると信号の1周期が200 [ps]まで短くなり、マージンがなく、データは読めなくなる」(同氏)。

タイミング誤差は頭が痛い課題だ。前田氏はこれまで紹介したものを含め、代表的なタイミング誤差を8つ挙げて見せた。

- 配線長誤差

- シグナルインテグリティ(SI)

- 符号間干渉(ISI)

- クロストーク(odd/even)

- 同時スイッチングノイズ(SSO)

- IC内部のタイミング誤差

- インターポーザ配線

- ランダムジッタ

「配線長誤差では1 [mm]で6〜7 [ps]という時間を合わせなければならない。同時に、内層配線、外層配線、ビアを区別する必要がある。外層は片面が空気に面しているが、内層は比誘電率の大きな、例えばFR-4に挟まれている。物理的な距離ではなく、電気的な距離を合わせ込む必要がある」(同氏)。

(2)は波形のゆがみの問題だ。(3)はパラレルバス配線に特有の同期ずれだ。パラレルバス配線では並列配線間のクロストークノイズと、同時スイッチングノイズ(SSO)を紹介した。符号間干渉は信号の内容に依存するノイズの一種だ。「例えば、0000000という信号が続いた後で1を出力すると、きれいに信号が出る。ところが0101010の後に1を出力しようとしても1つ前の信号のリンギングの途中だ。立ち上がり中に下がる動作になる。このため、波形が複雑に変化する」(同氏)。

(6)はICメーカーが仕様として公開しているものの、(7)は対策が遅れている。「パッケージ内基板の配線については等長配線を考慮していないメーカーが少なくない」(同氏)。(8)は量子的な効果だ。瞬間瞬間で電流の値にムラが生じていることに起因する。

シミュレーションと解析モデルを役立てる

反射、クロストーク、損失、タイミング……。これら全てを考慮して基板を設計することは容易ではない。設計時には解析ソフトウェアの力を借りる必要がある。

具体的な解析手法のうち、最も基本的なのが波形解析だ。以下では信号波形に限って解析の全体像を紹介する。

波形解析の目的は3つある。第1がトポロジーや終端、層構造の決定だ。「トポロジーではメモリ、クロックなど片側が1本、もう片側が複数箇所につながる分岐形状の解析が中心になる。終端抵抗をどこにどの程度入れるか、基板の厚みについても解析できる」(同氏)。

第2がDCスペック。電圧関連のシミュレーションだ。許容誤差内にオーバーシュートを収める際に役立つ。

第3がACスペック。タイミングのシミュレーションを実行する。「いずれの目的でも、変数をさまざまに変えて最適設計を探すために役立つ」(同氏)。

このような目的をかなえるにはトランジェント波形解析が役立つ。特定ビットパターンやクロック波形をチェックでき、終端やパッケージ特性、ビアの影響など細かい波形ゆがみや原因を詳細に確認できるからだ。

アイパターンが役立つとき

波形解析には2つの手法がある。1つが時間軸の波形解析。電圧と時間を各軸にとったV-T表示波形だ。「この終端抵抗を入れると、波形がこのように変化するといったWhat-if解析を進める際には波形解析が役立つ」(同氏)。

だが、メモリや高速シリアル配線の解析ではアイパターンが必要不可欠だ(図19)。いろいろな条件の信号の組み合わせを1つにまとめて表示し、タイミングや信号の振幅が確保できているかどうか、合否判定する場合に用いる。

図19のように測定データが例えばUSBやPCI Expressの規格で決められた範囲を含んでいれば合格だ。「波形解析では、1つ1つの波形パターンがいろいろなビットパターン、例えばクロストークノイズやISIなどによって変化してしまう。これらを全部見て合否判定することは難しい」(同氏)。

シミュレーションの用途は1つではない

シミュレーションを実行する場合、3種類の解析手法を区別しておかなければならない。ワーストケース解析とティピカル解析、全ケース解析だ。

「シミュレーションでは全ケース解析以外の2つを進める。ワーストケース解析は動作保証を目的とした解析だ。多くの解析パラメータがあるため、実行が難しい。どのようなパラメータの組み合わせがワーストケースなのかを事前に調査した後に実行する」(同氏)。

ティピカル解析は設計の早い段階である程度の目安を付けるために実行するシミュレーション。「80%程度の場合、現在の設計が動作することを確認するために実行する。平均的に特性がよいパラメータの組み合わせも把握できる」(同氏)。全ケース解析は高速なシミュレータを利用している場合に限って利用可能だ。

どの解析モデルを使うか

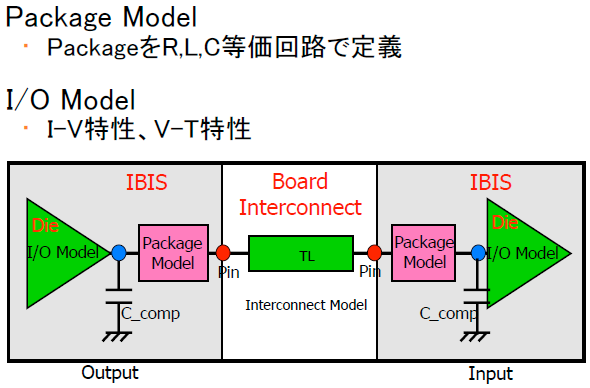

技術セミナーの最後のテーマは「解析モデル」だ。解析モデルには幾つかの分類があるという。解析対象に基づくと、ドライバ・レシーバ間を解析するI/Oモデル、パッケージ中やインターポーザを解析するPackageモデル、基板を解析するInterconnectモデルに分かれる。

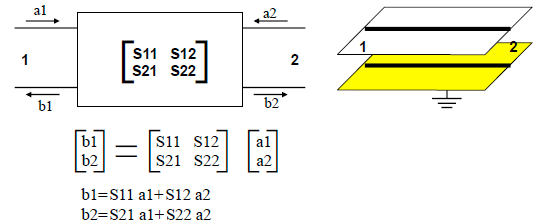

解析アルゴリズムで分類すると、主なものは古典的なSPICEモデル、パッケージやインターコネクタの解析に役立つSパラメータ、現在主流となっているIBISモデル、高速シリアル配線専用のIBIS AMIモデルだという。

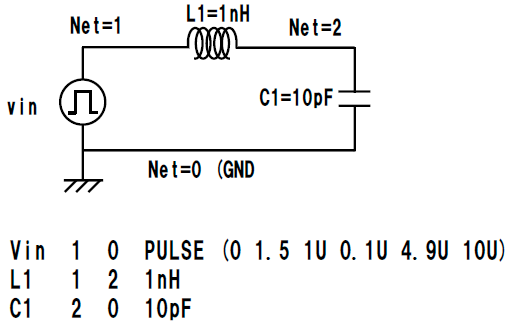

SPICEモデルはIC開発用に設計されたモデルであり、既に40年以上の歴史がある。自由に利用できるモデルであったために、ICメーカーなどが独自に機能を追加してきた。

「SPICEモデルは、ネットリストと呼ぶテキストファイル内に回路の物理レイアウトをそのまま入力する。半導体設計で使いやすいものの、IP保護の観点から社外に公開できない場合がある」(同氏)。

図20は単純な回路(上)をSPICEモデルで記述したもの(下)。下のテキストファイルでは、素子の名称(L1など)、接続関係(1 2)など、特性(1nHなど)を表している。

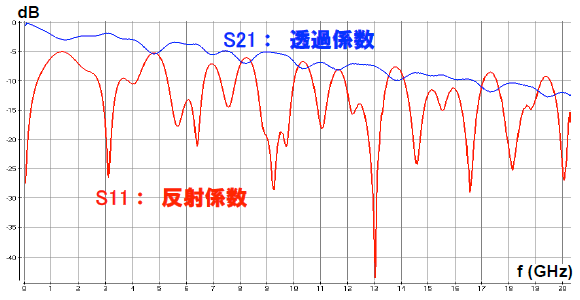

「Sパラメータは近年よく使われている。周波数依存性のあるモデルが書けるからだ。損失などを記述しやすい。基本的には入力ポートと出力ポートがあって、反射と透過による損失の特性をテーブル形式で記述したものだ。図21にある『S21』というのは2からみた1の特性、1から入れた信号が2からどのように出てくるという特性であり、これが透過係数である。逆にいえば周波数幾つでどのぐらい損失があるかを表している」(同氏)。

S11とS21の値をグラフ表示すると、図22のように周波数によって、どの程度反射や透過が起こるのか、分かりやすくなる。

IBISとIBIS AMIは全く違う

IBISはPCIバス向けのボード設計を容易にするために米Intelが開発を始めたモデルだ。SPCIEモデルの3つの「欠点」を解消した。欠点とはシミュレーションに時間がかかりすぎること、内部回路のIPの保護ができないこと、SPICEモデルに「方言」があることだ。

IBISモデルは、RCL等価回路で表現したPackageモデルと、I-V特性とV-T特性で表現したI/Oモデルを組み合わせた形をとる(図23)。

IBISモデルには精度の問題がつきまとう。精度が悪くなる原因は幾つかある。シミュレータと負荷条件の設定、高周波対応への対応が大きい。

「IBISモデルではある負荷状況を与えて、その条件での特性を求める。このため、負荷条件が実際の回路と違う場合、シミュレータ側で負荷条件を変えた場合を考えて解析する必要がある。ただし、対応が不十分なシミュレータもある」(同氏)。

IBISモデルの開発団体はバージョンごとの互換性に特に注意を払っており、上位互換性だけでなく、下位互換性も維持している。このため、IBISモデルに与えた情報のうち、実際にはシミュレータが利用していない情報がある。これが精度を悪くしている場合もある。

もう1つは高周波への対応だ。「PackageモデルはL、C、Rを1段、集中定数として見ているため、周波数がGHzまで高まってくると、例えば5 [mm]の配線でも伝送線路として扱わなければならなくなる。実際には2〜3 [cm]のインターポーザ配線もあり、これを集中定数として見ることはできない。このため、最新のIBIS 6.0からはSパラメータを利用できるように改善された。高周波にも対応できる」(同氏)。

2008年にはシリアルリンクの解析に特化したIBIS AMIが登場した。「DDRメモリやパラレルバスには利用できないことに注意が必要だ」(同氏)。

IBIS AMIは配線長さや周波数に比例して大きくなる損失を解析するために生まれたモデルだ。「高速なシリアルリンクでは、ドライバとレシーバにアナログのフィルタを導入している。PCI Expressでいうエンファシス、ディエンファシスを実現するためだ。条件に応じてドライバの電圧を強くしたり弱くしたりして高速に転送する。例えば、1ビット目でドライバの立ち上がり、立ち下がりを強くして、2ビット目以降に同じデータが続くときには弱くするというような調整を行う。このような挙動をIBISモデルのSパラメータで解析しようとすると、ビット列を与えてドライバとレシーバの特性を切り替えていく必要がある。非常な手間であり、時間も掛かる」(同氏)。

高速信号を扱う回路では配線が理想的な振る舞いをしないため、伝送線路として扱わなければならない。伝送線路では反射やクロストークがもたらすノイズや損失が増えることはもちろん、タイミングマージンが非常に小さくなってしまうことが課題だ。

単に動作するだけでなく、論理に基づきワーストケースを考慮した設計が欠かせない。これが技術セミナーを通じた前田氏の主張だ。

部品実装サービス大幅値下キャンペーン

対象はリフロー実装案件

これまで手付け実装でご利用いただいていたお客様も、実装仕上がり品質のよいリフロー実装をお試しください。キャンペーンの詳細と価格例は、こちらをご覧ください。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:株式会社ピーバンドットコム

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年12月3日

図1 米KEI Systemsの前田真一氏

図1 米KEI Systemsの前田真一氏 図2 反射によって波形が乱れた

図2 反射によって波形が乱れた 図3 反射係数の計算

図3 反射係数の計算 図4 ドライバとレシーバの間を反射する電圧

図4 ドライバとレシーバの間を反射する電圧 図5 ドライバとレシーバの電圧変化 オーバーシュートやリンギングをある程度再現している。

図5 ドライバとレシーバの電圧変化 オーバーシュートやリンギングをある程度再現している。 図6 反射ノイズを抑える終端抵抗

図6 反射ノイズを抑える終端抵抗 図7 さまざまな終端

図7 さまざまな終端 図8 終端抵抗の挿入位置

図8 終端抵抗の挿入位置 図9 積分回路の構成と効果

図9 積分回路の構成と効果 図10 クロストークノイズの全体像

図10 クロストークノイズの全体像 図11 クロストークノイズの発生場所は信号の伝播に従って移動する

図11 クロストークノイズの発生場所は信号の伝播に従って移動する 図12 クロストークノイズを抑える配線設計

図12 クロストークノイズを抑える配線設計 図A-1 odd modeとeven mode

図A-1 odd modeとeven mode 図13 信号の損失(アイパターン) 信号の周波数は1 [GHz]。

図13 信号の損失(アイパターン) 信号の周波数は1 [GHz]。 図14 高い周波数成分が失われている 図下は時間軸表示。

図14 高い周波数成分が失われている 図下は時間軸表示。 図15 信号周波数と損失の原因

図15 信号周波数と損失の原因 図16 同時スイッチングノイズが起こる理由

図16 同時スイッチングノイズが起こる理由 図17 電源供給回路とパスコンの位置

図17 電源供給回路とパスコンの位置 図18 基板に隠れたLとC

図18 基板に隠れたLとC 図19 アイパターンで示した規格の許容範囲(灰色)と測定データ(赤色)

図19 アイパターンで示した規格の許容範囲(灰色)と測定データ(赤色) 図20 単純な回路をSPCIEモデルで記述したところ

図20 単純な回路をSPCIEモデルで記述したところ 図21 Sパラメータの意味

図21 Sパラメータの意味 図22 Sパラメータと透過係数、反射係数

図22 Sパラメータと透過係数、反射係数 図23 IBISモデルの全体像

図23 IBISモデルの全体像