第4回 SimulinkモデルからHDLを生成 FPGAにDSP機能を実装する(後編):FPGA Insights

FPGAを用いてDSPベースのシステムを構築するのは容易ではない。設計、統合、検証、機能要件の変更、製造への移行時において、開発計画に予期せぬ遅れが生じることもある。現在では、製品開発サイクルを簡素化し、製品ライフサイクルの中で生じる多くの一般的なボトルネックをなくすためのFPGA開発ツールが存在する。後編では日本アルテラが提供するFPGA設計ツールを用いて、マルチチャンネル設計などの事例を紹介する。

Michael Parker 米Altera社

時分割多重化を自動設定

すべてではないが、DSPデータパスはほとんどが複数チャンネルからなる。その最も一般的な要件は、IおよびQの直交信号の並列処理である。マルチチャンネル設計にするには、単に「ChannelIn」と「ChannelOut」のブロックを設計図に追加するだけでよい。複数のチャンネル間でのDSP回路の時分割多重化は、自動的に行われるため、そのためのロジックを設計する必要はない。

設計のシミュレーションは、Simulink内で行われる。Simulink内のシミュレーションでは、Simulink ファイルを実行するたびに、Advanced Blocksetをバックグラウンドで起動する。バックグラウンドで実行される動作は以下の通りである。Advanced Blocksetは、Simulink動作モデルを与えられたパラメータとともに取得し、各FPGA用の内蔵タイミングモデルと、「Quartus II」設計ソフトウエアに内蔵されたスピードグレードを用いて、タイミングドリブンのRTL合成を行う。Advanced Blocksetは、必要に応じて、パイプラインレジスタと制御ロジックを追加することで、提示されたクロック速度を実現する。また、Advanced Blocksetライブラリからのチャンネル化ブロックを追加することにより、時分割多重化を行うようにFPGAレジスタと制御ロジックを自動的に設定する。これにより、クロック速度の速いフィルタによって、低速なデータ速度の複数のチャンネルを処理することができる。すべての場合において、Advanced Blocksetは、必要に応じて乗算器とロジックリソースを使用し、パラメータファイルに指定されたクロック速度を用いて、指定されたチャンネル数でDSP処理を実行するためのMMAC/秒を実現する。

この処理のすべてが自動的に行われ、その結果は開発ソフトウエア「Quartus」の中のタイミングアナライザ「TimeQuest」にレポートされる。多くの場合、性能レベルはFPGA乗算器のFmaxによって制限される。特にタップ数が100以上、チャンネル数が16以上のフィルタ回路では一般的だ。Advanced Blocksetを使用することにより、高性能FPGAを用いた場合は400 MHz以上、低消費電力で低コストのFPGAを用いた場合は240 MHz以上の実装を可能とする。

遅延は、本質的に決定的なものではない。しかし、Advanced Blocksetでは、要求されたクロック速度とチャンネル数を実現するために、これを調整する必要がある。ただし、設計ブロックサブセットごとに遅延を管理または制限するためのツール機能は存在する。設計の構成と性能レベルが定まれば、周辺実装のほかの部分とのインターフェースから予測される遅延の制約を加えることができる。Advanced Blocksetでは、将来的な設計変更などにも対応できる柔軟性を備えており、遅延を大きくとりたい場合には出力レジスタ段を追加することで対処することができる。

仕様変更にも柔軟に対応

上記の機能により、設計を構築した後からでも、必要に応じてチャンネルを追加したり、システムクロック速度を変更したり、他のFPGAデバイスにポーティングしたりすることが容易に行える。Advanced Blocksetは、簡単なFIRフィルタに限られるものではない。同ツールにはリファレンスデザインやIPブロックも用意されており、FIRフィルタの補間や間引き、CICフィルタ、IIRフィルタ、Radix 2 FFT、Radix 2 以外のFFT、その他多くのDSP機能の要求に対しても、迅速で高度に最適化された設計を可能とする。また、マルチチャンネルFFT、デジタルアップコンバートまたはダウンコンバートチェーン、波高率低減アルゴリズムなど、複雑なサブシステムの構築にも使用することができる。これらの機能は軍事用レーダ機器、ブロードキャスト・エッジQAM、ワイヤレス基地局、医療画像処理などの用途で用いられている。

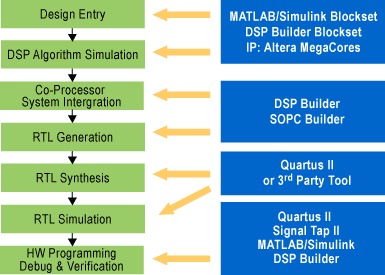

高性能なマルチャンネルのデータパスは、Advance Blocksetが設計チームに著しい生産性と柔軟性の向上をもたらすことのできる応用分野のほんの一部に過ぎない。Advanced Blocksetライブラリの中の多種多様なIPブロックを使用するか、基本ブロックを用いてアルゴリズムを構築するかを選択することができる。図1は、基本ブロックの設計フローを示したものである。

既存の設計シミュレーションにSimulinkを使用していない場合でも、Advanced Blocksetの能力は非常に高く、高度に最適化されたFPGAの論理合成技術が利用できるという利点に着目すべきであろう。Advanced Blocksetで実装したサブセクションを、大きなFPGA設計の一部として挿入することが可能であるため、顧客は、既存の設計フローを壊してしまうというリスクを最小限に抑えつつ、この設計手法の採用を試してみることができる。

Advanced Blocksetを含む設計ツールは、評価用として30日間無償で使用することができる。Advanced Blocksetに含まれる多くの設計例により、初めてSimulinkを使用するというユーザーもすぐにこの手法を取り入れることが可能だ。高性能のフィルタチェーン、FFT、その他のDSPデータパスを構築する場合は、Advanced Blocksetを利用することにより、設計時間を短縮し、最適な実装結果を得ることができる。

公開中(2009年9月〜2010年3月掲載分)

第1回 デジタル信号処理にみる DSPとFPGAの正しい選び方 (前編)

第2回 デジタル信号処理にみるDSPとFPGAの正しい選び方(後編)

第3回 SimulinkモデルからHDLを生成 FPGAにDSP機能を実装する(前編)

第4回 SimulinkモデルからHDLを生成 FPGAにDSP機能を実装する(後編)

第5回 スマートグリッドにおけるFPGAの役割(前編) 新しい「省エネルギー対応」住宅を実現する

第6回 スマートグリッドにおけるFPGAの役割(後編) 新しい「省エネルギー対応」住宅を実現する

関連情報

◎基本を学ぶ「FPGA入門」

FPGAの概要が知りたい、FPGAを試してみたい、と思っている方にFPGAの基本から設計のイロハまで分かりやすく紹介。

◎「テクニカルトレーニング」

FPGAの設計効率をもっと高めたい、最新チップの技術情報を習得したい、という方におすすめ。オンラインでの無料受講も用意。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

図 1. アルテラの DSP デザイン・フローの概要

図 1. アルテラの DSP デザイン・フローの概要