半導体IPの検証手法:コンプライアンステストだけでは不十分!(1/2 ページ)

標準規格にのっとった機能を実現する半導体IPは、当然のことながらコンプライアンステストに合格していなければならない。しかし、実際にIPの品質を完全に保証するには、それよりもはるかに困難な作業が必要となる。

IPベンダーがなすべきこと

何らかの標準規格に即した半導体IP(Intellectual Property)を開発したら、コンプライアンステストを実施することになる。それにより、そのIPが仕様どおりに機能するか否かを詳細に検査することができる。では、コンプライアンステストを実施しさえすれば、IP事業における最も重要な疑問に対する答えが得られるのだろうか。その疑問とは、「コンプライアンステストに合格すれば、そのIPが『チップ上で期待どおりに動作する』ことが保証されるのか」というものである。

筆者は、長年にわたってチップ設計者にIPを提供してきた。その経験に基づいてこの疑問に答えるなら、「そうであるとは言えない」ということになる。実際、コンプライアンステストだけでは品質や性能を保証できないことを示す理由がいくつもある。

本稿では、PCIe(Peripheral Component Interconnect Express)インターフェースを例にとり、IPが最高水準の品質を満たしていることを保証するために技術者が行うべき検証工程について説明する。その検証には、コンプライアンステストのほかに、機能的正確性の確認、さまざまなコーナーケースでのテスト、シリコンチップでの検証などが含まれる。これらすべての工程において、IPベンダーはかなり多くの作業を行うことが必要となる。

コンプライアンステストの価値

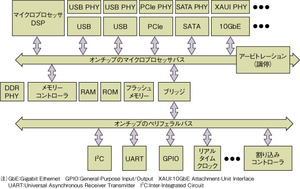

SoC(System on Chip)に実装された標準規格に基づくIPの数を考えると、仕様への準拠が必須であることがわかる(図1)。標準規格に準拠しているIPが、市場で大きな価値を持つのだ。なお、「標準」に当たるものとしては、USB(Universal Serial Bus)、PCIe、DDR(Double Data Rate)、SATA(Serial Advanced Technology Attachment)のような相互接続規格や、英ARM社などが提供しているマイクロプロセッサアーキテクチャのようないわゆるデファクトスタンダード、さらにはスタンダードセル、メモリー、I/Oなどが挙げられる。

標準規格に準拠する能力は、IP業界において基本として求められるものである。標準規格に基づくIPを利用することにより、設計者はプラグアンドプレイ手法で、より微細なプロセスノードが提供する無数のトランジスタを最大限に活用することができる。そのため、コンプライアンステストは非常に重要な役割を担うことになる。標準規格に基づくIPが、定められたとおりに機能するかどうかを検査し、ほかのデバイスとの相互運用性が確保できているか否かを確認できるからである。

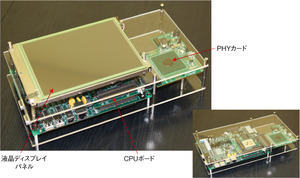

標準規格に基づくIPにコンプライアンステストのプログラムを適用するには、そのIPをシリコンチップとして実装するとともに、適切なテストシステムを用意しなければならない。そのテストシステムでは、アイダイアグラムのような電気的仕様をチェックする手段を設けるなど、各種規格に基づく一連のテストを実施できるようにする必要がある(写真1)。

コンプライアンステストの問題点

残念ながら、コンプライアンステストや相互運用性テストに合格しても、そのIPがチップ上で正しく動作することは保証できない。その理由としては、機能検証の基本的な問題や、テストでは検証できない製造上のばらつきの問題など、さまざまなものがある。例えば、コンプライアンステストでは規格が定めるすべての機能を検証することはできない。限られた動作シナリオしかチェックされず、テストにすべての条件が含まれているわけではないからだ。あるIPの実装が、コンプライアンステストや相互運用性テストに合格すれば、規格団体が定める仕様の一部に従って動作することは確認できる。しかし、例えばIPに組み込まれた構成オプションが動作するかどうかといったことは確認できないのである。

また、コンプライアンステストでは、仕様に対する余裕度を十分に把握することはできない。これは、ミックスドシグナルIP、特に今日の高速SERDES(Serializer/Deserializer)のPHY(物理)層IPでは非常に重要なポイントである。例えば、規格に対応するアイダイアグラムの範囲内にぎりぎり収まるPCIe PHYのIPは、コンプライアンステストに合格することができたとしても、仕様に対して十分なマージンがあるコアと比較して、実使用時の条件では適切に動作しない可能性が高い。

十分なマージンの確保は、パッケージやボードなどのレベルにおいて、信号品質の劣化につながるさまざまな要因に対処するために必要である。コンプライアンステストが行われる理想的な環境では、このような劣化の要因が考慮されない。また、コンプライアンステストで使用したシリコンチップは、プロセスコーナーが都合良く組み合わされたものであるかもしれない。実際のチップでは、問題が生じる恐れのあるコーナーが組み合わさっていることのほうが多いだろう。そのため、量産段階で使用できないチップが数多く製造され、歩留りが低下してしまう可能性がある。

システムへの実装時に生じる可能性のある問題に対処するには、IPに対して、コンプライアンステスト以上の詳細なチェックを行う必要がある。IPが高い品質を備えていることを保証するには、包括的なシミュレーション手法、シリコンチップによる検証などが必要である。IPベンダーは、そうした事柄のすべてを開発プロセスに組み込まなければならない。

ベストプラクティスの学習

経験豊富な設計者は、「最初から品質を確保できるように製品を設計すべきだ」と主張する。IPを開発する際には、そうした経験豊富な設計者が採用している開発手法を調査してみるとよい。

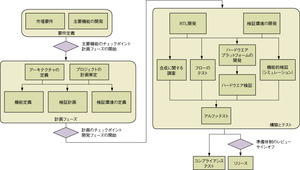

設計フローでは、その初期段階で検証計画を策定する。その検証計画をスタートとして多くの検証工程をこなすことになる(図2)。検証工程は、別個に存在するサブフローではなく、すべての工程でIPの設計に影響を与える。すなわち、フローにおける非常に重要な部分であるということだ。

設計フローで利用する実践的手法(practice)も非常に重要であり、再利用性の高い設計を実現するためのベストプラクティスを用意しておく必要がある。参考文献*1)は、大手半導体関連ベンダーや大学から得た包括的な知識に基づくSoC設計のベストプラクティスについて詳説している。この書籍では、IPが期待どおりに動作する確率を上げるために、記載されているベストプラクティスを導入することをIP開発者に推奨している。

脚注

※1…Keating, Michael, and Pierre Bricaud, Reuse Methodology Manual for System-on-a-Chip Designs, Third Edition, Kluwer Academic Publishers, 2002

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング