アナログIC設計ツール最前線(2/3 ページ)

最新の設計フロー

主要EDA企業の最終的な目標は、デジタル設計フローにおける“プッシュボタン方式”と呼ばれる簡単な操作を、アナログ/ミックスドシグナル設計にも導入することである。ここでは、ミックスドシグナルICの設計に関して各EDA企業が行っている取り組みを紹介する。

■Cadence社の例

米Cadence Design Systems社の製品マーケティングディレクタであるSteven Lewis氏は、「ミックスドシグナルIC設計では、これまで、アナログ領域をデジタル領域へ、またはデジタル領域をアナログ領域へと無理やり押し込むことが行われてきた」と語る。Lewis氏は、Intel社のRattner氏による「デジタル演算によってアナログの問題を解決する」という提案に言及しつつ、「一方の領域を他方へと押し込む方法ではもはやうまくいかない」と述べた。加えて、「65nm以降の各プロセスノードにおいては、デジタルとアナログの境界があいまいになる。どこからどこまでがアナログで、どこからどこまでがデジタルなのかが明確ではない」(同氏)と指摘する。

Cadence社でカスタムIC担当グループディレクタを務めるSandy Mehndiratta氏は、「もはや、アナログとデジタルが隔絶された方法では不十分だ。トップダウン設計を可能とし、顧客が複数の手法を混在させて使用できるような方法を採用しなければならない」と語る。Lewis氏は、「複数の拠点に分散し、多種多様なスキルを持つ設計チームをサポートできるものでなければ、有効な設計環境だとは言えない」と付け加える。

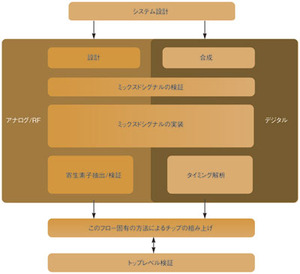

Lewis氏は、「当社の手法は、アナログでもデジタルでも、技術者が最適だと考える領域で作業できる環境を提供しようというものだ」と述べる。それを目標として、Cadence社はアナログとデジタルの「実装」の境界に加え、アナログとデジタルの「検証」の境界をなくそうとしている(図2)。

Cadence社は、デジタル/アナログの各領域において、何らかの変換を行うことなく、もう一方の領域を把握できるようにするために、例えば実装段階では、ミックスドシグナルICに対応した設計環境「Cadence Virtuoso」と微細プロセス向けのデジタルIC設計環境「Cadence Encounter」を米Si2(Silicon Integration Initiative)のIC設計用データベース管理システム「OpenAccess」の下に統合している。Lewis氏によると、「これはミックスドシグナルICの設計フローにおいて効率化を図る上で必須のことだ。しかし、これだけでは十分ではない」という。

VirtuosoとEncounterを統合することにより、アナログ部に関する作業時にデジタル部に対する接続を維持することができ、またデジタル部のフロアプランの調整時にアナログ部の固定が行える。なお、両者を統合した環境において、Encounterは、Pcell(Parameterized Cell)、マルチパートパス、ガードリングに関する機能をサポートする。Lewis氏によると、ある顧客からは「この設計環境により、ミックスドシグナル設計のサイクル時間がトータルで25%短縮された」との報告を得たという。

■Magma社の例

Magma社は、2008年2月に米Sabio Labs社を買収したことで獲得した技術をベースとした手法をとっている。Magma社のHershenson氏(Sabio社の前CEO)によると、その技術は、Magma社のミックスドシグナル対応フィニッシングツール「Titan Chip Finishing」およびアナログマイグレーションツール「Titan Analog Migration」によるミックスドシグナル設計とアナログ設計を加速するという。Titanは、統一されたデータベースアーキテクチャを採用しており、高速なシェープベース(shape-based)のルーティングとフルレイアウトエディティングをサポートする。また、Magma社のデジタル設計ツール「Talus」と、検証ツールである「Quartz DRC」、「Quartz LVS」を完全に統合している。TitanではPcellのインスタンス化も可能である。

Magma社は、Titan Analog Migrationに、マルチCPUのSPICEシミュレーションをサポートする同社の「FineSim」を統合する。Titan Analog Migrationにより、「あるプロセスノードを対象としたアナログ回路の設計を別のプロセスノード向けにわずか数時間で移行することができる」とHershenson氏は述べる。また、同氏はTitan Chip Finishingの速度について、「42Gバイトのファイルを4分で開くことができ、1チップのレイアウトを8秒で再描画できる」と述べた。

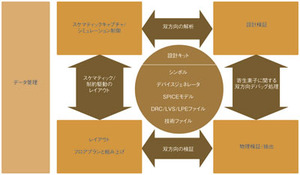

図3 Mentor社の設計フローの概念図 Mentor社のデータ管理ツールDesign Managerは、複数の拠点に分散するユーザー間での共同作業を可能にする。同ツールで管理されたアナログ/ミックスドシグナル設計フローでの作業は、双方向で行える。このフロー内において、Design Architect ICは、スケマティックキャプチャとシミュレーション制御の役割を担う。IC StationとICassembleは、レイアウト、フロアプランニング、組み上げに用いられる。Eldo、ADiTなどによって設計の検証を行い、Calibre DRC/LVSとCalibre xRCによって物理検証/抽出を行う。

図3 Mentor社の設計フローの概念図 Mentor社のデータ管理ツールDesign Managerは、複数の拠点に分散するユーザー間での共同作業を可能にする。同ツールで管理されたアナログ/ミックスドシグナル設計フローでの作業は、双方向で行える。このフロー内において、Design Architect ICは、スケマティックキャプチャとシミュレーション制御の役割を担う。IC StationとICassembleは、レイアウト、フロアプランニング、組み上げに用いられる。Eldo、ADiTなどによって設計の検証を行い、Calibre DRC/LVSとCalibre xRCによって物理検証/抽出を行う。■Mentor社の例

米Mentor Graphics社のカスタムIC部門でゼネラルマネジャを務めるMin-Fang Ho氏は、「当社の手法は、設計時に用いる実装/検証ツールを、データ管理システムが管理するアナログ/ミックスドシグナル設計フローに統合するというものだ」と語る(図3)。データ管理ツール「Design Manager」により、複数の拠点に分散するユーザーが共同で作業したり、リビジョン管理したりすることができる。そのほかのコンポーネントとしては、スケマティックキャプチャ用の「Design Architect IC」、レイアウト/組み上げ用ツールである「IC Station」と「ICassemble」、シミュレータの「Eldo」と「ADiT」、物理(レイアウト)検証ツールの「Calibre」などがある。

Mentor社のアナログ/ミックスドシグナルツール担当マーケティングディレクタを務めるHenry Chang氏は、フローのシミュレーション部分を次のように詳説してくれた。「EldoはSPICEベースのシミュレータだ。RF回路用の拡張機能を追加するための『Eldo RF』というツールもある。AdiTは、精度と引き換えに処理速度を上げた高速SPICEシミュレータだ。別の当社ツール『ADVance』によってこれらのシミュレータを統合し、当社のデジタルシミュレータ『ModelSim』と組み合わせることで、完全なミックスドシグナル設計/検証が行える」と同氏は述べる。

■austriamicrosystems社の例

IDM(垂直統合型デバイスメーカー)やファウンドリも、ミックスドシグナル用EDAツールを提供している。例えば、オーストリアのaustriamicrosystems社が提供しているものに、「HIT-Kit(High Performance Interface Toolkit)」がある。これは、Cadence社、Mentor社、Synopsys社の設計環境において、動作シミュレーション、デジタル回路の合成、スケマティックキャプチャ、ミックスドシグナルシミュレーション、レイアウト、検証、バックアノテーションをサポートするソフトウエアプログラムやライブラリで構成されたユーティリティである。

austriamicrosystems社のフルサービスファウンドリビジネス部門でゼネラルマネジャを務めるThomas Riener氏によると、「同キットにより、当社の設計者やファウンドリの顧客に対し、統一されたユーザーインターフェースを提供できる」という。また、同部門の設計サポート担当マネジャであるThomas Morth氏は、「同キットにより、例えばシングルダイ上で3.3V、20V、50V、120Vで動作するトランジスタに対し、各トランジスタが安全な動作範囲内で動作するか否かを検証する機能など、カスタム機能を追加できる」と述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー