組み込みシステムに適したPCIeのクロック分配技術(1/2 ページ)

高速入出力インターフェース技術であるPCI Express(PCIe)は、組み込み機器でも利用が進んでいる。組み込み機器において、PCIeによるギガビット/秒レベルの高速伝送を支える重要な要素が、クロックをいかに分配するかということである。本稿では、ジッターが小さく、不要輻射の少ないクロック分配技術について解説する。

PCIe規格のクロック分配方式

PCI Express(PCIe)の規格は、当初はパソコンシステムでの利用を前提として策定された。PCIeインターフェースはコネクタの端子数が少ない、性能が高い、伝送スループットを拡大できるといった特徴によって、パソコン以外のシステムにも普及した。ただし分配すべきクロックが高速であることと、クロック周波数が2種類存在することは、組み込み機器への応用では問題となる。

PCIeのプロトコルは、バックプレーンを介したデータ通信に適している。しかし、組み込み機器にとっては、バックプレーンのコネクタ端子はコストが高すぎることが少なくない。また、PCIeの技術仕様では、ポイントツーポイント接続でスター型のクロック分配方法を推奨しているが、この方法は組み込み機器において現実的な選択肢ではない。そこで、本稿では、マルチドロップ方式でPCIeのクロックを分配し、しかもPCIe Gen2規格のジッター要求仕様を満足する技術を紹介する。

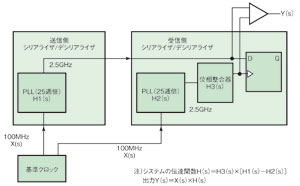

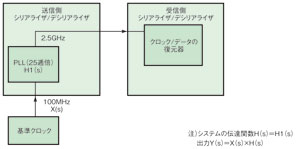

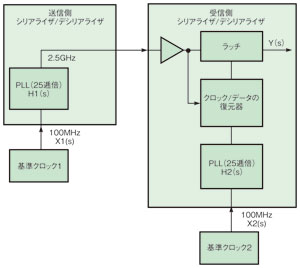

まずは、PCIe規格の概要やそこで規定されているクロック分配方式について説明しておく。PCIeの規格仕様であるPCIe Base Specifications 1.1と同2.0では、伝送速度が2.5ギガビット/秒(Gbps)、5Gbpsの信号伝送に対して3種類のクロック分配方式を定義している。コモンクロック方式(図1)、データクロック方式(エンベデッドクロック方式)(図2)、セパレートクロック方式(図3)の3つである。

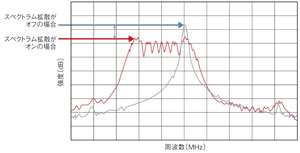

これらの中で最も一般的なのは、コモンクロック方式だ。その理由はいくつかある。まず、市販の半導体製品のほとんどが、コモンクロックのみをサポートしていること。また、その概念の理解が容易で、設計が簡素であること。そして、スペクトラム拡散クロックを直接サポートする方式はコモンクロックだけであることだ。スペクトラム拡散クロックには、不要輻射(EMI)のピーク強度を低減する効果がある。EMI規制の許容値を満足させる上では、スペクトラム拡散クロックの導入が重要な選択肢となる(図4)。

ただし、コモンクロック方式には問題点もある。最大の短所は、クロックの分配が容易ではないことだ。コモンクロック方式では、PCIeの各エンドポイントのすべてにクロック信号を分配しなければならないのである。

PCIeでは、周波数が100MHzまたは125MHzのクロック信号が用いられるが、規格が求めているジッターの条件を満たすのは容易ではない。2.5Gbpsの伝送モードで許容されるジッターは、ピークツーピークで86psである。そして5Gbpsの伝送モードでは、許容されるジッターはRMS値で3.1psとなる。なお、5Gbpsのモードでは、2.5Gbpsのモードで送受信間のネゴシエーションを完了してから、5Gbpsへと伝送速度を上げる。このため、5Gbpsの伝送モードでは、2.5Gbpsでのジッター条件も満たす必要がある。

データクロック方式とセパレートクロック方式には、このような条件は存在しない。ただし、クロック分配システムの設計は複雑である。また、スペクトラム拡散クロックを導入するには、側波帯伝送を使用しなければならない。

繰り返しになるが、基準クロックのジッター条件を記述した一般的な規格は、PCIe Base Specifications 1.1と同2.0である。また、PCIe Jitter-Modeling Revision 1.0DおよびPCIe Jitter and BER(Bit Error Rate) Revision 1.0は、ジッター条件を満足しているかどうかを検証する手法を詳しく定めている。

物理的なフォームファクタや電気信号、機能を定義している規格がPCIe Card Electromechanical Specifications 1.1と同2.0である。同規格は送信側PLLと受信側PLL、基準クロックのジッター条件も定めている。厳密には、パソコンやサーバー機器、ATXボードなどに適用されるものであり、モバイルコンピューティング向けには、PCIe Mini Card Electromechanical Specification 1.2が策定されている。

組み込み機器の性質

上記に挙げた各種の規格は、PCIeを利用する際、クロック周りの設計を行う上でのガイドラインとなる。例えば「Card Electromechanical」と名が付く規格の多くは、クロックの電気仕様にHCSL(Host Clock Signal Level)を使うと規定している。これに対して、組み込み機器の多くは、クロックにLVPECL(Low Voltage Positive Emitter Coupled Logic)またはM-LVDS(Multipoint Low Voltage Differential Signaling)を使う。クロックの伝送距離を長くとりつつ、雑音余裕を確保するためである。

組み込み機器の多くは、クロック信号を含む何種類もの高速信号をバックプレーンを介して分配する。それによりバックプレーンの電気的負荷が重くなるので、強力なドライバを積むことが少なくない。信号波形の立ち上がり時間と降下時間を短く抑えるためである。設計では最悪の場合を考慮してドライバを搭載するのだが、実際のバックプレーンの負荷が軽いときには、クロストークなどのシグナルインテグリティ(信号品質)に関連する問題が生じかねない。

また、先述したように、PCIeでは100MHzまたは125MHzのクロックを分配しなければならない。バックプレーンの負荷が重くて伝送距離が長い場合には、こうしたクロックをきれいに分配することが困難になる。そしてバックプレーンのコネクタを通る信号の数と、バックプレーンを通過する信号の数も設計を難しくする。コネクタ端子の割り付けは、非常に重要な作業となる。

組み込みに適したクロック分配

コモンクロック方式による分配では、ポイントツーポイントの差動伝送対を採用することが多い。ポイントツーポイントの一方は、PCIeのエンドポイントである。1枚のボード(あるいはカード)に複数のエンドポイントが存在する場合は、バックプレーンから送信された基準クロックを使い、ゼロ遅延バッファによってクロックを分配する。ただし、5Gbpsの伝送速度では、この方法でもジッターの要件を満たすことはかなり難しい。

オンボードでクロックを分配できたとしても、PCIeのルート(ホストあるいはマスター)からすべてのボードにポイントツーポイントで接続することに変わりはない。ルートのボードのスロットに数多くのコネクタ端子を配置するとともに、バックプレーンに膨大な配線をレイアウトすることになる。もちろん、ルートのボードでは、スロットの端子配置がほかのスロットとは異なる。

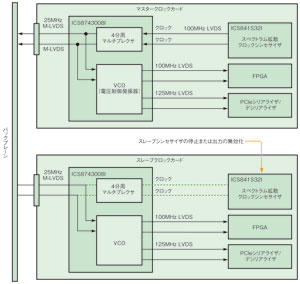

こうした複雑さを回避するために、M-LVDSを活用する方法がある。ルートのボードでPCIeのクロックを分周し、マルチドロップのM-LVDSを使って、バックプレーンを介して分周クロックを分配する。その上で、所望の周波数までクロックを逓倍するという方法である(図5)。考え方自体は簡単だが、実際には、PCIe規格のジッター条件を満足するために、かなり複雑な設計を行う必要がある。

上記の手法では、M-LVDS差動対を用いてPCIe準拠の基準クロックを送信/受信できる。組み込み機器の多くは、1枚のボード(またはカード)がルートとして動作したり、エンドポイントとして動作したりする。アプリケーションやスロット割り当てなどによって、どちらのモードで動作するのかが決まる。

ルートとエンドポイントの一方だけで動くボードであれば、図5よりも簡単な設計にすることができる。その要点を列挙すると以下のようになる。

- システムを構成するボードの中で1枚がルートとして機能する

- オンボードの水晶発振器を基に、PCIeの条件を満たす基準クロックを生成する

- 内部のクロック分配ネットワークによって、ボード上のすべてのPCIeデバイスにクロックを伝送する

- 上記のクロックは分周回路にも伝送され、元の周波数である100MHzまたは125MHzのクロックから、分周回路によって25MHzのバックプレーン周波数に変換される

- システム内のほかのすべてのボードは、バックプレーンから基準クロックを受信する

- ボード上のクロック発生器を使わず、基準クロックのドライバをトライステート状態にしておく

- 受信したクロックは、PLLベースのゼロ遅延バッファを用いて、基準クロック周波数にまで逓倍され、ほかのボードに分配される

- バックプレーンから基準クロックを受信して逓倍する回路は、通常はルートのボードに搭載する

- 上記の回路は、必要に応じて第2の基準クロックを生成する

- PCIe規格の技術仕様が要求する短いジッターを満足するには、クロックシンセサイザとゼロ遅延バッファにジッター減衰器を適用することが望ましい

この設計にはメリットがあるが、課題もある。それは、PLLはそのループ帯域幅よりも高い周波数のジッターを除去するものの、ループ帯域幅よりも低い変調周波数でジッターを加えてしまうということだ。また、PLLはトラッキングスキューを引き起こしてしまう。基準クロック入力の位相の変化と周波数の変化に、PLLは完全には追随できないからだ。このように、周波数の生成/変換のために複数のPLLが接続されたバックプレーン(PCIeの実装)においては、位相ジッターとPLLトラッキングスキューを最小化することに注力しなければならない。

Copyright © ITmedia, Inc. All Rights Reserved.