ARM社の新プロセッサコア「Cortex-A15」、処理性能は「Cortex-A9」の2倍以上

英ARM社は2010年9月、高性能機器向けプロセッサコア「Cortex-Aシリーズ」の新プロダクト「Cortex-A15 MPCore(以下、A15)」を発表した。従来、Cortex-Aシリーズが用いられてきたスマートホンや高性能のモバイル機器に加えて、車載機器やデジタル家電、サーバー機器などの用途に向ける。すでに、韓国Samsung Electronics社、スイスST-Ericsson社、米Texas Instruments社へのライセンス提供を開始しており、A15を用いたプロセッサ製品を搭載した機器は、早ければ2013年にも登場する見込み。なお、A15は、これまで「Eagle」という開発コードで呼ばれていたものである。

A15は、ARM社のプロセッサコアの特徴である消費電力の少なさを維持しながら、より高い処理性能を達成することを目指して開発された。ICとして製品化される際には、32nm/28nm以降の製造プロセスを用いることを想定している。最大動作周波数は2.5GHz。マルチコア構成で利用する場合に、SMP(対称型マルチプロセッシング)構成で利用できるコア数は最大で4個までとなっている。ARM社は、SMP構成で利用するコアの集合体を「クラスタ」と呼んでおり、同社からは、2クラスタ/8コアまでの構成を提案する予定である。ただし、「ファブリックを調整すれば、3クラスタ以上の構成も実現できるので、利用できるコア数に上限があるわけではない」(同社)ともしている。なお、A15はシングルコアで利用することも可能だ。

A15のマイクロアーキテクチャは、スーパースケーラ方式を採用しており、アウトオブオーダー実行にも対応している。また、1回のクロックサイクルにつき、3つの命令のデコードと、8つの命令の実行が可能である。キャッシュメモリーの容量は、L1キャッシュとして、命令用に32Kバイト、データ用に32Kバイトまでを利用できる。L2キャッシュについても、最大4Mバイトまでを搭載することが可能だ。さらに、128ビットまでのデータバス幅を持つ最新のオンチップバスインターフェース「AMBA 4」を採用。加えて、ハードウエアレベルでの仮想化技術にも対応した。仮想化や高度なアプリケーションのマルチタスク処理などに対応するために、最大1テラバイトまでの物理メモリー空間をサポートしている。

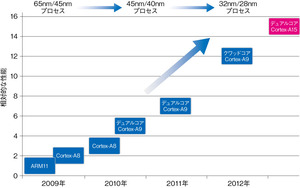

今回の発表でARM社は、A15の処理性能について、従来行ってきたDMIPS(Dhrystone MIPS)ベースの評価は行っていない。ただし、DMIPSに替えて、製造プロセスの進展と絡めた、同社の既存プロセッサコアとの比較による性能評価を行っている(図1)。それによると、32nm/28nmプロセスで製造したデュアルコア構成のA15の処理性能は、65nm/45nmプロセスで製造した「ARM11」コアの15倍、現行の最先端のモバイル機器で利用されている「Cortex-A8」の5倍、45nm/40nmプロセスで製造したデュアルコア構成の「Cortex-A9 MPCore」の2〜3倍となっている。

(朴 尚洙)

Copyright © ITmedia, Inc. All Rights Reserved.