ハーバードアーキテクチャって何?:Q&Aで学ぶマイコン講座(36)(2/3 ページ)

代表的なバスアーキテクチャ

代表的なバスアーキテクチャとして、「ノイマン型」と「ハーバード型」の2つを紹介します。

a)ノイマン型

簡単に説明すると、命令とデータ用のバスを兼用して、マイコンのハードウェアを効率的に構成するアーキテクチャです。バスは、マイコンの内部に張り巡らされているので、なるべく本数は少ない方が、マイコンのコストを抑えるのには有利です。

しかし、バスが1つしかないので、命令とデータを同時に取り扱えずに、マイコンの演算性能に影響を及ぼします。これを「ノイマンボトルネック」と呼んでおり、このボトルネックによって、高性能を追求するマイコンでは採用されていません。一方、性能よりもコストを重視するマイコンには都合が良く、コスト重視のマイコンに多く採用されています。ARM Cortex-Mプロセッサを例に挙げると、Cortex-M0とCortex-M0+がこれに該当します。低価格帯の市場をターゲットに開発されたプロセッサなのでコスト優先になっています。

b)ハーバード型

ノイマンボトルネックを解消するために、バスを命令とデータで分けて、独立させた方式がハーバード型です。この方式だとCPUが命令をフェッチしている期間でも、データバスを使って、データにアクセスできます。したがって、ノイマン型よりもマイコンの性能を高めることができます。ただし、独立した命令バスとデータバスが必要ですので、マイコンのハードウェアが大きくなり、コストが高くなります。そこで、コストよりも性能を重視するマイコンに多く採用されています。

ARM Cortex-Mプロセッサを例に取ると、Cortex-M3とCortex-M4とCortex-M7がこれに該当します。高機能アプリケーションの市場をターゲットに開発された高性能プロセッサです。

ハーバード型のメリットとデメリット

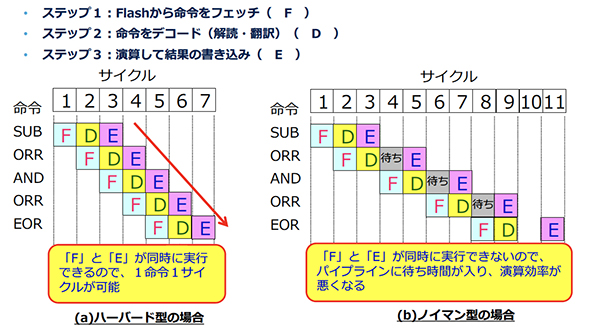

本連載の第1回「RISCとCISC、何が違う?」で説明したパイプライン処理の場合を例にとって、メリットを説明します。

図2に例としてSTマイクロエレクトロニクスの32ビットマイコン STM32F1シリーズに搭載されているARM Cortex-M3プロセッサ(以下、Cortex-M3)の3段パイプラインを示します。

「命令のフェッチ(F)」「命令のデコード(解読・翻訳)(D)」「演算して結果の書き込み(E)」の3つのステップから構成されています。各処理は1サイクル1回の処理を行います。命令をフェッチするのは「F」のステップです。データをアクセスするのは「E」のステップです。図2-aの場合、第3サイクル以降を見ていただくと、「F」と「E」が常に同時に行われています。もし、ノイマン型の場合だと、命令フェッチとデータアクセスは同時に実行できませんので、どちらかがバスの使用を待たなくてはなりません。バス権の調停をラウンドロビン方式(交互)にしたとすると、「F」と「E」が交互に行われるようになるので、図2-bのようになり、命令の実行効率が非常に悪くなります。ハーバード型であればパイプライン処理は1サイクル1命令実行が可能になります。

ハーバード型のデメリットは、バスのハードウェア規模がノイマン型の2倍必要になりマイコンのコストが上がることです。32ビットマイコンの場合、命令もデータも32ビットですので、その2倍の64ビットのバスに匹敵する面積が必要になります。バスの面積だけではありません。CPUの内部に、2種類のバスを制御する回路が必要になりますのでCPUの内部のハードウェアも大きくなります。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング