メモリーシステムの設計ポイント:プロセッサの性能はこれで決まる!(3/4 ページ)

トレードオフの考慮

メモリーとそれを管理するロジックは、プロセッサをベースとしたチップにおいてチップ面積の多くの部分を占める。つまり、メモリーブロックは面積的にコストが最も高い部品であり、しかもシステム内で最も消費電力を要する個所である場合が多い。また、多くの揮発性/不揮発性メモリーにおいて、数多くのトレードオフ項目が存在する。システム設計者は、コストと消費電力を抑えつつ、十分な性能を実現するために、主要なパラメータのバランスを考慮してそれらを取捨選択しなければならない。

メモリーアクセス遅延の隠蔽やチップコスト、消費電力などの間のバランスを保つため、プロセッサをベースとするチップでは、一般的に小容量の高速だが高価なメモリーをプロセッサコアの近くに配置する。また、大容量だが低速でより安価なメモリーをプロセッサコアから離れた位置に置く。

上記のような考えの下に一般的なメモリーシステムは、階層的なメモリー構造をとる(図2)。システム内で最も高速で容量が小さいメモリーリソースであるプロセッサのレジスタがプロセッサの最も近くに置かれる。次に、ローカルメモリーや密結合メモリー(TCM:tightly coupled memory)、複数の層からなるキャッシュ、揮発性/不揮発性のオンチップメモリー、チップ外部のメモリーなどが順に階層的に配置される。

最近のコンパイラは、プロセッサのレジスタの使用方法を管理する最適化機能を備えている。しかし、そのほかのメモリーを管理する能力はまだ不十分である。その理由は、レジスタの使用方法の最適化は、プログラムコードを局所的に参照すれば実現できるが、TCMなどほかのメモリー構造の使用方法を最適化するには、システムとプログラムコードをよりグローバルに参照する機能が必要となるからだ。そのため、ほとんどのコンパイラにおいてそのような最適化をする機能は、まだ開発の途上にある。

・TCMとキャッシュの違い

TCMなどのローカルメモリーは、ローカルバスや専用メモリーバスを介してプロセッサコアに接続され、キャッシュと同等のアクセス性能を実現する。TCMとキャッシュの主な相違点は、メモリーアクセスする際の遅延の量である。TCMを介した命令やデータへのアクセスはアクセス遅延がほぼ一意的に決まる。一方のキャッシュメモリーはというと、一時的にロックされている状態であれば、ラインレベル(一般的なキャッシュ管理はラインと呼ばれるまとまった単位で取り扱われる)でTCMのように動作することが可能である。しかし、ロックされていない場合には、ソフトウエア設計者はキャッシュミスが生じる最悪のケースを考慮しなければならない。

米Innovative Silicon社でアーキテクチャディレクタを務めるDavid Fisch氏は、「一般的な法則としては、キャッシュミスが生じると下層のメモリーにアクセスしなければならないため、アクセス遅延は10倍も長くなる。つまり、L2メモリーへのアクセスはL1キャッシュへのアクセスよりも遅延が10倍長く、L3メモリーへのアクセス遅延はさらに10倍である」と述べる。

遅延の予測が不可能なキャッシュではなく、TCMを採用したほうがよいと思うかもしれない。しかし、TCMを使用した場合、ソフトウエア開発者はプロセッサの動作に必要な命令やデータを外部メモリーからDMA(direct memory access)を用いて移動/管理して、TCMに格納しなければならない。

キャッシュは、小容量で高速なメモリーで構成され、大容量のより低速なメモリーの遅延を隠蔽する役割を果たす。時間的局所性と空間的局所性を利用することで、より低速なメモリーへのアクセス遅延を隠蔽する。

ここでいう時間的局所性とは、プロセッサがあるデータを要求したとき、その直後に再び同じデータを必要とするという性質のことである。データのコピーをキャッシュに保存しておくことにより、低速なメモリーへのアクセスを回避することができる。

空間的局所性とは、プロセッサがあるメモリー領域のコードを要求したとき、プロセッサが次に要求するのは、その次のメモリー領域や付近のメモリー領域である可能性が高いという性質のことだ。このような性質があることから、要求されたデータを取得する際、その近くのデータを同時にプリフェッチしておくことで、キャッシュ内に次のデータ領域が存在することになる。そのため、低速なメモリーから再度フェッチしてくることで生じる遅延を回避することができる。

・キャッシュの構成

キャッシュの容量が大きいほど、チップの面積コストは増大するがキャッシュミスは減少する。外部メモリーの特定の個所に格納されたデータのキャッシュ先を、キャッシュメモリー内のn個の場所から選択できる場合をnウェイのキャッシュ、または連想度(associatively)がnのキャッシュと呼ぶ。この連想度を高めると、外部メモリーのどの領域にキャッシュするかという自由度が上昇するため、大抵の場合キャッシュミスは減少する。なお、キャッシュ管理の単位であるラインの長さは、アプリケーションによって長いほうが有効な場合も短いほうが有効な場合もあり得る。

米Tensilica社でチーフアーキテクトを務めるBill Huffman氏によると、「キャッシュ構成の決定は、プロセッサで実行するアプリケーションに強く依存するため、繰り返しの作業になる」という。つまり、キャッシュ構成における種々のパラメータについてバランスをとる作業は、チップ面積とキャッシュのヒット率のトレードオフを考える複雑な作業になり得るということだ。

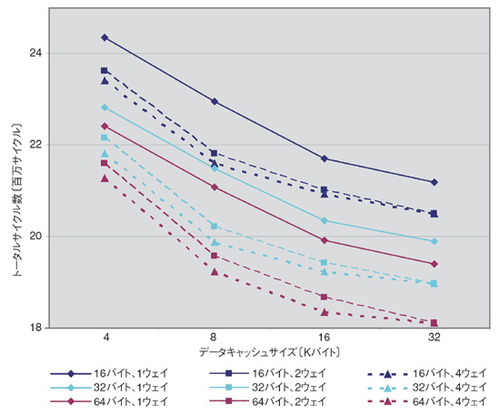

図3は、JPEGをエンコードするアプリケーションを実行した場合の例である。16バイトのダイレクトマッピング方式(連想度が1のキャッシュまたは1ウェイキャッシュ)から64バイトの4ウェイ群連想方式までの実行サイクル数を表している*2)。この図から、キャッシュサイズは大きいほどよいが、16Kバイトから32Kバイトへ増やしても、4Kバイトから8Kバイトに増やしたほどのメリットは得られていないことが分かる。また、キャッシュラインのサイズを大きくするほうが、キャッシュ全体のサイズを2倍にするよりも大きく性能が向上する。等しいキャッシュサイズの場合、長いキャッシュラインサイズのほうがチップコストを削減するメリットもあるためこのアプリケーションの場合は非常に効果的だといえる。さらに、連想度は大きいほうがよいが、この例では2ウェイから4ウェイへ連想度を変更しても1ウェイから2ウェイに変更したほどの効果は得られていない。

図3に示した結果は、JPEGエンコーディングの例だが、アプリケーションが異なれば、データサイズや処理内容も異なるため違う結果になる。つまり、キャッシュの最適な構成はアプリケーションに依存するため、決まった規則は存在しないということである。

図3 キャッシュ構成の違いによるサイクル数の違い このグラフは、JPEGエンコードアプリケーションに対して、キャッシュサイズやラインサイズ、連想度などを変えた場合における処理サイクルの違いを表している(提供:Tensilica社)。

図3 キャッシュ構成の違いによるサイクル数の違い このグラフは、JPEGエンコードアプリケーションに対して、キャッシュサイズやラインサイズ、連想度などを変えた場合における処理サイクルの違いを表している(提供:Tensilica社)。システムの設計ポイント

メモリーシステムを設計する際に最も重要なのは、プロセッサコアのアーキテクチャを考慮することである。これは、設計者が「メモリーシステムはどのようにプロセッサコアと通信するのか」という仮定を立ててコアを構築するためだ。

・プロセッサアーキテクチャ

ノイマン型とハーバード型の2つは、それぞれメモリーへのアクセス方法を異なるかたちで実装したプロセッサアーキテクチャである。

ノイマン型アーキテクチャに基づくプロセッサは、命令とデータの区別をせずに単一のストレージとしてシステムメモリーをモデル化し、単一のバスインターフェースですべての命令/データへのアクセスを処理する。一方、ハーバード型アーキテクチャに基づくプロセッサでは、システムメモリーを命令とデータに分けて異なる2つのストレージ構造としてモデル化し、それぞれ別々のバスインターフェースによってアクセスを処理する。

このアーキテクチャの違いによって、ハーバード型アーキテクチャは命令とデータへの同時アクセスをサポートするが、ノイマン型アーキテクチャはサポートしないという差が生じる。当然、このようなプロセッサアーキテクチャの違いはメモリーシステムを考える際、非常に重要な要素となる。

・アプリケーションの動作

最適なメモリーシステムを設計するには、プロセッサのアーキテクチャだけでなく、アプリケーションの動作と要件も理解しなければならない。

まず、考慮すべき点として、アプリケーションがシステム上でデータをどのように入出力するかが挙げられる。例えば、「プロセッサはデータを直接ロードするのか」、「DMAコントローラなどの外部エージェントがデータをプロセッサのローカルRAMにロードするのか」といった点である。出力に関しても、同様の問題について考察しなければならない。例えば、「プロセッサは直接、出力ポートを駆動するのか」、「DMAコントローラなどの外部エージェントがデータをプロセッサのローカルRAMからI/Oインターフェースへと転送するのか」といった点である。

ほかに、「アプリケーションは起動時にどのような動作をするのか」、「特殊なメモリーインターフェースを利用すればシステム効率が高まるか」、「オンチップメモリーに性能面でクリティカルなアプリケーションの命令やデータを格納することができるか」といったことを考察しなければならない。

アプリケーションが起動する際の挙動は、初期化コードを格納すべき場所や初期化コードにアクセスするインターフェースの選択に影響を与える。オンチップOTP(one time programmable)ROMは、ビット当たりの面積が小さいため、ブートコードを格納するのに適している。また、電源投入後にすぐに読み出せるので、アプリケーションの高速な起動が可能である。

一方、フラッシュメモリーや外部メモリーに命令/データを格納して内部メモリーにシャドーイングした場合、さまざまな遅延が発生してシステムの起動が遅くなるだろう。もし、命令/データをオンチップメモリーに格納できれば、外部メモリーインターフェースをサポートする必要はない。また、性能に影響する命令/データがプロセッサのローカルメモリーに収まるならば、キャッシュを実装する必要もないかもしれない。

設計者は、ターゲットとするアプリケーションに応じて、RAMや不揮発性メモリーをアプリケーションが要求する容量だけ持たせるようにプロセッサを設計することができる。つまり、TCMやキャッシュ、特殊なメモリーなどのサイズやパラメータは、アプリケーションに合わせて設定可能だ。だが、一般的に広範なアプリケーションをターゲットとするプロセッサにおいては、汎用のメモリーシステムを実装し、多様なアプリケーションが要求する最大公約数的な要件を満たすような設計が求められる。また、設計者はメモリーのリソースを減らしてコストを抑えるための選択肢についても考えなければならない。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 階層的なメモリーシステムの例 プロセッサコアからのメモリー階層のレベルが1つ下層になるごとに、メモリーアクセス遅延は10倍も増加する(提供:Tensilica社)。

図2 階層的なメモリーシステムの例 プロセッサコアからのメモリー階層のレベルが1つ下層になるごとに、メモリーアクセス遅延は10倍も増加する(提供:Tensilica社)。