メモリーシステムの設計ポイント:プロセッサの性能はこれで決まる!(4/4 ページ)

コントローラの設計ポイント

プロセッサアーキテクチャが類似しているシステム間の差異化をメモリーシステムによって図ることもできる。メモリーシステムはプロセッサシステムの処理性能や消費電力、価格などを決定する非常に重要な要件である(別掲記事『メモリーシステムの設計例』を参照)。中でも、メモリーコントローラをどう設計するかが大きなポイントとなる。

メモリーコントローラは、処理の対象とするメモリーブロックの実装を抽象化し、それがプロセッサシステムへのデータパイプであるかのように見せるものだ。メモリーブロックからデータを読み出すためのロジック回路が含まれ、対象とするメモリーの種類に応じて、書き込みやリフレッシュ、テスト、誤り訂正などを実行する。オンチップメモリーについては、メモリーコントローラにその企業独自の技術を搭載し、競合他社の類似のプロセッサチップとの差異化を図るといったことが行われる。

多くの場合、プロセッサベンダーは、自社の重要な技術であるメモリーコントローラの仕様の詳細は明かさない。しかし、帯域幅が広いことや多重アクセス/時間差アクセスに対応していること、パイプライン手法を取り入れていること、トランザクションの並べ替えを行うこと、特殊で斬新なアクセスパターンを採用していることなどについては多少明らかにしている。

実装されたメモリーの特性に加え、メモリーコントローラの設計と効率に影響を及ぼすシステムレベルの要因としては、「物理的アドレスをシステム内部のメモリーにどのようにマッピングするのか」、「バースト/ランダム/コンカレントなど、アクセス時のアドレッシングパターンのうちいずれを選択するのか」、「読み出し/書き込みアクセスの組み合わせにはどのようなパターンを採用するのか」、「使用しないメモリーを低消費電力モードに移行するのか」といったことがある。

通常は、主に使用するモデルに対応するかたちでメモリーシステムが決定される。例えば、グラフィックスやマルチメディア用途のメモリーコントローラは、シーケンシャルアクセスに向けて最適化され、組み込み通信システムのアプリケーション用途に向けたメモリーコントローラは、大容量のメモリーに対するランダムアクセスを重要視して最適化されるだろう。高い信頼性が要求されるシステムに向けたプロセッサのメモリーコントローラは、設計の複雑性は増すが、ECC(error checking and correction)機能を備える必要があるかもしれない。

・マルチコアプロセッサへの対応

メモリーコントローラのアクセスパターンは、シングルプロセッサコアとマルチプロセッサコアの場合で大きく異なる。シングルコア用のメモリーコントローラではストリーム的なアクセスパターンが大部分である。一方、マルチコアシステムにおける共有メモリーのコントローラは、マルチストリーム的なアクセスとランダムアクセスに対応しなければならないだろう。

マルチコアプロセッサの設計においては、高速かつ効率的にプロセッサ間でメッセージを送受でき、データの共有化が可能なメモリーシステムが要求される。

これらの目標を達成するためのものとしては種々の手法が存在するが、すべての用途に対して効率的な単一の構成は存在しない。

例えば、高速なポイントツーポイントのチャンネルやキューによるプロセッサ間通信は、短くクリティカルなメッセージを交換するのに最適である。しかし、大きなサイズのデータをやりとりするには共有メモリーのほうが適している。加えて、共有メモリーは、同期を実現し、メモリーを管理するためのプログラムをサポートすることが必要となるだろう。

ヘテロジニアスなマルチコアプロセッサなどを搭載する組み込みシステムが多くなるに連れ、ソフトウエア開発ツールはソフトウエア開発者を支援するものとしてさらに発展するだろう。これは、複雑化するソフトウエア設計において、できる限り高い処理性能を実現するために、命令/データの空間的、時間的な配置の最適化を支援するものである。このような開発ツールは、システムの全体的な動作とシステム内のメモリーシステムを適合させる作業を支援できなければならない。そのようなソフトウエア開発ツールの支援が得られなければ、ハードウエア設計者は、メモリーやメモリーコントローラの制御アルゴリズムをますます複雑化して組み込むという影の努力を続けていかなければならない。

メモリーシステムの設計例

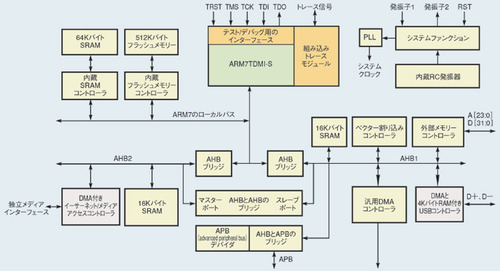

メモリーシステムの設計例として、オランダNXP Semiconductors社のプロセッサコア「NXP LPC2129」におけるプロセッサアーキテクチャを示す。これは、ARM7をベースとしたプロセッサである(図A)。ARM7は、3段のパイプラインを持つノイマン型アーキテクチャを採用しており、1つのポートがAHB(advanced high performance bus)ブリッジを介して高性能なバスに接続されている。このブリッジは、プロセッサと周辺ブロックの同期をとるインターフェースを実現し、マルチマスターバスへのインターフェースとしての役割を果たす。しかし、このブリッジはプロセッサがAHBを介したアクセスを行う際に、2クロック分の遅延を生じさせる。アドレスが連続していない場合にはさらに遅延が増加する。

命令とデータを配置する位置としては、プロセッサがメモリーにアクセスでき、周辺ブロックが直接メモリーデータにアクセスできるようするのが適切である。しかし、AHBブリッジでは、上述したように2クロック分の遅延が生じるという問題がある。処理性能を最適化するには、プログラムメモリーを、AHBブリッジのプロセッサのローカルバス側に配置するとよい。この構成ではプロセッサの処理性能は向上するが、ほかのバスマスターがこのメモリーに直接アクセスすることができなくなる。従って、DMAマスター用に、AHB側にさらにメモリーを配置しなければならない。旧式のプロセスでこの手法を用いるとコストが増加してしまうが、最新の微細プロセス技術であれば、コスト増に見合う性能の向上が得られる。

フラッシュメモリーは、6T(six transistor)のSRAMよりもかなり低速だが、不揮発性で信頼性が高く、消費電力が少ない。また、設計に柔軟性があるため、組み込みシステムで利用する価値は高い。また、1つのメモリー構造に対して多くのサブアーキテクチャがあり、それらをアプリケーションの要求に応じて調整することが可能である。ここでいうアプリケーションからの要求としては、例えば、アクセス速度や書き込み速度、電源電圧、消費電力、コストなどが挙げられる。フラッシュメモリーにおいて考慮すべきほかの重要な項目には、耐用年数や消去サイクルがある。

組み込みフラッシュメモリーにおける調整可能な点の例としては、アクセス速度が挙げられる。例えば、市販のフラッシュメモリーのランダムアクセス速度が85nsであるのに対し、組み込みフラッシュメモリーのランダムアクセス速度は約50nsと高速である。しかし、それでも100MHz以上の速度で動作するプロセッサをターゲットとする場合には問題が生じる。ただし、この問題に関しては1つの対処法がある。組み込みフラッシュメモリーへのアクセスは端子数の制約を受けないため、広いビット幅に何らかのインターフェースロジックを用いて性能を向上させることができる。

ここに示す例では、128ビットというバス幅により同時に4個のワードにアクセス可能で、シーケンシャルな連続アクセスに対しては80MHzという実効アクセス速度を実現している。これは、バッファを用いた4ワードのフェッチと分岐予測を行う読み出し操作を組み合わせることにより、フラッシュメモリーからの高い実行性能を引き出す工夫である。

この例は、データへのランダムアクセスと命令へのシーケンシャルなアクセスに対し有効である。つまり、SRAMとフラッシュメモリーを組み合わせることによって、単にSRAMを実装するよりもコストや消費電力の面で効率の良いローカルメモリーを実現できる。

広い帯域幅を備えた周辺ブロックをサポートするバスアーキテクチャの実装方法としては、2つの選択肢がある。1つは、格子状に構成されたマルチレイヤーバスを使用する方法である。これは、複数のマスターが、異なる方法でメモリーリソースにアクセスすることを可能とする。もう1つは、複数の独立したバスを実現するために、AHBからAHBへのブリッジを設計する方法が考えられる。

ローカルメモリーであるSRAMはDMAをサポートしない。従って、いずれの方法を選択した場合にも、イーサーネットやUSBなどの広い帯域幅を備えた周辺ブロックが直接メモリーにアクセスできるようにするための専用のメモリーリソースを持たせる必要がある。この専用メモリーのサイズは、格納されるデータパケットやフレーム数、データ速度、プロセッサ速度などによって決定される。

図A NXPLPC2129のブロック図 NXPLPC2129は、ローカルバスに接続されたローカルSRAMと内蔵フラッシュメモリーを備える。また、広い帯域幅を必要とする周辺回路は高速なAHBに接続されている(提供:NXPSemiconductors社)。

図A NXPLPC2129のブロック図 NXPLPC2129は、ローカルバスに接続されたローカルSRAMと内蔵フラッシュメモリーを備える。また、広い帯域幅を必要とする周辺回路は高速なAHBに接続されている(提供:NXPSemiconductors社)。Copyright © ITmedia, Inc. All Rights Reserved.