反転形DC/DCコンバーターの設計(2)部品の定格:たった2つの式で始めるDC/DCコンバーターの設計(16)(1/5 ページ)

今回は反転形コンバーターに使用する部品の定格の要点について説明、検討していきます。

前回はUSB駆動機器に代表される入力電圧の種別が限られる機器で必要な負電圧を生成する反転形コンバーターについて下記に示す概要を説明しました。

- 名前の通り入力電圧と異なる極性の出力電圧が得られます。

- 出力電圧Voはδ/(1−δ)に比例し、電圧可変範囲が0Vから可能です。

- δによる制御利得は常に1以上であり既に説明した降圧形や昇圧形コンバーターよりも高くなります。

- 時比率δを制御することで過電流保護ができます。

今回はこの反転形コンバーターに使用する部品の定格について前シリーズの降圧形や昇圧形DC/DCコンバーターにならってその要点について説明、検討していきます。

説明内容が前シリーズと重複する点も出てきますが前シリーズに戻る手間を考え、簡単に再度説明していきます。この説明が足らないと思われる箇所については前シリーズの説明を参照してください。

また、説明のための数式などは読み飛ばしてもらっても構いません。

半導体の要求定格

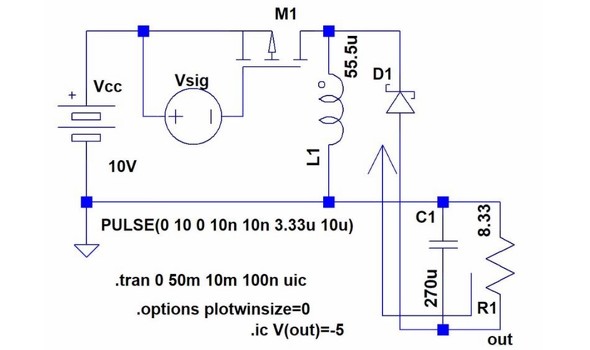

ここでは理想化された回路図ではなく、実際の回路に近い図1や図6の波形を参考にして各部品の要求特性について考えます。

FET(M1)

FETがターンオフする時には回路説明の項で述べたように次の現象が発生します。

“このようにオン時とオフ時では電流の流れの一部が切り替わります……”

一方、実機の配線(導線)には本連載の第10回で説明したように長さ1mm当たり1nH程度の寄生(浮遊)インダクタンスLeが付随して発生します。このLeは回路図には表れないのでその影響がよく見落とされるので注意が必要です。

このLeに流れる電流が上述したように急に変化するとLの式[E=L(ΔI/Δt)]に従ってスパイク電圧がLeの両端に発生します。この電圧はΔIが大きくなるほど大きくなるので同じスイッチング時間(Δt)でも大きな電流変化を伴うFET-SWやDi-SWの両端では大きなスパイク電圧が観測されます。

またFETへの印加電圧が急変すれば回路につながっている部品の寄生容量への充放電電流がCの式[I=C(ΔV/Δt)]に従ってスパイク状の電流になって流れます。特にFETには図2に示すようにターンオンピーク電流IdMが流れます。このスパイク電流は過大になると内部のボンディングワイヤにダメージを与えます。

VDSS:FETのドレイン−ソース間の最大定格電圧です。

M1がターンオフするとFETのドレイン(D)は出力電圧(ーVo)になります。したがってFETのD-S間には(VCC+Vo)の電圧が印加されますが、この値は理論値です。

実際には前述したように各素子やパターンの寄生成分によってVo程度のスパイク(リンギング)電圧Vs*が重畳されるのでFETのVDSSはこのスパイク電圧に対してマージンを取らなければなりません。

経験的にはVDSS定格として(VCC+Vo+Vs≒2Vo+VCC)の1.25(=1/0.8)倍と考えます(80%ディレーティング)。この様子を1式で表しますが、この1式からVoは定電圧制御によって一定ですからVDSSの要求値は電源Vccの上限ほど大きくなることが分かります。

*FETのVDSS定格電圧が許せばスパイク電圧は抑制しない方がコンバーターの変換効率は高くなりますがノイズや他回路へのノイズの影響を考慮すると一般には1式程度に抑制するようにCRスナバー回路などが付加されます。CRスナバー回路の検討については昇圧コンバーターの章(連載第10回)で説明しましたのでここでは省略します。

Id(DC):理想放熱条件において連続的に流すことのできるFETの定格電流です。

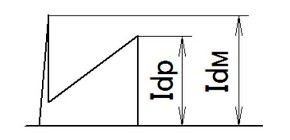

ドレイン電流の各部の波形の定義を図2に示します。

M1のドレインには既に説明したようにオン期間ton中にチョーク電流ILが流れます。その最大値ILPは、

でIdPはこのILPそのものですがこの値も理論値です。

実際のFETのターンオン時には前述のヒゲ状のターンオンピーク電流IdMが重畳されます。ですが、この項目についてはドレイン電流のパルス定格Id(Pulse)が定義、保証されているので測定値IdMはId(Pulse)定格の80%に収まっていれば問題はありません。したがって必要な電流定格の値は次の2式、3式の値になります。

3式のIdPは基本的には入力最低時の条件で測定します。ですが電源VCCの内部抵抗が大きいと負荷短絡時などでは電流が制限されるケースもありますので確認のために入力電圧を変えて測定を行ってください。VCCによる電流制限を考えなくても良い場合は入力最低時で測定します。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:反転形DC/DCコンバーターの基本回路構成図

図1:反転形DC/DCコンバーターの基本回路構成図 図2:ドレイン電流波形の定義

図2:ドレイン電流波形の定義