高速シリアルインターフェースのオンチップテスト回路(2/2 ページ)

オンチップのテスト機能の効果

続いて、オンチップのテスト回路を用いたテストの実現方法について説明する。

高速シリアルインターフェースの物理層の性能をテストする際には、ビットエラー率(BER)、非同期BER、送信電圧振幅、アイマスク、送信ジッター、受信オフセット、受信電圧振幅などが一般的な項目として使われる。これらのうちのほとんどは、帯域の広いA-Dコンバータを使ったアナログ信号測定を利用して評価することになる。A-Dコンバータを使って信号をデジタル化して利用する1つの理由は、パッケージや入出力チャンネルなどで生じる影響を除去するためである。

チップ内の動作を可視化して検証するためにモデルとすべきなのは、標準的なデジタルスキャンテスト手法である。デジタル回路のテストでは、制御回路によってシリアルスキャンデータをレジスタに格納し、各レジスタをスキャンする。テストパターンの開発とテストカバレッジの評価には、ソフトウエアツールが利用できる。スキャン回路の搭載によって内部信号を容易に観測でき、自動テストを簡単に実施できるようになる。デジタルスキャン回路の搭載によるチップ面積の増加は、一般的にはチップ全体の15%未満にとどまる。

チップ内のアナログ回路に対してデジタル回路のスキャンテストと同様のことを行うには、テスト用のバスが必要となる。図2に示したのは、2本のフォース線と2本のセンス線で構成されたアナログテストバスの例である。これを利用することで、4端子のJTAG(Joint Test Action Group)インターフェースを介して、設定作業と測定作業を実行できる。

アナログテストバスに加え、バスの周囲に必要とされるリソースもチップに集積する。それよって物理層の動作をフルにテストすることが可能になる。多種多様なアナログテスト機能をシリコンチップ上に集積するのである。その場合、必要なリソースはすべてチップ上にあるので、物理層に対する外部からのアクセスは、簡素なデジタルポートを介するだけで済む。そして、アナログテストの結果は、すべてパス/フェイル判定で行える。このように、すべてのアナログテストをJTAGのような簡単なデジタルインターフェースの入出力に置き換えることで、高価なアナログテスト装置を利用しなくても済む。

送信電圧振幅など、オンチップのA-Dコンバータで変換して得た値は、許容値であろうとなかろうと時間的に連続した値として取り込まれる。このデジタル値をテスターで読み取り、許容値に対するパス/フェイル判定を行う。ただし、デジタル値を読み込んでパス/フェイル判定を行うには、そのためのプログラムを記述する必要がある。そして、このプログラムをさまざまななテストプラットフォームでデバッグしたりメンテナンスしたりする担当者を設けなければならない。とはいえ、この部分については効率化を図る手法が存在する。

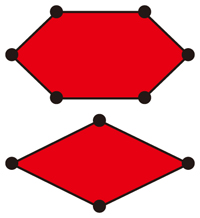

図4 アイマスクの例 上は6角形のアイマスク、下は菱形のアイマスク。マスクの各頂点における電圧と位相を指定することで使用する。SoC上のアナログテストバスに接続された比較レジスタは、オンチップの信号の値が、頂点に指定した値で決まる範囲に含まれるか否かを自動的に判定する。6角形のアイマスクでは、例えば次のようにして6つの頂点を指定する。(1)電圧が100mVで位相が0.2UI(UnitInterval)、(2)電圧が100mVで位相が−0.2UI、(3)電圧が−100mVで位相が0.2UI、(4)電圧が−100mVで位相が−0.2UI、(5)位相が0.4UI、(6)位相が−0.4UI。菱形のアイマスクでは、例えば次の4つを頂点として指定する。(1)電圧が100mV、(2)電圧が−100mV、(3)位相が0.4UI、(4)位相が−0.4UI。

図4 アイマスクの例 上は6角形のアイマスク、下は菱形のアイマスク。マスクの各頂点における電圧と位相を指定することで使用する。SoC上のアナログテストバスに接続された比較レジスタは、オンチップの信号の値が、頂点に指定した値で決まる範囲に含まれるか否かを自動的に判定する。6角形のアイマスクでは、例えば次のようにして6つの頂点を指定する。(1)電圧が100mVで位相が0.2UI(UnitInterval)、(2)電圧が100mVで位相が−0.2UI、(3)電圧が−100mVで位相が0.2UI、(4)電圧が−100mVで位相が−0.2UI、(5)位相が0.4UI、(6)位相が−0.4UI。菱形のアイマスクでは、例えば次の4つを頂点として指定する。(1)電圧が100mV、(2)電圧が−100mV、(3)位相が0.4UI、(4)位相が−0.4UI。それには、シリコンチップに内蔵したレジスタを利用する。まず初めに、アナログ許容値の上限値と下限値、測定の実施命令をチップ内に書き込む。各テストに対応してパス/フェイルを表すビットを設定しておき、パス/フェイル判定のためにスキャンを実行する。このようにすれば、この部分の詳細なテストプログラムを記述する必要はない。ソフトウエアツールによって、従来のデジタルスキャンテストと同様に入力ベクターと比較ベクターを作っておくだけでよい。このようにレジスタとA-Dコンバータをチップ上に搭載することで、任意のテストプラットフォーム、任意の簡単なデジタルテスターによってアナログ特性のテストを実行できるようになる。

オンチップのテスト機能をデジタルスキャンテストのように簡単に使いこなすには、ソフトウエアツールによって標準的なアナログテストをデジタルテストのパターンに変換する必要がある。そのソフトウエアツールは、膨大な量の設定と回路に関する知識をエンジニアに要求しないパス/フェイルテストを生成できなければならない。

回路コア(IP)として物理層を入手できる機会が増えることは、シリアルインターフェースを簡単にテストする手法を提供するIPベンダーが増えるということを意味する。それにより、IPユーザーはIPの内部に関する知識やシリアルインターフェース規格の技術的な詳細に関する知識がそれほどなくても、アナログテストの準備を迅速に進められるようになる。アイマスクを利用したテスト手法はその代表例だろう。

各種インターフェース規格では、アイパターンを用いた判定を行えるようにするためのアイマスクを定義している(図3)。実際のテストでは、チャンネルに生じる歪(ひずみ)を考慮して、規格に定められているものよりも大きいアイマスクを使用するのが一般的である。ユーザーは菱形のマスクや6角形のマスクを利用し、その各頂点における電圧と位相のパス/フェイル判定値を指定する(図4)。一方、ソフトウエアは、デバイスを適切に設定するためのベクターを生成し、指定されたアイマスクを適用する。すると、SoCからパス/フェイルの結果が返ってくる。この手法においては、アナログ的で詳細な知識は不要である。

信号の観測がいつでも可能に

オンチップのテスト回路を利用する手法は、低コストであることに加え、フィールドでのデバッグとテストにも応用できる。オンチップのテスト回路を使えば、受信端におけるアイパターンの表示のほかに、いくつかの重要なパラメータの測定も行える。この機能を使うことで、フィールドで生じた問題に容易に対処できるようになる。送信器によるプリエンファシスと受信器によるイコライゼーションが普及するに連れ、リンク上のさまざまな設定が与える影響をいつでも測定できる機能は重要性を増す。

外部の簡素なループバックを用いた従来のテスト手法は、高速だが正確さに欠ける。一方で、高価で洗練されたミックスドシグナルテスターを使うと、余分なオーバーヘッドが伴うことに加え、複雑なテストプログラムを記述してデバッグを行うという負荷が生じてしまう。

オンチップのテスト回路を活用すれば、高速シリアルインターフェースを安価なデジタルテスターで短い時間に実速度でテストできる。コンプライアンステストなどが要求するアイマスクや、非同期電圧余裕、送信レベルなどの試験に向けた検証済みのデジタルテストパターンを自動的に生成する手法も利用可能である。さらに、インターフェースのデバッグと特性評価にもオンチップのアナログテスト回路は利用できる。

Copyright © ITmedia, Inc. All Rights Reserved.