微細化に堪え得るオンチップSRAM:ワード線電位制御の効果を知る(3/3 ページ)

試作による確認

最後に、ワード線電位制御を適用したテストチップの試作結果を紹介する。この技術を利用すれば、セルの安定性が高まり、不良率を下げることができる。そのため、同じデザインルールでも、より小さなセル面積を実現可能である。

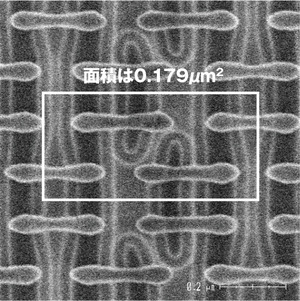

筆者らは、40nm世代のトレンドにのっとった既存セル(面積は0.20μm2)をベースとし、チャンネル面積を20%縮小することでセル全体の面積を10%削減した試作品を開発した(写真1)。その0.179μm2という面積は、40nm世代のセルとしては現在報告されている最小のサイズである。

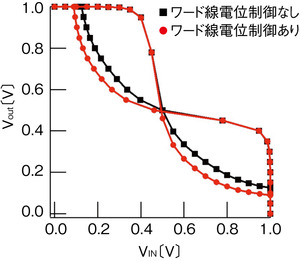

このセルのバタフライカーブの測定結果を図12に示した。ワード線の電位を下げることでバタフライカーブが大きくなっており、より安定なセルになっていることがわかる。

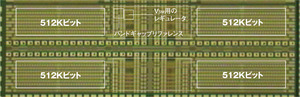

図13は、このセルを搭載した2Mビットのテストチップ(写真2)の評価結果である。これは電源とワード線の電位を変化させて行った試験の結果であり、パス、フェイルの判定結果をそれぞれ「P」、「F」で表している。nMOS/pMOSがそれぞれSlow/Fast(SF)、Fast/Slow(FS)の2つの条件のチップについて試験した結果を重ねて表記しており、1文字目がSF条件のチップのP/F、2文字目はFS条件のチップのP/Fを表している。例えば、「PF」という表記の場合、SF条件のチップはパスで、FS条件のチップはフェイルという意味である。

ワード線電位VWLが固定である従来の構成は、図のいちばん左列の設定、すなわちワード線電位の降圧量(VSM−VWL)が−0.0Vの条件に相当する。この場合、SRAM用電源VSMが1.2Vであっても、FS条件のチップではフェイルしてしまう。

ここでプロセス条件ごとにワード線電位制御を行うと、SF条件のチップの場合にはワード線電位が最も高い設定(−0.0V)とすることで、VSMを0.9Vまで下げてもパスする。また、FS条件のチップの場合には、ワード線電位を125mV下げた設定(−0.125V)にすることで、VSM=0.8Vでもパスするようになる。このように、条件ごとに最適なワード線の電位を設定することで、0.179μm2のセルでも安定して動作させることが可能である。

以上、本稿ではプロセスの微細化に伴う局所ばらつきの問題と、その問題がSRAMに及ぼす影響について述べた。その上で、これらの問題への対策の一例として、ワード線電位制御について説明した。SRAMセルの微細化トレンドを維持するには、このような回路技術の導入がますます重要になると考えられる。

微細化に対処するためのその他の技術

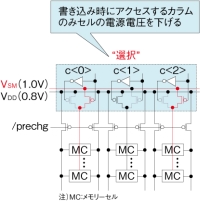

本稿で紹介したワード線電位制御以外にも、SRAMセルの安定性を向上するための回路技術が存在する。例えば、書き込み時にアクセスするカラムのセル電源電圧のみを下げるように動的な制御を行うことで、アクセスしていないセルを不安定にすることなく書き込みマージンを改善する方法(図A)*A)や、書き込み時にビット線を負電位にする方法*B)など、各種のバイアス制御方式が提案されている。

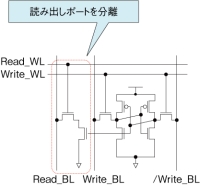

また、セルの面積は増加してしまうが、セル自体をよりばらつきに強いものに変更するという考え方もある。例えば、通常の6トランジスタ型セルに読み出し用ポートを追加した8トランジスタ型セルを使用することで、読み出し時のデータ破壊は起こらなくなる(図B)*C)。

脚注

※A…K. Zhang, et al., "A 3-GHz 70-Mb SRAM in 65-nm CMOS Technology With Integrated Column-Based Dynamic Power Supply," J. Solid-State Circuits, vol. 41, pp.146-151, Jan. 2006

※B…K. Nii, et al., "A 45-nm Single-port and Dual-port SRAM family with Robust Read/Write Stabilizing Circuitry under DVFS Environment," Symp. VLSI Circuits, pp.212-213, June 2008

※C…L. Chang, et al., "Stable SRAM Cell Design for the 32nm Node and Beyond," Symp. VLSI Technology, pp.128-129, June 2005

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- 次世代車載向けセキュリティコントローラー