微細化に堪え得るオンチップSRAM:ワード線電位制御の効果を知る(1/3 ページ)

ICの製造プロセスの微細化を進めるには、それに伴って生じる新たな課題に対処していかなければならない。そうした課題の1つが、プロセスばらつきの影響に堪え得るオンチップのSRAMを開発することである。今後も、SRAMの微細化トレンドを維持するためには、従来とは異なる技術的な工夫を盛り込む必要がある。

微細化で生じる問題

SRAMは、CMOS ICのオンチップメモリーとして多用されている。ICの開発者/利用者にとっては、最も身近なメモリーだと言えよう。オンチップメモリーとして用いられる理由としては、特殊なプロセスを必要としないので製造が容易であることや、リフレッシュ動作などが不要なので使いやすいことが挙げられる。

その半面、SRAMは製造プロセスの微細化に伴う諸問題にいち早く直面している存在だとも言える。そのため、近年は、この点について学会などで盛んに議論が行われている。単位面積当たりの記憶容量を増やすことを目的とし、SRAMのメモリーセルには、通常のロジック回路で使用されるものよりも微細なトランジスタが使用される。結果として、最先端プロセスを使用したICの設計では、微細化に伴う問題がSRAMにおいて最初に顕在化しているのである。

では、プロセスの微細化によりトランジスタの素子サイズが小さくなることで何が問題になるのだろうか。それは、トランジスタ特性の局所ばらつきである。ここで言う局所ばらつきとは、単一チップ中のトランジスタ1個ごとに異なる値で生じるばらつきのことを指す。

局所ばらつきが生じる最も大きな原因は、トランジスタごとの不純物原子(ドーパント)数の“揺らぎ”である。トランジスタの微細化により、トランジスタ1個当たりに注入されるドーパント数が減少した結果、注入されるドーパントの数や分布の揺らぎが、トランジスタごとの閾(しきい)値電圧(Vth)に大きな変動を生じさせるのだ。

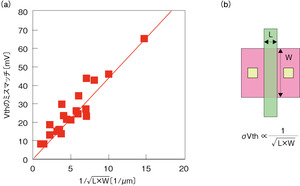

図1に、Vthのミスマッチとトランジスタサイズの関係を示した。ここで言うVthのミスマッチとは、まったく同じ構成のトランジスタを2つ隣接して配置した場合のVthの差のことである。これがVthの局所ばらつきに相当する。図1(a)のとおり、隣接したまったく同じサイズのトランジスタであっても、Vthにはばらつきが生じる。そして、トランジスタサイズが小さくなるほど、ばらつきは大きくなる。一般的に、ドーパント数の揺らぎによるVthの局所ばらつきは、トランジスタのチャンネル面積(=ゲート長L×チャンネル幅W)の−1/2乗に比例することが知られている(図1(b))*1)。チャンネル面積が小さいほど局所ばらつきは大きくなるため、ICにおいて最も微細なトランジスタで構成されるSRAMで顕著な問題となっているのである。

SRAMの微細化トレンド

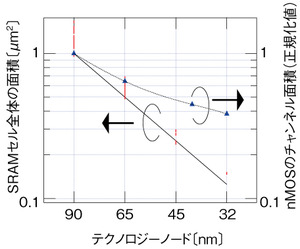

最近では、オンチップメモリーとして使用されるSRAMの総容量は数十Mビットに及ぶ。そのため、SRAMセルの面積の大小がチップ面積に大きなインパクトを及ぼす。このことから、SRAMセルに対するスケーリングの要求は依然として強い。SRAMにおけるメモリーセルの面積は、世代ごとに半分となるスケーリングのトレンドを維持している(図2)。各社このトレンドに沿った微細メモリーセルの開発を進めてきている。

図2のグラフには、メモリーセルに使用されているnMOSトランジスタのチャンネル面積のトレンドも併せて示している。セル全体の面積は、世代ごとに半分になるというトレンドをキープしているのに対して、トランジスタのチャンネル面積はセル面積ほどには縮小されなくなっていることが見て取れる。その理由となっているのが、前述した局所ばらつきの増大である。チャンネル面積をセル面積と同じ比率で縮小していくと、局所ばらつきが増大し、メモリーセルが正常に動作しなくなってしまう。このため、チャンネル面積は縮小せず、その他の部分を縮小することにより、セル全体の面積を削減しているのだ。

このように、微細プロセスにおけるオンチップSRAMのメモリーセルでは、ばらつきを考慮した上でチャンネル面積を確保することが重要となっている。そして、このことが、セル面積の限界を作る大きな要因になってきている。上述したとおり、現状はチャンネル部を縮小できない分、その他の部分をよりアグレッシブに縮小することで、セル面積のスケーリングのトレンドを維持している。しかし、この考え方では、微細化が進むほどチャンネル部の割合が増大するので、ますます条件が厳しくなっていく。従って、今後もトレンドを維持するためには、別の対策が必要となるのである。

ディスターブ不良

ここで、局所ばらつきの増大により生じるSRAMの問題についてもう少し詳しく説明しよう。

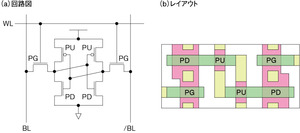

図3に、一般的な6トランジスタ型のSRAMメモリーセルの回路図とセルレイアウトを示した。6トランジスタ型セルでは、2つのインバータから成るフリップフロップによって「0」、「1」のデータを記憶する。読み出し/書き込みは2つの転送ゲートPGを介して行う。通常、ビット線の対(BL、/BL)は電源電圧に充電されている。読み出し(ディスターブ)時にはワード線(WL)がハイレベルになる。フリップフロップのデータに応じ、一方のビット線が一方のPGを介してローレベルへと放電されることでデータが読み出される。このとき、ワード線がハイレベルになることで、PGによってフリップフロップの両出力がわずかにプルアップされる。その影響で、この不安定なフリップフロップのデータが反転してしまい、データの破壊という結果に至ることがある。これが、SRAMのディスターブ不良である。この不良モードは、前述したVthの局所ばらつきによって生じる。

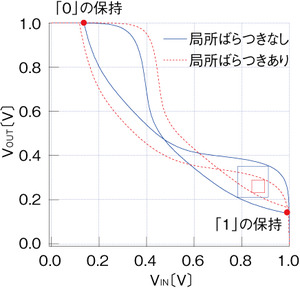

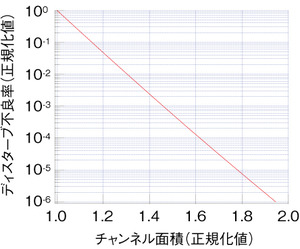

図4は、SRAMセルにおいてフリップフロップを構成するインバータ対それぞれの入出力特性をX/Y軸を反転して重ねたものである。これは「バタフライカーブ」と呼ばれている。2つの曲線の両端にある交点が安定点であり、これらが0、1のデータそれぞれを記憶している状態に当たる。このバタフライカーブにおいて、2つの曲線に囲まれた領域に内接する正方形の大きさが、セルの安定度の指標として用いられている*2)。もし、各トランジスタに局所ばらつきがなければ、図中の青い線のような状態になる。一方、局所ばらつきによって各トランジスタのVthが変動すると、赤い点線のように、バタフライカーブに歪(ひずみ)が生じる。その結果、2つの曲線に囲まれた領域に内接する正方形が小さくなる。さらに局所ばらつきが大きくなると、曲線が交わらないものが発生する。この場合、0、1のデータを保持できず、メモリーセルとして正常に機能しなくなってディスターブ不良となる。ディスターブ不良の発生確率は、Vthのばらつきの大きさに依存する。言い換えれば、チャンネル面積から大きな影響を受ける。

図5は、メモリーセルのフリップフロップを構成するnMOSトランジスタ(PD)のチャンネル面積とディスターブ不良の発生確率の関係を表したものである。この図から、チャンネル面積を1割削減すると、ディスターブ不良の発生確率が一桁近く増えてしまうことがわかる。これがチャンネル面積のスケーリングが困難になっている理由である。

ここで見方を変えると、回路設計の工夫などのアプローチにより、不良率を低減することができれば、その分、チャンネル面積の縮小を許容できることになる。前述したように、現状はチャンネル面積によってセル面積に限界が生じている。逆に言えば、チャンネル面積を縮小できるならば、現状のデザインルールのままで、さらに小さなメモリーセルを実現できることになる。また、次世代のプロセスでスケーリングのトレンドを維持することも可能になる。以下では、セル面積の削減を実現可能にする回路設計によるアプローチの例として、ワード線電位制御について説明する*3)。

脚注

※1…M. J. M. Pelgrom, et al., "Matching Properties of MOS Transistors," J. Solid-State Circuits, vol. 24, pp.1433-1439, Oct. 1989

※2…E. Seevinck, et al., "Static-Noise Margin Analysis of MOS SRAM Cells," J. Solid-State Circuits, vol. 22, pp748-754, Oct. 1987

※3…O. Hirabayashi, et al., "A process-variation-tolerant dual-power-supply SRAM with 0.179μm2 Cell in 40nm CMOS using level-programmable wordline driver," ISSCC Dig. Tech. Papers, pp.458-459, Feb. 2009

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- 次世代車載向けセキュリティコントローラー