SoC設計フローの変化:微細化と最新EDAツールがもたらす(2/3 ページ)

事前計画の重要性

ここからは、最先端のSoCの設計事例を基に、これからのSoCの設計フローにおいてどのようなことに留意すべきかを説明する。

米Open-Silicon社は、ゲート数が1億個に達する無線ネットワーク機器用SoCを開発した。チップの製造に用いるのは、台湾TSMC(Taiwan Semiconductor Manufacturing Company)社の65nm CMOSプロセスである。Open-Silicon社のエンジニアリング担当バイスプレジデントを務めるTaher Madraswala氏は、「このチップの設計において最も重要だったのは、設計フローに実際に入る前の事前の計画であった」と述べる。

Open-Silicon社は、ファブレス半導体企業である中国HiSilicon社に、このSoCの要件設計とRTLのコーディングを依頼した。また、ASIC設計サービス企業である中国Brite Semiconductor社と共同で物理設計(レイアウト)に取り組んだ。Madraswala氏は、「このような分業体制を事前に計画することにより、このSoCの設計フローは、ほぼトップダウン設計と言えるものになった」と述べる。また同氏は、「事前の計画の大部分は、クロックの設計に関することに費した」とも指摘している。

まずOpen-Silicon社は、設計するチップに対する理解を深めることと、リスクの評価に注力した。Madraswala氏によれば、「非常に長い道のりを経なければ完成しない、非常に大きなチップになることがわかっていた。そこで、クロック構造を理解するためだけにも、3日間を費やしてミーティングを行った」という。また、機能ブロックを配置するための前準備として、さまざまなクロックのソース、使用個所、ゲーティング構造についても理解しておく必要があった。これらを理解していなければ、クロックタイミングのクロージャを達成するのは、まず不可能だっただろう。

また同社は、このSoCを設計する上で複数のIPコアを扱う必要があった。IPコアは、基本的にピン配置が固定であるため、機能ブロックを配置する際に制約が生じる。Madraswala氏は、「ここで問題になるのは再現性だ。IPコアを配置する方向を変えると、重要な配線の長さが変わり、タイミングが変化してしまう」と説明する。そこで、同社の設計チームは、最初にトップレベルの信号、クロック、I/Oに関する予備的な配線を行った。その上で、この予備配線を、設計の分割(パーテショニング)と機能ブロックの配置の基盤として利用した。

初期段階で行うべきこと

米Redpine Signals社の会長兼CEO(最高経営責任者)であるVenkat Mattela氏は、「現在、システムレベルで設計を分割するのは非常に困難なこととなっている」と述べる。その上で、同氏は「技術者は早い段階で電源に関する設計を行う必要がある」と指摘する。

Redpine社は、組み込み機器向けに、低消費電力のIEEE 802.11n対応トランシーバを設計した。その設計では、RTLコードを使ってモジュール定義を行った。それにより、各モジュールは、チップの電源設計の観点からは自己完結したものとすることができた。また、モジュールへの分割は、機能的な境界だけでなく、電圧アイランドとクロックドメインとの間の境界条件にも従った。その結果、設計チームは、RTLの各ブロックの電力要件を、設計の開始時にUPF(Universal Power Format)ファイルで把握することができた。

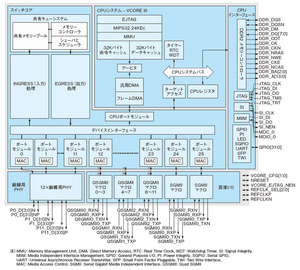

設計の初期段階で注意しなければならない問題はほかにも存在する。例えば、米Vitesse Semiconductor社は、銅線用のPHY(物理層)の集積ブロックを搭載する24ポートのスイッチング機器用SoC「VSC7427」を開発した(図1)。同社の設計担当ディレクタを務めるMandeep Chadha氏によると、「PHYブロックの消費電力によって、どれだけの機能を集積できるかをほぼ見積もることができる」という。これは、PHYブロックの消費電力が、チップの総消費電力のほとんどを占めるからである。同氏は、「設計フローの前段階では、消費電力が重要な問題となっていた。これは、当初からワイヤーボンディングパッケージをターゲットとしていたためだ」と述べる。ワイヤーボンディングパッケージは、フリップチップパッケージのような信号再分配層を持たないため、チップ上のI/Oの配置は、パッケージの端子の位置に合わせなければならない。その一方で、VSC7427の動作周波数を考慮すると、パッケージの端子の位置は、それを搭載するプリント基板のレイアウトにも適合したものでなければならない。Chadha氏は、「このような理由から、このSoCを搭載するスイッチング機器の物理的なレイアウトが、SoCのフロアプランに直接影響を与えることになった」と付け加える。

設計フローの初期段階では、電源管理と、トップレベル階層における信号/クロック/電源の配線という2つの問題が生じるが、EDAベンダーはこれらの変化に対応してきている。現在では、省電力を目的とした設計フローでは、初期段階において、電力に関する要件を、標準的なCPF(Common Power Format)ファイルもしくはUPFファイルを用いて把握することが推奨されている。これらのファイルは、SoC設計における合成、配置配線、検証という設計フローを通して、電源管理の機能を実装する上での指針となる。

EDAベンダーは、分割やフロアプランといった設計フローの初期段階において、設計チームは予備的な配線情報を必要とするということに注目している。米Mentor Graphics社の配置配線部門マネジャを務めるPravin Madhani氏は、「配線の混雑が、予期せぬ最大の問題となることがある。この問題を回避するためには、より早い段階で配置配線ツールを利用し、混雑の可能性がないかどうかを確認する必要がある」と述べる。このような背景から、配置配線ツールのベンダーは、設計の非常に早い段階で使用できるようにツールの機能を拡張している。

予期せぬ配線混雑の問題が発生してしまうと、その代償は大きなものとなる。Open-Silicon社のMadraswala氏は、「無線ネットワーク機器用SoCの開発では、いくつかのブロックで配線混雑の問題が生じた。それらを解決するためには、設計フローの初期段階に戻ってRTLコードを書き直す必要があった」と述べる。このような対処を行った結果、配線混雑が生じたブロックに対する検証や合成を再度実施しなければならなかった。ただし、Open-Silicon社は、HiSilicon社の中国のオフィスに自社の設計チームから6人の技術者を派遣しておいた。HiSilicon社のRTL設計の担当者に迅速にフィードバックを行うための経路をあらかじめ用意しておくことで、配線混雑の問題による影響を最小限にとどめることが可能になったという。

サードパーティのIPに予期せぬ配線混雑が存在する場合、問題はさらに深刻になる。例えば、そのIPのベンダーがRTLコードをスケジュール内に変更できるだけのリソースを持っていない場合や、配線混雑の原因がハードウエアIPブロックのピンに存在する場合はどうなるのだろうか。最悪の場合、SoCの設計チームが、IPベンダーに代わって作業しなければならないかもしれない。だからこそ、電源に関する設計に併せて、設計の分割および配置を行うことと、トップレベルの階層の配線を初期段階で用意することが、最も重要な取り組みになっているわけだ。

Copyright © ITmedia, Inc. All Rights Reserved.