FPGAの可能性を広げるプロセッサコア(後編):主要プロダクトと実装時の課題を解説!(1/2 ページ)

FPGAに実装できるプロセッサコアは、FPGAベンダーやIPベンダーから、さまざまなプロダクトが提供されている。それらは、ハードコアやソフトコアという違いだけでなく、機能、回路規模、コストなどについても異なっている。後編では、これらのプロセッサコアをFPGAに実装する際の課題について、インターコネクト、メモリー、アクセラレータ、デバッグという4つの観点に分けて解説する。

インターコネクトの選択

FPGAにプロセッサコアを実装するとき、それをどのようなアプリケーションで利用する場合であっても、バスやメモリーとのインターコネクト(相互接続)が必要になる。しかし、そのためのアプローチ方法は、プロセッサコアごとに異なっている。

ほとんどのバス規格が策定される以前から存在しているAlteraのソフトウエアベースのプロセッサコア(ソフトコア)「Nios」は、独自のインターコネクトシステム「Avalon」を持つ。Avalonでは、共有物理バスの問題を避けるため、一般的にスイッチマトリクスを使用している。しかし、最近になってAlteraは、Avalonの周囲にガスケットを配置することにより、ARMのバス規格「AXI(Advanced Extensible Interface)」に対応できるようになると発表した。これは、ARMが、プロセッサコアだけでなくバス規格などについても影響力を増大させつつあるからだ。また、Xilinxも、中核的なインターコネクトIP(Intellectual Property)としてAXIを採用する方針を表明している。

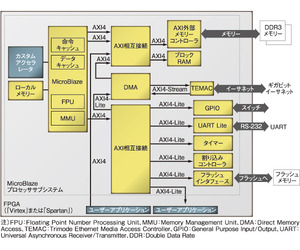

ユーザーが直面するインターコネクトの問題は、物理層だけに留まらない。Xilinxのマーケティング担当シニアバイスプレジデントを務めるVin Ratford氏は、「顧客が求めているのは単体のプロセッサコアではない。プロセッサコアを含めたエコシステムだ」と述べる。その要求に応えるために、ベンダーらはプロセッサコアだけでなく、メモリーや周辺機能などの各ブロックを接続し、合成とマッピングスクリプトを作成するという面倒な処理を行う、GUI(Graphical User Interface)ベースのシステム構築用ツールを提供している。例えば、Xilinxのソフトコア「MicroBlaze」を利用する場合、そのエコシステムとXilinxが提供するIPブロックを用いるだけで、高性能のマイクロコンピュータを構築できる。このとき、FPGA内部のインターコネクトも自動的に生成される(図2)。

Xilinxに限らず、主要なFPGAベンダーは、このような包括的なソリューションを提供している。Microsemiでのシニア製品開発マネージャを務めるTim Morin氏によると、「われわれのツールは、プロセッサ、メモリー、周辺機能、ARMのバス規格『AHB(Advanced High Performance Bus)』を接続するためのIPを提供する。ユーザーはツール上でブロックをドラッグアンドドロップするだけでよい」と述べている。

Lattice Semiconductorは、インターコネクトIPについても、プロセッサコアと同様にオープンソースにする方針を貫いている。Latticeのソフトコア「LatticeMico」は、インタフェースとしてオープンソースの「Wishbone」を採用している。同社のソフトウエア製品計画マネージャを務めるMike Kendrick氏によると、「Wishboneは、一見AlteraのAvalonに似ているが、細部は大きく異なっている。両インタフェースの間に互換性はない」と語る。また、Latticeも、ブロック図形式の入力からRTL(レジスタ転送レベル)コードを生成するシステム構築用ツールを提供している。

メモリーとの組み合わせ

高速RAMも、FPGAにプロセッサコアを実装する際に検討すべき課題の1つである。Linuxを組み込んで動作させるようなアプリケーションプロセッサには、大容量のセットアソシアティブ方式のキャッシュメモリー(以下、キャッシュ)が搭載されている。一方、実行するタスクの種類が決まっているタイプのプロセッサでは、より高速で簡素な構造のダイレクトマップ方式のキャッシュか、ARMのプロセッサコアにオプション的に実装される密結合メモリー(TCM:Tightly Coupled Memory)のようなRAMを使用することが多い。最新のFPGAは、大容量の高速ブロックRAMを搭載しているため、RAM自体の容量や速度が大きな問題になることはない。しかし、プロセッサコアとRAMの間の接続やメモリーコントローラの実装については困難さが付きまとう。

ARMのマイコン向けプロセッサコアであるCortex-Mシリーズを用いたFPGA製品に注力するMicrosemiは、ブロックRAMとプロセッサコアの接続を簡素なものにしている。Morin氏は、「ハードウエアベースのプロセッサコア(ハードコア)である『Cortex-M3』の基本仕様はキャッシュレスとなっている。そこでわれわれは、キャッシュとして、容量が32KバイトのハードウエアSRAMを2個、当社のFPGA『SmartFusion』のスイッチマトリクスポート上に搭載している。一方、ソフトコアであるCortex-M1を使用する場合にはキャッシュは使用しない。その代わり、ユーザーはシステム構築用のツールを介してTCMを指定することができる。これは、TCMをプロセッサコアに接続するためのラッパーを独自に用意することで実現した」と述べる。

Xilinxも、MicroBlazeのメモリー接続について、Microsemiと同じような保守的な方法をとっている。Xilinxのプロセッシング製品担当バイスプレジデントを務めるVidya Rajagopalan氏は、「ブロックRAMまたはLUT(Look-up Table)の中にキャッシュを実装することができる。キャッシュは、ダイレクトマップ方式のものを用いることがほとんどだ。メモリーコントローラをセットアソシアティブ方式に対応させることもできるが、処理が複雑になるので最大動作周波数が低くなるおそれがある」と説明する。

Alteraは、さまざまなアプリケーションで、プロセッサコアを搭載したFPGAが利用されていると見ていることから、メモリーについては多様な選択肢を設けている。同社の組み込み製品マーケティングマネージャを務めるNirmal Kari氏によると、「NiosのL1キャッシュは、オンチップのメモリーブロックと連携するソフトコントローラとして実装されている。最大動作周波数への影響を最小限に抑えつつ、セットアソシアティブ方式のキャッシュを実装することもできるが、その結果得られるシステム性能は実行するソフトウエアに依存する。また、キャッシュを用いることで、システム性能がよくなる場合もあれば悪くなる場合もある」という。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング