プリント基板のパワーインテグリティ(前編):シミュレーションツールの活用で実現する(1/2 ページ)

半導体技術の進展によってICの動作速度が向上し、これらのICを搭載する機器の性能が向上していることは周知の通りだ。その一方で、ICに電力を供給するプリント基板のパワーインテグリティの重要性も増している。本稿の前編では、プリント基板のパワーインテグリティが重要になっている背景と、パワーインテグリティを実現する上で必須となっているシミュレーションツールの役割について説明する。

困難さを増す電源分配回路の設計

プリント基板(PCB)上に実装したICに電力を供給する。これはもはや簡単な仕事ではない。従来は、専有面積の小さい、細い配線で電源とグラウンド(接地)にICをつなげばよかった。しかし、ICの動作速度が高まるにつれて、電源プレーンのような面状に広がる低インピーダンスの経路を介して電力を供給する必要が生じてきた。電源品質の確保、いわゆる「パワーインテグリティ」が極めて重要になっている。

かつては、4層基板によって電源プレーンとグラウンドプレーンを形成すれば、パワーインテグリティ問題のほとんどを解決できた。また回路上の細かい電源問題を回避するには、電源プレーンに加えて、ICごとに電源とグラウンドの間にデカップリング用のコンデンサを挿入するという手法も有効だった。

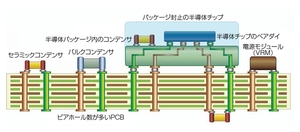

しかし最近では、PCBはコストや開発スケジュールだけでなく面積の要求条件も厳しくなっており、旧来の手法だけでは問題を解決しにくくなっているのが実情だ。その結果、PCBに作り込む電源分配回路の設計は極めて難しい作業になっている。Mentor Graphicsでシミュレーション/アナログ製品担当のシニアディレクタを務めるDave Kohlmeier氏は、「民生用機器や携帯型機器ではコストの制約があり、層数の少ないPCBを使っている。しかし、最近のICは電圧が異なる複数系統の電源を必要とするものが多くなっている。従って、少ない層数で電源品質を確保することが設計上の重要な課題になっている」と指摘する。この問題はモバイル機器だけでなく、スペースの制約が厳しい産業用機器でも同じだ(図1)。例えば携帯電話の基地局は、かつては19インチのラックに組まれており、それが建物の中に据え付けられていたが、今ではアンテナの上部に取り付けた小さな箱(いわゆるリモートラジオヘッド)に納まるようになっている。

大量生産される民生用機器や車載機器は、コスト要求が非常に厳しい。従って、必要かどうか分からないコンデンサをPCB上にむやみに実装するわけにはいかない。また、完成までに許容される設計期間についても、今や年単位ではなく、月単位さらには週単位のレベルまで短縮することが求められており、ますます厳しくなっている。こうなってくると、電源プレーンやグラウンドプレーンの不具合を修正し、最適化するためにPCBの設計を手直しする時間の余裕は無い。

こうした外的要因の一方で、電力の供給を受けるIC側の事情も、PCBの電源分配回路の設計を難しくしている。DDRメモリチップのデータ転送速度は既に1600Mビット/秒に達しており、遠くない将来に2200Mビット/秒を超えるようになるだろう。高速化に加えて、さらに問題を難しくしているのは、DDRメモリチップがシングルエンド出力であり、その電源系が負荷電流の急激な変動に対応できなければならないということである。メモリチップ上でメモリインタフェース回路を構成する数多くのデジタルゲートが同時にスイッチング動作することで生じる「同時スイッチング雑音(SSN)」の低減に取り組む必要がある。また、高速シリアル通信を利用する場合にも、電源品質の確保が大きな課題になる。例えば次世代イーサネット規格であるIEEE 802.3baの場合、40Gビット/秒や100Gビット/秒という極めて高い速度でデータを伝送するので、それに対応できるように電源系の品質も高めなければならない。

さらに、最近のデジタルICは電源電圧が低下しており、1Vを切るものもある。これは、ミリボルト(mV)オーダーの雑音でもデータに依存する問題を引き起こす可能性があることを意味する。1つの電源で複数のICに給電することは可能だが、電源電圧の低下や過電圧の問題を生ずる危険性がある。そうした設計のシステムでも、数週間あるいは数カ月間にわたって正常に動作し続けるかもしれない。しかしそのデジタル回路がひとたび同時スイッチング動作すれば、負荷電流の急激な変動を引き起こし、システムの再起動が必要な事態に陥る可能性がある。

アナログとRFの知識が不可欠

これらのパワーインテグリティの問題は、トラブルシューティングが難しい。あるシステムにおいて、1つのICのパワーインテグリティ問題が、そのシステム内の別のICで再起動が必要になる事態の原因になる場合もある。National Semiconductor(2011年9月にTexas Instrumentsが買収)のアナログアプリケーションエンジニアであるPaul Grohe氏は、「ナノ秒程度の瞬間的な電源の遮断でも、システムの安定性を損なう原因になり得る」と指摘する。また、ANSYSでシグナルインテグリティ製品のマネジャーを務めるSteve Pytel氏は、「電源雑音の最小化は、回路の信頼性を確保するために不可欠だ。これは、デジタルシステムの技術者であっても、アナログ回路やRF(高周波)回路の設計技術を学ぶ必要があることを意味している」と述べている。

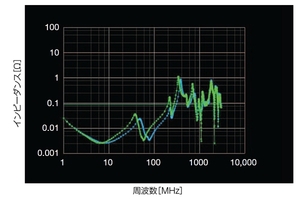

電源分配回路に取り組む技術者であれば、電源系のインピーダンスを低く抑える必要があることを理解しているだろう。そして、アナログ技術者であればアナログICの電源端子の雑音は小さければ小さいほど良いということを理解しているはずだ(図2)。しかし、デジタルICとは異なり、アナログICには雑音に対するマージンが存在しない。アナログICのPSRR(電源電圧変動除去比)は、電源雑音がICの出力ピンにどれだけ漏れ出すかを規定した特性である。デジタルシステムの技術者は、これと同じ電源雑音の問題に対処しなければならなくなっている(別掲の囲み記事『理解できない? アナログ技術者の用語』を参照)。

理解できない? アナログ技術者の用語

パワーインテグリティに取り組む設計技術者は、電源系の設計に関する基本的な概念を持ち合わせていないデジタルシステムの技術者と話をする際に違和感を覚えることがあるだろう。例えば、Cisco SystemsのシニアパワーエンジニアであるBob Thomas氏は、あるFPGAベンダーのデジタル設計技術者たちとの会話にいら立ちを覚えることが少なくないという。Ciscoは、このFPGAベンダーから製品を購入している。同氏によると、アナログや電源系の設計者たちが使う用語を、そのデジタル設計技術者たちは理解できないというのだ。

こんなことがあった。デジタルシステム技術者はThomas氏に対し、あるICが求める電源雑音特性が−20dBだと告げた。「dB」は相対値なので、この数字の意味を理解するにはその基準が何なのかを知る必要がある。そこで同氏は「−20dBとは、いったいどこから20dBダウンなのですか?」と聞き返さなければならなかった。しかしそのデジタルシステム技術者は、「電源雑音は−20dB以下にしてください」と繰り返すだけだったという。

Thomas氏は、それがdBm(1mWを0dBとした電力の絶対単位)や他の電力測定値を指しているわけではないと分かっていたので、「誰か他の方と替わってもらえますか」と伝えた。そのデジタルシステム技術者はしばらく抵抗したが、最終的には他の技術者に電話を代わった。ところが、交代した技術者もまた同氏が納得できるような仕様を教えることができなかった。「誰か他の方と替わってもらえますか……」。仕方なく、同氏はまたそう告げた。同氏はこのやり取りを4人の技術者と繰り返さなければならなかったという。最後に、アナログ/電源分野の用語を理解できる技術者が応対したことにより、Thomas氏は電源雑音の正しい仕様を聞き出すことができ、ようやく設計を進めることができた。

皆さんがデジタルICのベンダーと話をするときは、Thomas氏のエピソードを思いだしてほしい。先方は善意であなたの役に立ちたいと思っているかもしれないが、あなたは話している相手がアナログの素養を備えた技術者であることを確かめた方がいいだろう。デジタルICのベンダーも必ずそういう技術者を雇用しているので、あなたはそれを探し当てる必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング