シリコンパワーMOSFETの性能改善、素子構造よりもパッケージが効く時代に:パワー半導体(1/2 ページ)

SiCやGaNを使う次世代パワー半導体の開発が進んでいるものの、当面は旧来のシリコン材料を用いたパワーMOSFETが広く使われるだろう。ただしシリコン品の性能を高めるには、もはや半導体素子構造の改良では間に合わない。ウエハー処理の後工程となる組み立てプロセスとパッケージ技術の進歩が貢献する。

SiC(炭化ケイ素)やGaN(窒化ガリウム)など、ワイドバンドキャップ半導体を使った新しいスイッチング用パワートランジスタの登場によって、電力変換効率は大幅に向上していくだろう†1。

しかし現在、最も普及しているのは従来のSi(シリコン)パワーMOSFETであり、この状況は今後もしばらくは続くとみられる。そのパワーMOSFET技術の動向を調査する場としてうってつけなのがパワーエレクトロニクス分野で最大の学会兼展示会である「APEC(The Applied Power Electronics Conference and Exposition)」だ。2012年は2月5〜9日に、米国フロリダ州オーランド市で開催された。

パワーMOSFETは耐圧(VB)によって市場が分かれている。一般に、40V未満、100V未満、600V未満の3種類に分けられる。パワーMOSFETの応用分野としては民生用電子機器とサーバ/ノートPCが最も大きいことから、通常、耐圧100V未満のMOSFETを性能指標として使う。

素子構造の改善はもはや役に立たない

これまでシリコンパワーMOSFETは、デジタルICのプロセス技術の進化に便乗する形で技術を進展させることができた。デジタルICでは、ムーアの法則に沿ったプロセス技術の微細化によってトランジスタ密度が増加する。パワーMOSFETにおいても、それと同じような“規模の経済”によって、「性能が向上しても価格は下がる」という傾向が続いてきた。しかし、そうした平和で幸福な日々は終わった。シリコンMOSFETは、シリコン技術による性能向上の限界に近づきつつある。

米International Rectifierでパワーマネジメントデバイス事業部門のディレクターを務めるステファン・エルノー(Stéphane Ernoux)氏は、「今後は、シリコン技術への投資をいくら増やしても、性能の改善度合いは少なくなるばかりだ」という。

同氏が言う「投資を増やす」とは、さらに複雑なシリコン技術を開発するという意味だ。その背景には、シリコンチップ自体を改善しても、パッケージ技術が妨げとなって性能向上が滞るようになったという事情がある。同氏は、「5年前、10年前、15年前を振り返ってみると、シリコンチップに全ての開発力が注がれ、パッケージ技術はMOSFETの性能向上にあまり役立っていなかったといえる。しかし現在、シリコンチップ自体の性能は非常に高くなったため、パワーMOSFETメーカーはパッケージ技術の開発に注力すべきだろう」と語る。

ウエハー薄化とパッケージ技術が効く

シリコンパワーMOSFETの電力密度を今以上に高めるには、3つのアプローチがある。1つ目は半導体素子(デバイス)の構造で、エルノー氏も「まだ改良の余地が少しばかり残っている」と認めている。2つ目はウエハー薄化技術の向上であり、3つ目は新しいパッケージ技術の開発である。

半導体メーカーは通常、ウエハーメーカーがスライスし、研磨処理を1回施したウエハーを購入する。そしてそのウエハー上にMOSFETを形成する。パワーMOSFETは縦型のデバイス構造を採るため、オン抵抗を減らすにはウエハーをできるだけ薄くすることが重要である。

ウエハーの薄化、すなわち研磨処理は、ウエハー処理の最後に実施する。初期のMOSFETは、厚さ8ミル(1000分の8インチ、約0.2mm)のウエハー上に形成されていた。しかし現在は、厚さ2ミル(約0.05mm)のウエハーが一般的になっている。

半導体メーカーはこの10年間、IGBTの製造時にウエハーの薄化技術を適用してきた。IGBTを薄化する理由はパワーMOSFETとは違う。オン抵抗を減らすためというより、薄化によって絶縁破壊電圧を高く維持できるというメリットがあるためだ。

メーカーは通常、反りの少ない6インチ径ウエハーを使ってIGBTを作り込む。この場合、薄化はそれほど難しくない。一方でMOSFETは、2〜3年前に8インチ径ウエハーに移行したものの、薄化と8インチという大口径ウエハーのハンドリング時に生じる破損のため、歩留まりが低くなってしまった。そのためMOSFETメーカー各社はその課題を克服するための技術を開発しなければならなくなった。キャリア基板を使って薄化したウエハーをハンドリングする技術である。

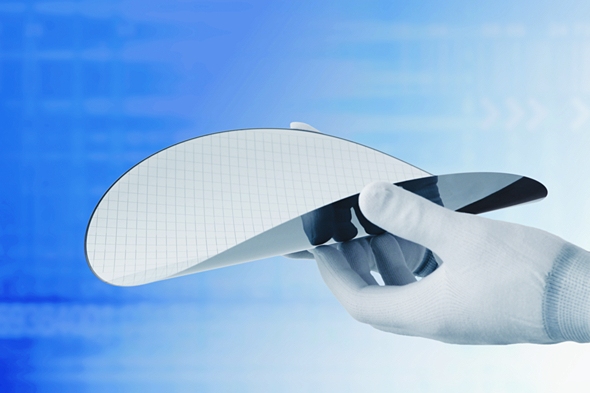

独Infineon Technologiesは2011年末に初めて、オーストリア南部のフィラッハ市にあるパワー半導体の開発拠点で、薄化した300mm(12インチ)ウエハーを使用したパワーMOSFETのサンプル品を製造した(図1)。同社によると、300mmの大口径ウエハーながら、200mmウエハーを使用して製造した同等のチップと同じ特性が得られたという†2。

図1 Infineon Technologiesが製造したパワー半導体向け300mmウエハー 同社は、直径300mm(12インチ)の薄いウエハー上にパワーMOSFETを形成した。同チップは200mmウエハーを使用して製造した同等のチップと同じ特性を実現しているという。

図1 Infineon Technologiesが製造したパワー半導体向け300mmウエハー 同社は、直径300mm(12インチ)の薄いウエハー上にパワーMOSFETを形成した。同チップは200mmウエハーを使用して製造した同等のチップと同じ特性を実現しているという。接合技術が重要

現在、ウエハーの薄化とシリコンデバイス構造の改善によって、パワーMOSFETのオン抵抗はかなり小さくなった。そのため、パッケージ部分の抵抗と、リードフレームとチップ接着部の寄生インダクタンスが重視されるようになっている。

ワイヤボンディングは比較的細くて損傷を受けやすいため、大電流を流しにくい。そのため、大電力を扱う高性能デバイスではワイヤボンディングに代わってクリップが標準的に使われるようになりつつある。クリップを使うと、オン抵抗を低減できる上に、スイッチング速度を遅くする要因である寄生インダクタンスも抑えることが可能だ。

MOSFETで一般的に使用される性能指標(FOM:Figure of Merit)は、オン抵抗とゲート電荷によって決まり、以下のように表すことができる。ここでRDSONはオン抵抗、QGはゲート電荷である。

- FOM=RDSON×QG

ゲート電荷は一般的に、ダイ内部の電流パスの面積と関係があり、通常、オン抵抗とは反比例する。

一般に、シリコンデバイス構造の改善によってMOSFETの性能を高めるには、オン抵抗かゲート電荷のいずれかを犠牲にする必要がある。MOSFETメーカーは、用途に応じて、オン抵抗を最小化するか、あるいはゲート電荷を抑えてスイッチング速度を高めるか、どちらかを選んでデバイスを設計する。

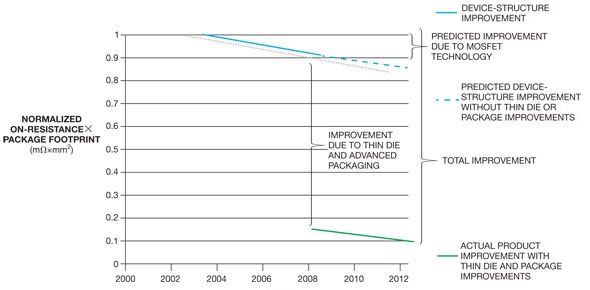

しかし、ウエハーの薄化とダイボンディング技術の進歩によって、オン抵抗と寄生インダクタンスをゲート電荷に影響を与えることなく改善できるようになった。このように、パッケージ技術の進歩は性能の改善に大きく寄与している。新しいデバイス構造を開発するよりも効果的だ(図2)。

図2 パワーMOSFETの性能を改善するには 最近(2008年)までシリコンデバイスの構造の進歩が、パワーMOSFETの性能向上を支えてきた。しかし現在では、ウエハーの薄化や新しいパッケージ技術といった、アセンブリプロセスの進歩が性能の向上をけん引している。縦軸はオン抵抗とパッケージ面積の積(mΩ×mm2)を正規化した値、横軸は西暦。デバイス構造の改善による性能向上(青色の実線)と、薄いダイやパッケージの改善による性能向上(緑色の実線)の間に劇的な改善が見て取れる。デバイス構造による改善だけでは、性能向上の予測値(青色の点線)は、緑色の実線に到達できそうもない。出典:Fairchild Semiconductor

図2 パワーMOSFETの性能を改善するには 最近(2008年)までシリコンデバイスの構造の進歩が、パワーMOSFETの性能向上を支えてきた。しかし現在では、ウエハーの薄化や新しいパッケージ技術といった、アセンブリプロセスの進歩が性能の向上をけん引している。縦軸はオン抵抗とパッケージ面積の積(mΩ×mm2)を正規化した値、横軸は西暦。デバイス構造の改善による性能向上(青色の実線)と、薄いダイやパッケージの改善による性能向上(緑色の実線)の間に劇的な改善が見て取れる。デバイス構造による改善だけでは、性能向上の予測値(青色の点線)は、緑色の実線に到達できそうもない。出典:Fairchild SemiconductorCopyright © ITmedia, Inc. All Rights Reserved.

パワーMOSFET

パワーMOSFET