ラッチアップって何?:Q&Aで学ぶマイコン講座(4)(2/3 ページ)

サイリスタ構造の説明

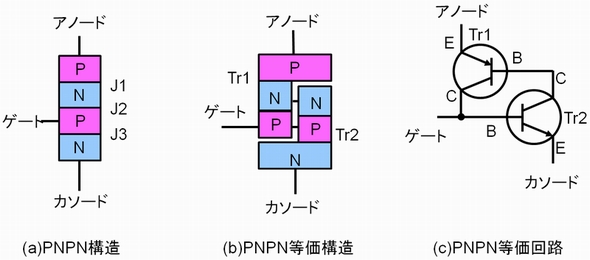

図2-aにサイリスタ(PNPN)構造を示します。アノードに正電位、カソードに負電位を印加しても、J1とJ3は順方向ですが、J2は逆方向なので、アノードからカソードへ電流は流れません。

しかし、ゲートに電圧を印加して電流を流すと、J2の逆方向電流がゲート電流によって加速され、J2に電流が流れるようになります。J1とJ3はもともと順方向ですから、この現象が発生すると、アノードからカソードに電流が流れ始めます。

一度、電流が流れ始めると、アノードの電源を切らない限り電流は流れ続けます。

これがサイリスタのスイッチング動作です。この動作を利用して、サイリスタは電力用機器でスイッチング素子として使われます。

PNPN接合は図2-bのようにPNP型トランジスタとNPN型の結合と考えられます。回路図にすると図2-cのような2つのトランジスタの構成になります。

Tr1のエミッタ(E)がサイリスタのアノードになります。ベースは、Tr1のコレクタ(C)(Tr2のベース(B))になります。カソードは、Tr2のエミッタ(E)になります。

ラッチアップ発生のメカニズム

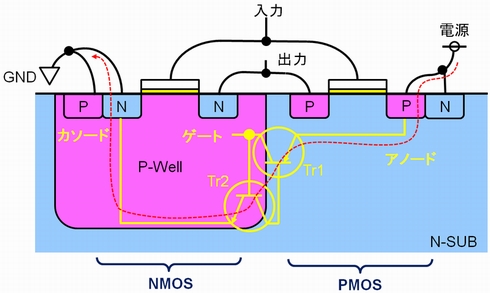

この2つのトランジスタをマイコンの中のCMOSに当てはめると図3のようになります。

図3の例はN-SUBの場合です。この他にP-SUBの場合がありますが、どちらの場合も寄生PNPN接合が形成されますので、ラッチアップの原理は同じように考えることができます。

電源につながっているPMOSのソースのPchからN-SUB、そしてP-WELLと続く経路でTr1が形成されます。そして、N-SUBからP-WELL、そしてGNDにつながっているNMOSのソースのNchの経路でTr2が形成されます。

Tr1とTr2は図3のCMOSの中で、黄線で描かれた様に形成されていることになります。電源側がアノード、GND側がカソード、そしてゲートはNMOSのP-WELLに相当します。

CMOSの入力ラインはNMOSのゲートにつながっています。ゲートとP-WELLはゲート酸化膜をはさんでコンデンサと同じ構造を形成しています。コンデンサは高周波信号を通しやすいので、万が一、入力ラインにノイズが入り、そのノイズのdV/dtが大きい(高周波成分が大きい)と、ゲート酸化膜を通り抜けてP-WELLに到達します。すると、これがトリガーとなってPNPN接合がONして、電源からGNDにかけて大電流が流れることになります。

また、電源ラインが急峻に変動した場合、特にマイナス側に変動した場合、ゲート電圧が電源電圧よりも高くなり、ゲートにノイズが入ったのと同じ状態になります。マイコンの電源が確立する前に端子に電圧を印加すると、この状態になります。

マイコンの内部にはPNPN接合は無限にありますので、どこのPNPN接合でラッチアップが発生するか分かりません。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 サイリスタ構造

図2 サイリスタ構造