過電流/過電圧保護用のブレーカー回路:Design Ideas アナログ機能回路(2/3 ページ)

設定された許容値を超えると……

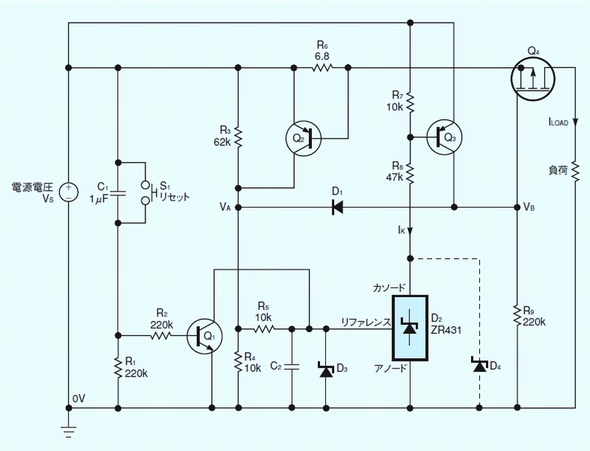

一方、ILOADが、設定された許容値を超えて過剰に流れると、電流検出抵抗R6での電圧降下(すなわちトランジスタQ2のVBE)が増大し、Q2はオンになる。その結果、VBの電圧が電源電圧VS側に引かれて上昇し、D2の出力トランジスタがオンになる。それにより、D2のカソード端子電圧が約2Vに低下する。

それに伴い、D2の出力トランジスタが抵抗R7とR8を経由する電流IKを引き込み、その電流によってトランジスタQ3のベース電流が流れてQ3がオンする。これにより、出力MOSFETであるQ4のゲート電圧VBがQ3を介して電源電圧と等しくなる。その結果、Q4がオフする。同時に、Q3とダイオードD1を経由して抵抗R4に電流が流れ、その結果、VAが電源電圧VSからD1による電圧降下分だけ低い値になる。

ここで、R6を流れる電流はゼロになり、Q2はベース‐エミッタ間電圧VBEが0Vとなってオフするが、VAの値は十分に高い電圧でD2をオンに保持する。抵抗R6を適正な値にすることで、最大負荷電流におけるQ2のベース‐エミッタ間電圧VBEを0.5V以下にできる。

過電圧保護動作

続いて、過電圧保護動作について説明する。この回路は、上記の過電流保護に加え、電源電圧が異常に高くなったときにもブレーカーとして機能する。負荷電流が正常な範囲にあるとQ2はオフし、電圧VAは電源電圧を抵抗R3、R4によって分圧された値になる。電源電圧が異常に高くなったときには、電圧VA(D2のレファレンス端子電圧)がD2内蔵の基準電圧VREFよりも高くなるため、D2の出力トランジスタがオンになる。これに対応してQ3がオンになり、次いでQ4がオフになって負荷は異常な高電圧から遮断される。

回路はいったんブレーカーとして動作すると、リセットされるまでその状態を保持する(リセットについては後述する)。ブレーカーとして動作した状態では、Q3がQ4のゲート‐ソース電圧をほぼ0Vに保持しているので、Q4自体もゲート‐ソース電圧が過電圧になることなく保護される。

R5による電圧降下は十分小さいので無視すると、D2のレファレンス端子電圧はVS×R4/(R3+R4)となる。レファレンス端子電圧が2.5VになったらD2の出力トランジスタがオンになるのを考慮すると、R3=[(VST/2.5)−1]×R4という関係式が得られる。

この式におけるVSTがブレーカー動作に移行する電源電圧レベル(トリップ電圧)である。例えば、R4を10kΩとし、トリップ電圧を18Vにしたい場合には、R3を62kΩにすればよい。このようにして、トリップ電圧が所望の値となるようにR3とR4の値を決定することになるが、その際には、両抵抗を流れる電流が過剰にならないよう十分大きい値にする必要がある。その一方で、これらの抵抗の値はレファレンス端子を流れる電流による誤差が問題にならない程度に小さくしなければならない。

Copyright © ITmedia, Inc. All Rights Reserved.