パッケージ技術の進化を迎え撃つ、LSIとパッケージの協調設計(2/2 ページ)

ツールの進化

EDAベンダーは、LSIとパッケージの協調設計を2つの方向から実現しようとしている。LSI最適化ツールによるアップストリームと、プリント基板システムツールによるダウンストリームだ。LSI設計とパッケージ設計の統合化に向けた業界の最初の取り組みは、I/Oピン割り当てソフトウエアをLSI実装ツールに統合するというLSI中心のアプローチだった。この方法により、スプレッドシートを使って手作業で割り当てを決めなくても済むようになった、とAllegroグループSIP製品マーケティンググループ担当ディレクターのKeith Felton氏はいう。「SERDES(シリアライザ/デシリアライザ)のような高速信号を使う設計でないといけない。誰だってパッケージ内で修正できないようなスキューをチップに残したくないだろう」(Felton氏)。

Cadence社、Synopsys社、Magma社が数年前から提供しているLSIフロアプランツールにはI/Oピン割り当て機能があるが、従来のフロアプランツールはパッケージの基本的な面しか捉えていないため完璧とはいえないとFelton氏は指摘する。

EDAベンダーはプリント基板側からもこの問題に取り組んでいる。1990年代半ば、Cadence社はパッケージ設計者向けのプリント基板設計ツールを開発した。この「Advance Package Designer」というツールと、その直後に米Avanti社(その後Synopsys社が買収)から発売されたツールにより、パッケージ設計者も回路の設計・分析ができるようになった。これらのツールにはパッケージ用の回路図入力・レイアウト機能と自動配線機能があったが、それをLSI設計にリンクさせたり、シミュレーションや解析に結びつける手段がなかった。Cadence社のほか、ここ3年で台頭してきた主要ベンダーは、LSIとパッケージの協調設計技術でさらに大きく前進してきている。

新しい流れ

Optimal Corp社のCTOを務めるAn-Yu Kuo氏は、LSI/パッケージ協調設計ツールの開発に向けたEDA業界の取り組みが加速したのは、台湾TSMC社がReference Flow 5.0を発表したことによってLSI/パッケージ協調設計フローの必要性が浮き彫りになった2004年のことだという*1)。「確かに今日でも完全に統合された協調設計ツールは存在しないが、昔はLSIとパッケージの設計はまったく別物だった。3年前、TSMC社が半導体製造フローにおけるLSIとパッケージの協調設計の重要性を認識し、業界がそれに追随した。以来、EDA業界は大きく前進したが、まだまだ先は遠い」(Kuo氏)。

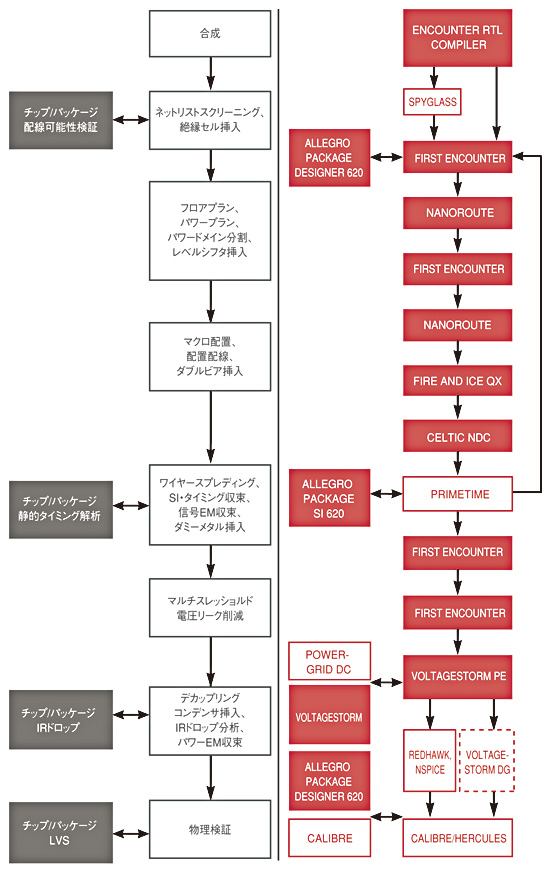

ばらばらだった断片を最初に1つのフローにまとめたのは、すでに市場に多くの主要ツールを提供していたCadence社だった(図1)。そして、パッケージ設計ツールベンダーの大半は、このCadenceのパッケージ設計フローに自社のツールを合わせた。1年前、Cadence社はパッケージ/プリント基板の協調設計機能を備えた「Allegro Package SI(signal-integrity)620」をリリースした。このツールは、Optimal Corp社の3Dフィールドソルバー・エンジンをAllegro Package SIシミュレータに搭載したものだ。620は、Allegro Package Designerで作成・設計されたパッケージ設計のほか、Allegroプリント基板レイアウトツールで作成されたプリント基板設計の読み出し/書き込みを行う。このツールを使用すれば基板のレイアウトと電気的効果の妥協点を探ることができる。「ユーザーがチップからプリント基板にいたるまでの電気経路を分析して、最終マスクまでにパッケージサブストレートとプリント基板、両方の最適化を目指した」とFelton氏は語る。

Synoposys社も負けていない。同社は2001年に行なったAvanti社の買収で「Xynetix」パッケージ設計ツールを手に入れ、2005年9月には設計フローを自動化する「JupiterIO」を発売した。このツールは、チップ/パッケージ間のI/Oを同時に設計できるツールで、I/Oとバンプの配置、RDL(redistribution layer)配線、パッケージ/ルートプランニングなどの機能を備えている。LSIデータにはMilkywayデータベースから、パッケージデータには標準インターフェースからアクセスする。

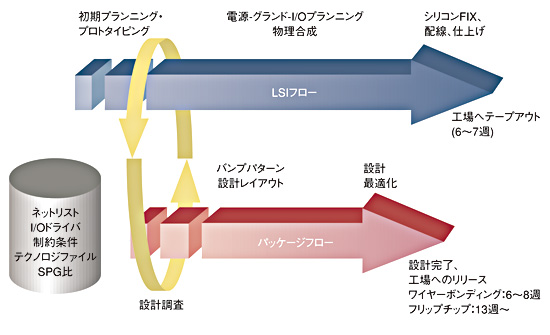

LSI/パッケージ協調設計ツールの市場に新たに参入する企業さえ出てきた。この記事が出る頃には、Cadence社とMagma社の両社が出資しているRio Design Automation社が「RioMagic」をリリースしているだろう。JupiterIOと同様、このツールでもLSIとパッケージの同時設計が可能だ(図2)。同社のCEOを務めるKaushik Sheth氏は、このツールによってLSI設計者は「パッケージに配慮しながら」自らの設計を調整することができ、ボードやパッケージの変更が必要になれば、LSI設計にすぐ変更を反映できるという。RioMagicのフローを使用すれば、設計者はLSIフロアプランニングステージで1つのI/Oデータモデルからビルドを開始して、フローの残りの部分には米Si2社の「Open Access」からアクセスできる。

Rio社のマーケティング部門副社長、Joel McGrath氏は、RioMagicによってI/O信号の信号品質と、チップパッケージの電源品質を解析できるという。この解析により、RioMagicはオンチップとパッケージの寄生パラメータを捉えた電気的モデルを作成する。このモデルのオンチップ部分を作成するために、RioMagicはオンチップのインターコネクトを事前に特定して、これをルックアップテーブルに格納する。

電気的モデルのパッケージ部分に対しては、RLCとKを抽出して、パッケージの詳細なPEEC(partial equivalent electrical circuit)モデルを作成する。このPEECモデルにより、フィールドソルバーにコストをかけることなくパッケージ全体を捉えることができる。またこのツールは、一次ドライバ、ネット用ドライバ、ネット寄生ネットワーク、各ネットに対応するプリント基板の負荷終端で構成されるシミュレーションデッキを生成する。

RioMagicには合成エンジンが搭載されているため、このモデルを使用してI/Oを割り当てた後にすぐ、それがLSIフロアプランに影響するかどうかを検証できる。I/Oが固定されているハードコアをフロアプラン内で移動させると、RioMagicは残りのI/Oをそのモデルに合わせて自動的に再合成する。

RioMagicは標準フォーマットに対応している。チップネットリストデータにはDEF(design exchange format)、I/OにはIP(intellectual property)ライブラリ、標準セルとハードマクロにはLEF(layout exchange format)、I/OドライバモデルにはIBIS(I/O buffer information specification)が使用されている。

SIPやアナログ/デジタル混載回路、高速RF回路などの高度な設計には、より詳細な抽出、EM解析、熱解析、シミュレーションが必要だ。SIPにアンテナを組み込む試みさえある。幸いにも、Ansoft社、EEsof社、Cadence社、Synopsys社、Flomerics社、Optimal社といった主力ベンダーから、こうした最先端アプリケーションに対応したツールが提供されている。

たとえばSIPにはアナログLSIとデジタルLSIの両方が組み込まれることが多い。それも積み重ねるのではなく、シールディングの目的で隣同士に配置されるのが普通である。2個のLSIを搭載したSIPでは、設計者は寄生パラメータの抽出と信号・電源品質の分析を、チップとパッケージの両方で個別に行ってから、システム全体としてSIPを分析しなくてはならない。

チップがワイヤーボンディングで積み重ねされていたり、デジタルブロックの干渉を受けやすい高速信号を使うRFブロックが組み込まれていれば、この分析はさらに難しくなる。抽出されるデータは手に負えないほど膨大な量となるため、モデルベースの手法を使わざるを得ない。

EEsof社とAnsoft社は、2Dプレイナーと3D EMシミュレータを提供している。一般にRFツールの進化は非常にゆっくりとしたものだが、Ansoftは最近「Nexxim」という回路シミュレータを発売した。マサチューセッツ工科大学のJacob White教授が開発したこのツールは、同社のフラッグシップ製品であるHFSS(high frequency structured simulator)を補完するものだ。Ansoft社のマーケティングディレクター、Larry Williams氏は、多数のランタイムを提供するこのツールは、複数のモデルが混在するLSI、パッケージ、プリント基板の設計に役立つという。このツールを使えば、設計者はネットリストとデバイスモデルごとに異なるシミュレータを実行したことで生じる分析結果の差を調整する必要がない。

「設計エンジニアが使える電磁気のモデルを作成するのには常に苦労してきた。しかし、回路シミュレータでそのモデルを使って何をするだろうか。たとえば、従来のオンチップの寄生エクストラクタを使えば回路シミュレータを速く実行できる。大半の人が速いSpiceシミュレータを使うべきと言うが、アクティブデバイスに関してはオーバースペックなことが多い。必要なのはより性能の高い回路シミュレータだ。だから我々はNexximを開発した」(Williams氏)。

Ansoft社は、ピン数の多いBGAパッケージ向けに境界要素法を採用したパッケージモデリングツール「Turbo Package Analyzer」も提供している。Agilent社のEEsofグループも、最新の3DプレイナーEMツール「Momentum」を提供している。同社は最近、フィールドソルバーによる容量不足の問題に対処するため、このツールの64ビット版をリリースした。

TSMC社が90nm設計向けのReference FlowでLSIとパッケージの協調設計を提案してくれたおかげで、EDA業界はLSI/パッケージ協調設計分野への取り組みに本腰を入れ始めつつある。ベンダーはそれぞれの戦略を進めつつあるが、この分野の課題すべてを達成するにはまだまだ時間がかかりそうだ。ほとんどのベンダーが認めているのは、SIPがさらに普及するようになればLSI集積のニーズが増え、EDAベンダーにSIP設計のサブフローを開発するチャンスが巡ってくるということだ。しかし、LSI設計グループ、パッケージ設計グループ、システム設計グループのうち、どのグループがSIPを担当するようになるのかはまだ分からない。おそらく、新しい特別な設計チームあるいは設計者を必要とするほどにSIPの設計は複雑になっていくと思われる。今後の動向を見守っていきたい。

脚注

※1…http://www.tsmc.com/tsmcdotcom/PRListingNewsAction.do?action=detail&LANG=E&newsid=1521&newsdate=2004/07/15.

Copyright © ITmedia, Inc. All Rights Reserved.

図1 パッケージ/プリント基板/LSI設計ツールの先駆者でもあるCadence社は、TSMCが提案したLSI/パッケージ協調設計ツールフローに対応したツールを提供している。

図1 パッケージ/プリント基板/LSI設計ツールの先駆者でもあるCadence社は、TSMCが提案したLSI/パッケージ協調設計ツールフローに対応したツールを提供している。  図2 Rio Design AutomationのRioMagicは、同じモデルを使ってLSIとパッケージを同時に設計できる。

図2 Rio Design AutomationのRioMagicは、同じモデルを使ってLSIとパッケージを同時に設計できる。