高速シリアルバスをサージから守る:3つの策で「難敵」をシャットアウト!(2/4 ページ)

【対策2】侵入者への攻撃 印加されたサージを減衰させる

筐体が導電性であっても、サージが漏れ込む可能性はある。この漏れ込み現象には明確に把握し難い性質があり、そのことが多段の防御作戦を要する理由となっている。

第2の対策の目標は侵入したサージを減衰させることだ。これは、第1関門を破って侵入した敵を消耗させることに当たる。この対策は、城の外門と第2の門の間に、敵をせん滅するための空間を配置することに例えることができる。城の防御においては、これら門の間は両側を壁で囲った狭い通路とし、そこを通過しようとする敵を両側の壁に開けた小窓から弓矢で攻撃すればよい。第1の城門(ファラデーケージ)を通過した敵が第2の門まで到達するには、このような仕掛けを施した空間を通過する必要がある。電子機器の対策はこのようなドラマチックなものではないが、目標とすることは同じようなものとなる。半導体デバイスに到達するサージが最小になるよう、可能な限り減衰させることである。

IEEE 1394やUSB、あるいはケーブル接続型のPCIeの場合、DC電源の供給用の電源パスとリターンパスにペアのケーブルが使用される。これらのラインに減衰特性の優れたフィルタを挿入すると、サージに対する防御になる。ちなみに、そのフィルタの特性を少し変更すれば、EMIの対策とすることも可能だ。

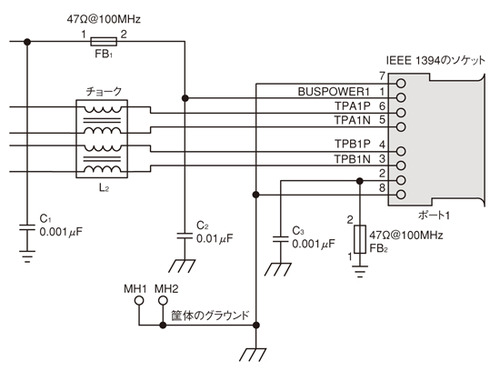

コネクタシェルと筐体をバネ構造によって導通させたと仮定し、電源ラインをどのようにすればよいか検討してみる(図1)。高周波のサージに対しては、電源パス/リターンパスと筐体グラウンドとの間のコネクタに極力近い位置にコンデンサC2、C3を挿入する。IEC(International Electrotechnical Commission:国際電気標準会議)で規定されたESD試験(放電容量として150pFのコンデンサを使用)のことを考慮すると、コンデンサCを介して電圧が印加される場合、トータルの電荷Qを一定に保つとすれば、コンデンサCにかかる電圧Vを定格電圧である50V以下に低減するためには、約0.033μFの保護用コンデンサが必要となる(Q=CVの関係より)。図ではC2を0.01μFとしたが、この場合、2kVまでの入力電圧に対して定格電圧以下に保つことができる。保護用コンデンサは、耐圧が十分なものにするとともに、ツェナーダイオードなどにより印加電圧をクランプして保護するか、またはTVS(transient voltage suppressor:トランジェント電圧サプレッサ)を代替で使用するかしなければならない。この保護コンデンサは、電源ラインとグラウンドラインに接続するものなので、容量が大きくても特に問題はない。

図1では比較的小さい値のコンデンサを使用しているが、実際にはもう少し大きい値が望ましい。コンデンサC2、C3は、低インピーダンスのパスによりサージを筐体グラウンドに逃がす役割を果たす。このコンデンサではサージのすべてを吸収することはできないが、効果は十分にある。コンデンサC2(あるいはC3)のインピーダンスによってそのパスに逃げるサージの量が決まり、その結果として、フェライトビーズFB1(あるいはFB2)に逃げるサージの量が決まる。フェライトビーズは高周波の信号に対しては抵抗成分が増加する。言い換えれば、高周波になると、フェライトビーズはコンデンサよりも高インピーダンスになる。サージのエッジに含まれる高周波成分は、障害の主たる原因である。コンデンサとフェライトビーズを組み合わせて使用することにより、高周波成分を減衰させ、サージのエッジの影響を緩和することが可能になる。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 IEEE1394シリアルバスにおけるサージ対策の例 コンデンサ、フェライトビーズの適切な配置、筐体へのコネクタの適切な組み込みなどにより、サージ耐性を強化することができる。

図1 IEEE1394シリアルバスにおけるサージ対策の例 コンデンサ、フェライトビーズの適切な配置、筐体へのコネクタの適切な組み込みなどにより、サージ耐性を強化することができる。