携帯電話機向けSERDESの設計(5/5 ページ)

次なる課題

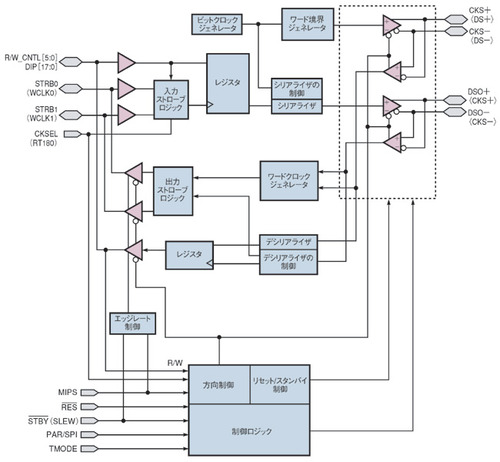

われわれは最初のプロジェクトと並行して、次世代製品の仕様策定も開始した。次世代製品では最初の設計概念を改良することに加え、最初のプロジェクトよりもかなり短期間で開発することが必要であった。最近発表された第2世代のμSerDesであるULP(ultra low power:超低消費電力)チップでは、パラレルクロッキングとシリアルクロッキングを分離し、さらなる消費電力の削減が図られている(図3)。

ULPチップでは、パラレルデータストリームとシリアルデータストリームの同期をとる必要がないため、2つ目のPLLを削除した。すべてのPLLを削除することが、第1世代製品のときからの目標であった。シリアルストリームのクロックは内部生成クロックのみで提供可能であることが分かった。これにより、消費電力は大きく低減され、システムクロックを必要としないマイクロコントローラインターフェースを提供することができる。

2つ目のPLLの削除は、非常に効果的であった。さらに都合の良いことに、クロックが常に仕様上の最大周波数で動作可能であることが分かった。これにより、インターフェースを介してシリアルストリームをバースト転送することができ、μSerDesペアは、各転送サイクルの大部分を連続的に起動状態に保つことなく、“バーストスタンバイ”という擬似的な電源停止状態にすることができる。

動的電力は動作周波数に依存すると思われがちだが、それは正確ではない。実際には、一定時間当たりの信号のエッジ数に依存する。このアプリケーションでは転送するビット数、つまり一定時間当たりのエッジ数は一定であったため、速度を上げても動的電力は増加しなかった。逆に転送後のバーストスタンバイ状態により、静的電力は大幅に減少した。さらに連続動作しないマイクロコントローラに対しては、動作間のバーストスタンバイにより、平均消費電力が著しく低減した。

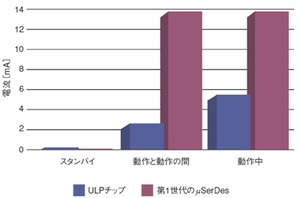

図4に、第1世代の24ビット品である「FIN24xx」とULPチップである24ビット品「FIN324」の消費電力の比較結果を示した。FIN24xxの消費電流は、5.44MHzクロックのピクセルインターフェースに対し、1ペア当たり約14mAである。一方、FIN324の消費電流は、それと同じ条件で約6mAに削減されている。ここで、マイクロコントローラインターフェースについては、稼働時間の割合を仮定する必要がある。マイクロコントローラの稼働率を約30%とするのが、現実的な見積もりである。この見積もりで、マイクロコントローラのサイクル周波数を同じく5.44MHzとすると、FIN324の消費電流は約3mAとなる。

このプロジェクトを通して、コンピュータ業界におけるSERDES設計に関する専門知識を、要求の異なる別の市場に適用することができることが分かった。しかしこれを実現するには、詳細な調査、顧客との対話、チップから最終的なシステムへと設計対象を移すという発想の転換が必要である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図4 消費電流の比較

図4 消費電流の比較