携帯電話機向けSERDESの設計(2/5 ページ)

最初の仕様

上述した情報を総合して、われわれは最初の製品仕様を完成させた。少なくとも、カメラと液晶ディスプレイについてはシリアル化された双方向通信が可能なチップが必要で、チップ当たりの消費電流は待機時で5μA未満、動作時で7mA未満、EMIは−120dBm未満である必要があった。もう1つ、携帯電話機市場における重要なポイントがあった。それは、そのチップを使用するエンジニアのほとんどはSERDESを扱ったことがないということである。そのため、チップをできる限り使いやすいものにすることも非常に重要な要件であった。

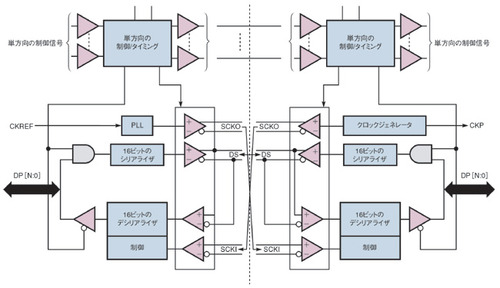

チップに要求される事柄は分かったので、われわれは図1のようなブロック図を考えた。これであれば、双方向通信が可能で、マイクロコントローラインターフェースやピクセルインターフェースに接続することができる。しかしながら、消費電力、EMI、マイクロコントローラの読み出し操作、パラレルクロックとシリアルクロックの分離など、いくつかの条件をどのようにして満たすのかという問題はまだ残っていた。例えば、EMIは−120dBmと、それまでのSERDES製品よりもかなり低くする必要があった。また、垂直同期、水平同期、ピクセルデータに対応する標準のピクセルインターフェースにも対応しなければならなかった。とはいえ、行うべき作業は明白であり、これまでのSERDESにおけるそれと似たものになると考えていた。

この段階で、アプリケーションと顧客の要求に関するいくつかの重要な項目が明確になっていた。どの顧客も、ピクセルインターフェースとマイクロコントローラインターフェースの両方を要求しており、それらはプラットフォームの要求によって異なっていた。ベースバンドプロセッサが液晶ディスプレイに対するマイクロコントローラインターフェースを備えている必要があるケースもあれば、ベースバンドプロセッサがより標準的なピクセルインターフェースを必要とする場合もあった。ほとんどすべてのシステムメーカーが複数のサプライヤのプロセッサを使用していたため、どのメーカーも両方のインターフェースを必要とした。

このことから、両方のインターフェースを提供可能な単一のチップを提供できれば好都合であることが分かった。加えて、1つのチップにパラレルからシリアル、シリアルからパラレルに変換する機能が存在すべきだった。これが実現されれば、顧客は4〜6個ものチップを購入するのではなく、1つの製品を購入するだけで済む。チップは双方向のデータに対応し、マイクロコントローラ処理のためにシリアライザとデシリアライザの両方を搭載し、EMIを低減するためにシリアルI/Oを差動にすることが決定された。

われわれにとっての大きな課題の1つは、差動I/Oに関する部分であった。通常、差動I/Oの方式は電流モードと名付けられているのにもかかわらず、実際には電圧レベルレシーバを用いて構成されていた。このレシーバは、2つの信号間の電圧差によって「1」か「0」かを決定する。詳細に考察した結果、設計チームは電圧差ではなく、電流の向きを利用することにした。電流の向きは電圧レベルよりも安定しているので、1と0を区別するために必要となる電圧はかなり小さくて済む。実際、従来は少なくとも約250mVの電圧差が必要であったのに対し、新しい手法では50mVの電圧振幅で判定が可能となった。これであれば、駆動能力は従来の1/5でよいことになる。われわれは、この新しいI/O技術にCTL(current transfer logic)という名前を付けた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング