幕開け迫る「45nm時代」:この最新プロセスノードに設計者はどう備えるべきなのか?(2/3 ページ)

最重要課題はリーク対策

「大きな変化はなし」と言いつつも、ファウンドリ、EDAベンダー、設計チームは、45nmプロセスの設計では、大きく以下の3つが課題になるとしている。

- 低消費電力設計を必ず採用しなければならない

- DFMに対応したツール/手法を採用しなければならない

- RDRや確率解析を従来以上に導入しなければならない

65nmノードでもそうであったように、ファウンドリの最初の45nmプロセスは、高性能化よりも低消費電力化を目的としたものとなる。また、ファウンドリは、High-kのような新材料を採用して大勝負に出るよりも、劇的な変更を避ける方法を選択する傾向にある。そのため、45nmノードにおいても引き続きリークが最大の問題であり続ける。

65nmノードでは、ダイナミック、スタティック(スタンバイ)時のリーク電力が、チップの全消費電力の約40%を占める。そのため、ターゲットとするアプリケーションの種類によらず、チップの設計者は低消費電力設計を採用せざるを得なかった*3)。そして、45nmノードではリーク電力が全消費電力の60〜65%にも上り、問題はさらに大きくなる。

ファウンドリによれば、このリーク電力の存在から、45nmノードでは低消費電力設計の適用は必須になるという。Chartered社のNg氏は、「例えば、電圧アイランドの考え方が非常に多く活用されるようになってきた。われわれの顧客らは、単にブロックごとの供給電圧の違いに対応するためだけに電圧アイランドを採用しているわけではない。それらグループ全体の電源を未使用時には遮断するために利用している。このような徹底的な電力管理手法が、ますます多く見られるようになってきている」と述べる。

米Freescale Semiconductor社のCMOS技術担当バイスプレジデントであるGregg Bartlett氏によると、「当社のネットワークグループとワイヤレスグループは、すでに45nmノードでの設計に携わっている。両者とも、低消費電力設計を採用している」という。同氏は、「65nmと45nmのノードには、本質的な大きな差異はないと考えている。電力管理手法としては、これまでいくつかのプロセスノードに対し、DVFS(dynamic voltage frequency scaling:動的電圧周波数スケーリング)やゲートの状態保持(データリテンション)、パワーゲーティングなどの電力低減手法を適用してきた。つまり、45nmノードでこれらを初めて採用するわけではないが、45nmノードではこれまで以上に多用することになる」と述べる。「いくつかのプロセスノードで低消費電力設計を適用してきた当社ワイヤレスグループは、45nmの設計フローでは、高度な電力モデリングに従来以上に時間をかけている」(同氏)という。

また、Bartlett氏は「当社ワイヤレスグループは熱モデリング手法も採用し始めている」と付け加えた。「そのための手法やそれに対応するツールはまだ広まっていないが、チップ内における高温の個所ならびに熱変化点を特定し、どこで電力が消費されているのかを知ることが重要だと考えている」(同氏)という。

こうしたバルクCMOSプロセスにかかわる動きの一方で、Freescale社は最近の数世代のチップセットでIBM社のSOI(silicon on insulator)プロセスを利用している。Bartlett氏は、「われわれは各種プロセスの評価を常に行っている。その中でも、SOIはこれまで素晴らしい結果を出している。SOIプロセスでは、バルクCMOSプロセスと比較して、消費電力と性能の両方で2桁の改善が見られた」と述べる。

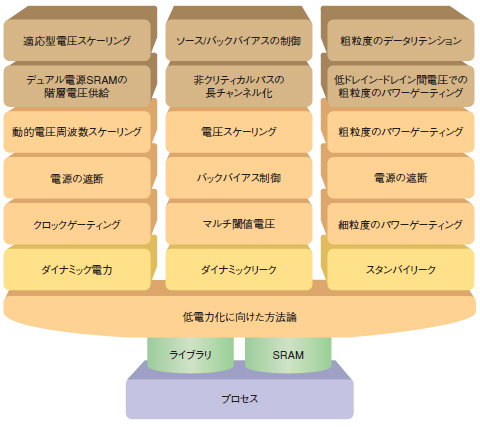

バルクCMOSプロセスを提供するファウンドリは、新しいUltra Low-kプロセスにおいて、電力を管理するためにかなりの労力を費やしている。また、EDAベンダーとも密接に協力し、顧客向けに45nmプロセスでの電力管理を支援するツールを提供している。例えば、TSMC社は同社のリファレンスフロー8.0に「推奨する高度な低消費電力化手法」を追加し、顧客がさらに電力を低減できるようにしている(図2)。同社は、電力管理のために、以下のような手法を推奨している。

- ダイナミック電力を低減するために、デュアル電源のSRAMブロックに高度な電圧スケーリングと階層的な電圧供給を適用する

- ダイナミック電力を低減するために、ソースバイアスおよびバックバイアスを制御する

- ダイナミック時のリーク電力を低減するために、非クリティカルパスには長いチャンネルを使用する

- スタンバイ時のリーク電力を低減するために、ドレイン‐ドレイン間電圧を低くし、粗粒度のデータリテンションとパワーゲーティングを適用する

TSMC社のQuan氏は、「こうした手法のほとんどは、未使用ブロックに対するクロックゲーディングや電源の遮断に関するものだ。顧客が45nmノードでの設計に適用できるさまざまな手法を用意している」と述べる。

低消費電力化のためのツールも、顧客向けに数多く販売されている。TSMC社、UMC社、CPTAは、各種ベンダーの電力管理ツール/低消費電力化ツールを認可している。米Cadence Design Systems社、米Magma Design Automation社、Synopsys社は、いずれも低消費電力化ツールを開発している。また、リーク電力が比較的少ない65nm/45nmプロセスをターゲットにしたIC設計の増加に伴い、その部分でのシェアを獲得するために、要求されるすべての事柄を網羅した低消費電力設計フローを構築することに力を注いでいる。

ファウンドリは、自社プロセスを顧客に採用してもらうためにEDA企業を自社陣営に取り込もうとしている。TSMC社はリファレンスフロー8.0向けに、Cadence社が支持するCPF(Common Power Format)の検証を行った。同フォーマットは、電力に関する回路仕様や制約条件を記述するためのもので、Si2(Silicon Integration Initiative)が普及を図っている。これを利用することにより、設計フローの各所で使用するツールが、電力に関する単一の記述を基に稼働することが可能となる。Quan氏によると、「一方で、TSMC社は標準化団体AccelleraのUPF(Unified Power Format)グループとも共同で、同社の45nmプロセス向けにUPFフォーマットの検証を行っている」という。

DFMは「必須」に

ファウンドリは、65nmノードでも顧客に対してDFMツールの使用を推奨していたが、それを必須とはしていなかった*4)。それに対し、45nmノードでは、ファウンドリが定める3つの分野のうち、以下の2つでDFMツールの使用が必須となる見込みだ。

- LPC(lithography process check)

- CAA(critical area analysis)

これに対し、3つ目の分野であるCMP(chemical mechanical planarization)シミュレーションについては、DFMツールの使用を必須とはしていない(推奨はしている)。

Chartered社のNg氏は、「65nmノードではDFMツールを使用する顧客はまだあまり多くない。しかし、DFMを利用せずに45nmプロセスに対応するのは不可能だろう」と述べる。同氏によれば、Chartered社は65nmプロセスを利用してDFMツールの検証を行った。それを通して、「DFMの問題点やツールの要件がやっと分かってきたところだ。これにより、45nmノードでは何が本当に必要なのかをさらに適切に把握することができる」(同氏)としている。

現在、ほとんどの大手EDAベンダーは、各種DFMツールの使用を必須とし、それらを1つの技術体系として統合しようとしている。2006年には多くのEDAベンダーが、自社開発ないしはDFMツールを開発していた企業との合併や買収により、ツール群をそろえた。EDAベンダーの多くは、ユーザーがDFMツールを使っていることを意識せずに利用できるよう、DFMの技術をツールに盛り込むことに注力している。大手ファウンドリは、この目的が達成できるようEDAベンダーを支援している。EDAベンダーはDFM技術を自社のフローに統合し、完全なDFM対応とするか、Correct by Construction(構築しながら修正する)対応とするようにしている。この状況は、90nm/130nmプロセスの時代に配線ツールがDRC(design rules checking)対応になったときに似ている。

Magma社で設計実装ビジネスユニットのシニア製品ディレクタを務めるDwayne Burek氏によると、Correct by ConstructionなDFM、つまり同社が呼ぶところの「in the loop design verification」は必須であるという。45nmノードの大規模なレイアウトでは、増加し続けるDRC/LVS(layout vs. schematic)用デッキ/モデルに加えて、かなりの数のDFM用デッキ/モデルが必要になる。Burek氏によると、Magma社のプラットフォーム「Talus DFM」には、DRC、LPC、CMPシミュレーションを含むin the loop design verification機能が搭載されているという。Burek氏は、「これを利用することで、ICの実装フロー内で、各機能単体を直接的に用いるか、または統合された物理検証機能を利用する形でチェックを実施することができる」と述べる。

Magma社とCadence社のツールフローは、いずれもLPC、CAA、CMPシミュレーションを含んでいる。Cadence社は最近、同社のツールプラットフォーム「Encounter」にDFM対応機能を追加したことを発表している。また、2007年8月に米Clear Shape Technologies社を買収したことで、LPCツールとCAAツールを手に入れた。米Mentor Graphics社とSynopsys社のフローにもLPCツールとCAAツールが含まれているが、CMPについては両社ともファウンドリのCMPシミュレータを利用するようにしている。

TSMC社とUMC社は、これまで両社の新しいプロセス上で自社のツールを検証したいと考えるすべてのEDAベンダーと共同で作業を行ってきた。TSMC社は、大手ツールベンダーのフローと、多くの未上場企業のDFMツールを検証した。この検証を経て、TSMC社の製造データは各パートナ企業に提供されることになる(データは暗号化される)。Quan氏によると、このデータを提供することにより、ツールベンダーは自社の顧客に、TSMC社のDFM自動解決フローを容易に提供できるようになるという。

UMC社もリファレンスフローを用意するが、同社の企業マーケティング部門担当シニアディレクタであるMort Bamdad氏によると、「当社は、どのように設計すべきであるという指示は行わない」という。「45nmプロセスでも、基本的なフローはそれ以前とあまり変わらない。設計者にとって新しい機能が必要となるかもしれないが、新しいツールまでは必要とならないように、DFMにかかわる変更点をツールに実装するようEDAベンダーに伝えている」と同氏は述べる。

CPTAは、65nmノードの場合と同様に、各EDAベンダーが提供するDFMツールのうちのいくつかに対して、CPTAの3社の45nmノードに対応可能なものであるとの認定を行った。CAAについては、米Ponte Solutions社とMentor社製のツールを認定した。CMPシミュレーションについては、Cadence社が米Praesagus社の買収によって取得した「Cadence CMP Predictor」を認定している。ブロックレベルの詳細なLPCに関してはMentor社の「Calibre LFD」を認定し、チップレベルのLPCに関してはCadence社の「Cadence Litho Physical Analyzer」(オリジナルはClear Shape Technologies社の「InShape」)を認定している。Ng氏によると、CPTAは、リーク電力低減と歩留りの改善を目的とした米Blaze DFM社の「Blaze MO」と、デッキのチェックを目的としたMentor社の「Calibre Yield Analyzer」も推奨しているという。

脚注

※3…『低消費電力LSIの設計技術』(Michael Santarini、EDN Japan 2007年9月号、p.42).

※4…『変化するDFM市場』(Michael Santarini、EDN Japan 2006年11月号、p.46).

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

図2 TSMC社が提示する電力管理技術 電力管理は、45nmプロセスでの設計でも最優先事項のままである。TSMC社は、従来からの電力管理技術に対し、さらなる項目追加を行っている。

図2 TSMC社が提示する電力管理技術 電力管理は、45nmプロセスでの設計でも最優先事項のままである。TSMC社は、従来からの電力管理技術に対し、さらなる項目追加を行っている。